- 您现在的位置:买卖IC网 > PDF目录98044 > MSC8144E (FREESCALE SEMICONDUCTOR INC) 0-BIT, 150 MHz, OTHER DSP, PBGA783 PDF资料下载

参数资料

| 型号: | MSC8144E |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 数字信号处理 |

| 英文描述: | 0-BIT, 150 MHz, OTHER DSP, PBGA783 |

| 封装: | 29 X 29 MM, LEAD FREE, PLASTIC, FCPBGA-783 |

| 文件页数: | 62/80页 |

| 文件大小: | 2284K |

| 代理商: | MSC8144E |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页当前第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页

Hardware Design Considerations

MSC8144E Quad Core Digital Signal Processor Data Sheet, Rev. 0

Freescale Semiconductor

65

3

Hardware Design Considerations

The following sections discuss areas to consider when the MSC8144E device is designed into a system.

3.1

3.1.1

Power-on Sequence

Use the following guidelines for power-on sequencing:

There are no dependencies in power-on/power-off sequence between VDDM3 and VDD supplies.

There are no dependencies in power-on/power-off sequence between RapidIO supplies: VDDSXC, VDDSXP,

VDDRIOPLL and other MSC8144E supplies.

VDDPLL should be coupled with the VDD power rail with extremely low impedance path.

External voltage applied to any input line must not exceed the related to this port I/O supply by more than 0.6 V at any time,

including during power-up. Some designs require pull-up voltages applied to selected input lines during power-up for

configuration purposes. This is an acceptable exception to the rule during start-up. However, each such input can draw up to 80

mA per input pin per MSC8144E device in the system during start-up. An assertion of the inputs to the high voltage level before

power-up should be with slew rate less than 4V/ns.

The following supplies should rise before any other supplies in any sequence

VDD and VDDPLL coupled together

VDDM3

After the above supplies rise to 90% of their nominal value the following I/O supplies may rise in any sequence (see Figure 44):

VDDGE1

VDDGE2

VDDIO

VDDDDR and MVREF coupled one to another. MVREF should be either at same time or after VDDDDR.

VDDM3IO

V25M3

Note:

1.

This recommended power sequencing is different from the MSC8122/MSC8126.

2.

If no pins that require VDDGE1 as a reference supply are used (see Table 1), VDDGE1 can be tied to GND.

3.

If no pins that require VDDGE2 as a reference supply are used (see Table 1), VDDGE2 can be tied to GND.

4.

If the DDR interface is not used, VDDDDR and MVREF can be tied to GND.

5.

If the M3 memory is not used, VDDM3, VDDM3IO, and V25M3 can be tied to GND.

6.

If the RapidIO interface is not used, VDDSX, VDDSXP, and VDDRIOPLL can be tied to GND.

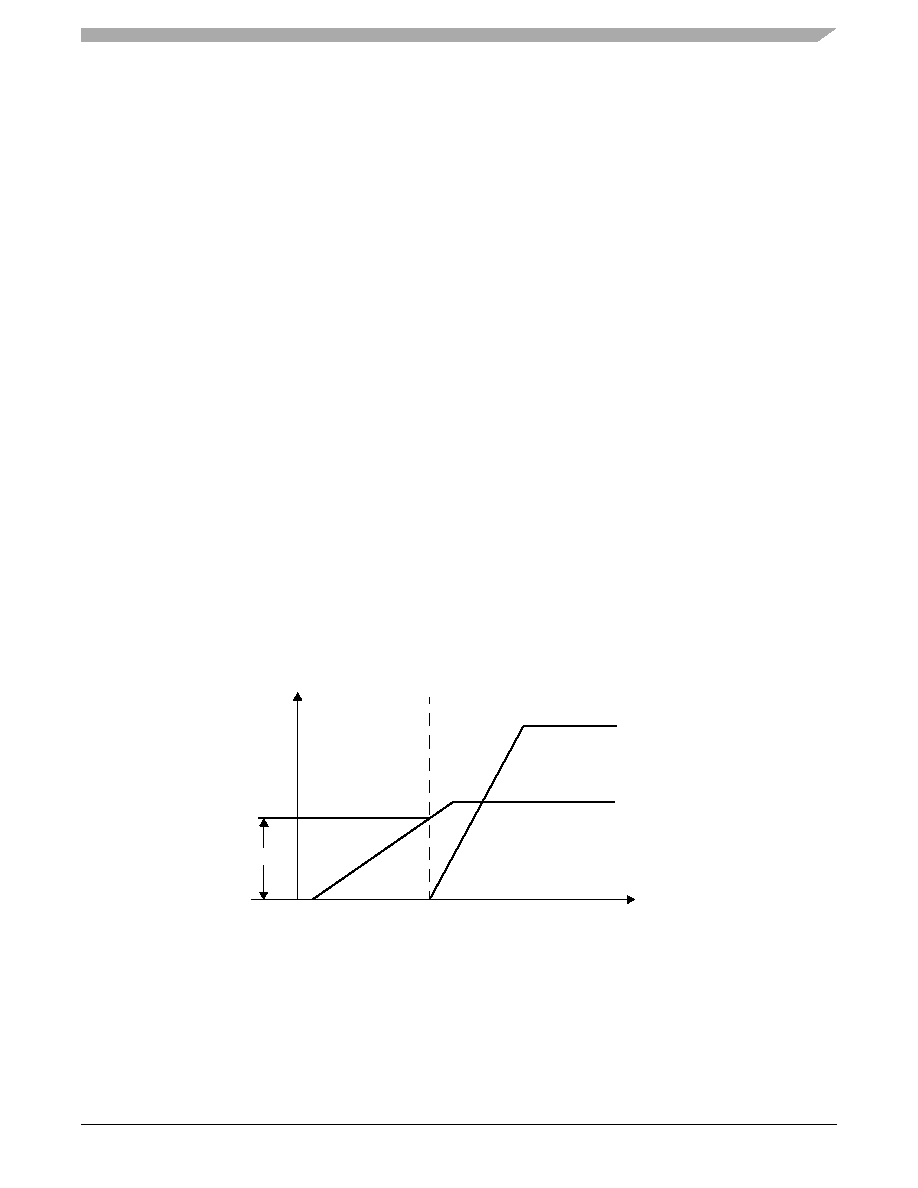

Figure 44. VDDM3, VDDM3IO and V25M3 Power-on Sequence

VDDM3, VDD, and VDDPLL

90%

I/O supplies

相关PDF资料 |

PDF描述 |

|---|---|

| MSC8152TVT1000B | RISC PROCESSOR, PBGA783 |

| MSC8154ETVT1000B | 0-BIT, OTHER DSP, PBGA783 |

| MSC8252TVT1000B | 0-BIT, OTHER DSP, PBGA783 |

| MSC8252SVT1000B | 0-BIT, OTHER DSP, PBGA783 |

| MSD1010LT3 | 100 mA, 15 V, PNP, Si, SMALL SIGNAL TRANSISTOR |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MSC8144EC | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Quad Core Digital Signal Processor |

| MSC8144ESVT1000B | 制造商:Freescale Semiconductor 功能描述:DSP 32-BIT 1GHZ 1000MIPS 783-PIN FCBGA BOX - Trays 制造商:Freescale Semiconductor 功能描述:ENCRYPTION PACSUN R2.1 783FCPBGA |

| MSC8144ESVT800A | 制造商:Freescale Semiconductor 功能描述:DSP 32BIT 800MHZ 800MIPS 783FCBGA - Trays |

| MSC8144ESVT800B | 制造商:Freescale Semiconductor 功能描述:DSP 32-BIT 800MHZ 800MIPS 783-PIN FCBGA EACH - Bulk 制造商:Freescale Semiconductor 功能描述:ENCRYPTION PACSUN R2.1 783FCPBGA |

| MSC8144ETVT1000A | 制造商:Freescale Semiconductor 功能描述:DSP 32-BIT 1GHZ 1000MIPS 783-PIN FCBGA - Bulk |

发布紧急采购,3分钟左右您将得到回复。