- 您现在的位置:买卖IC网 > PDF目录385639 > MT4C1M16E5DJ-6 (Micron Technology, Inc.) EDO DRAM PDF资料下载

参数资料

| 型号: | MT4C1M16E5DJ-6 |

| 厂商: | Micron Technology, Inc. |

| 英文描述: | EDO DRAM |

| 中文描述: | EDO公司的DRAM |

| 文件页数: | 3/24页 |

| 文件大小: | 385K |

| 代理商: | MT4C1M16E5DJ-6 |

3

1 Meg x 16 EDO DRAM

D52_B.p65 – Rev. B; Pub. 3/01

Micron Technology, Inc., reserves the right to change products or specifications without notice.

2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

V

IL

CASL#/CASH#

V

IL

RAS#

V

IL

ADDR

ROW

COLUMN (A)

DON‘T CARE

UNDEFINED

V

IL

WE#

V

IOL

OPEN

DQ

tWPZ

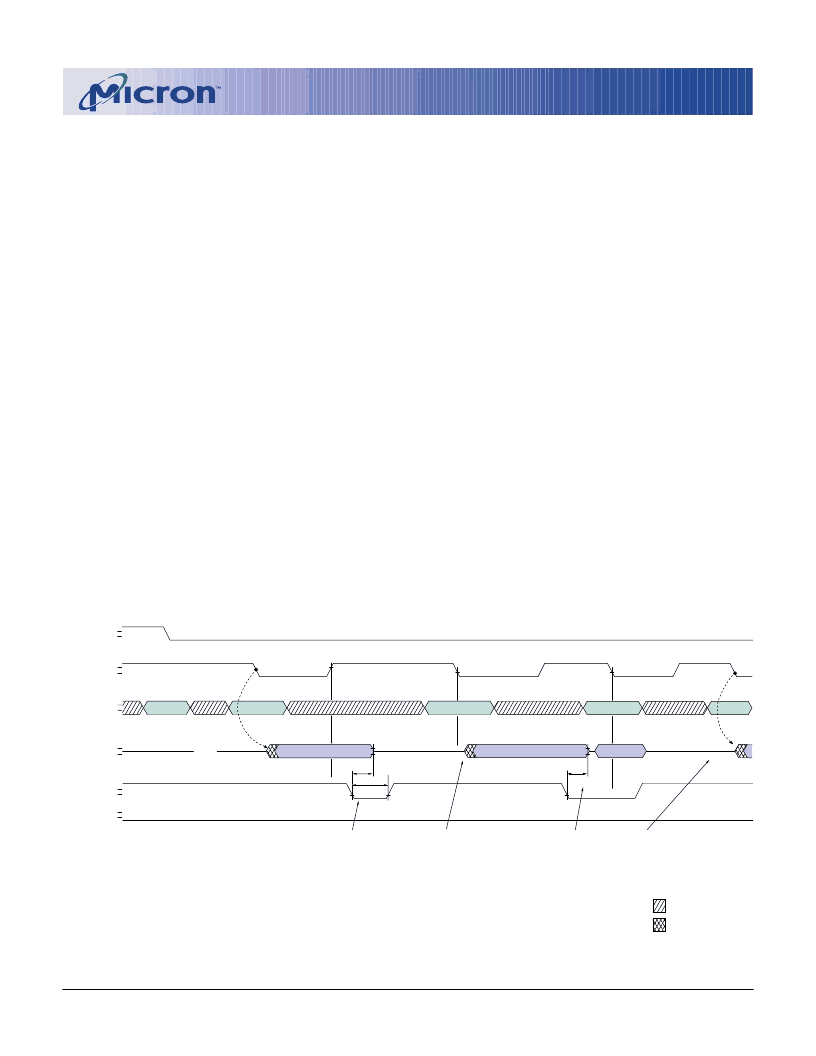

The DQs go to High-Z if WE# falls, and if

t

WPZ is met,

will remain High-Z until CAS# goes LOW with

WE# HIGH (i.e., until a READ cycle is initiated).

V

IL

OE#

VALID DATA (B)

tWHZ

WE# may be used to disable the DQs to prepare

for input data in an EARLY WRITE cycle. The DQs

will remain High-Z until CAS# goes LOW with

WE# HIGH (i.e., until a READ cycle is initiated).

tWHZ

COLUMN (D)

VALID DATA (A)

COLUMN (B)

COLUMN (C)

INPUT DATA (C)

Figure 2

WE# Control of DQs

PAGE ACCESS

Page operations allow faster data operations (READ,

WRITE or READ-MODIFY-WRITE) within a row-

address-defined page boundary. The page cycle is al-

ways initiated with a row address strobed in by RAS#,

followed by a column address strobed in by CAS#. Ad-

ditional columns may be accessed by providing valid

column addresses, strobing CAS# and holding RAS#

LOW, thus executing faster memory cycles. Returning

RAS# HIGH terminates the page mode of operation,

i.e., closes the page.

EDO PAGE MODE

The 1 Meg x 16 provides EDO PAGE MODE, which is

an accelerated FAST-PAGE-MODE cycle. The primary

advantage of EDO is the availability of data-out even

after CAS# returns HIGH. EDO provides for CAS#

precharge time (

t

CP) to occur without the output data

going invalid. This elimination of CAS# output control

provides for pipelined READs.

FAST-PAGE-MODE DRAMs have traditionally

turned the output buffers off (High-Z) with the rising

edge of CAS#. EDO-PAGE-MODE DRAMs operate like

FAST-PAGE-MODE DRAMs, except data will remain

valid or become valid after CAS# goes HIGH during

READs, provided RAS# and OE# are held LOW. If OE# is

pulsed while RAS# and CAS# are LOW, data will toggle

from valid data to High-Z and back to the same valid

data. If OE# is toggled or pulsed after CAS# goes HIGH

while RAS# remains LOW, data will transition to and

remain High-Z (refer to Figure 1). WE# can also perform

the function of disabling the output drivers under cer-

tain conditions, as shown in Figure 2.

During an application, if the DQ outputs are wire

OR’d, OE# must be used to disable idle banks of DRAMs.

Alternatively, pulsing WE# to the idle banks during

CAS# HIGH time will also High-Z the outputs. Inde-

pendent of OE# control, the outputs will disable after

t

OFF, which is referenced from the rising edge of RAS#

or CAS#, whichever occurs last.

BYTE ACCESS CYCLE

The BYTE WRITEs and BYTE READs are determined

by the use of CASL# and CASH#. Enabling CASL# se-

lects a lower BYTE access (DQ0-DQ7). Enabling CASH#

selects an upper BYTE access (DQ8-DQ15). Enabling

both CASL# and CASH# selects a WORD WRITE cycle.

The 1 Meg x 16 may be viewed as two 1 Meg x 8

DRAMs that have common input controls, with the ex-

ception of the CAS# inputs. Figure 3 illustrates the BYTE

WRITE and WORD WRITE cycles.

Additionally, both bytes must always be of the same

mode of operation if both bytes are active. A CAS#

precharge must be satisfied prior to changing modes of

operation between the upper and lower bytes. For ex-

ample, an EARLY WRITE on one byte and a LATE WRITE

on the other byte are not allowed during the same cycle.

相关PDF资料 |

PDF描述 |

|---|---|

| MT4LC1M16E5DJ-6S | EDO DRAM |

| MT4LC1M16E5 | EDO DRAM |

| MT4C4256 | 256K x 4 DRAM Standard Or Low Power, Extended Refresh(标准或低功率,扩展刷新,256K x 4动态RAM) |

| MT4C4256L | 256K x 4 DRAM Standard Or Low Power, Extended Refresh(标准或低功率,扩展刷新,256K x 4动态RAM) |

| MT4LC16M4T8TG-5 | DRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MT4C1M16E5TG-5 | 制造商:MICRON 制造商全称:Micron Technology 功能描述:EDO DRAM |

| MT4C1M16E5TG-6 | 制造商:MICRON 制造商全称:Micron Technology 功能描述:EDO DRAM |

| MT4C2M8B1DJ-6 | 制造商:Micron Technology Inc 功能描述: |

| MT4C2M8E7DW-6 | 制造商:Micron Technology Inc 功能描述:2M X 8 EDO DRAM, 60 ns, PDSO28 |

| MT4C40004 | 制造商:MICRON 制造商全称:Micron Technology 功能描述:4 MEG x 4 DRAM |

发布紧急采购,3分钟左右您将得到回复。