- 您现在的位置:买卖IC网 > PDF目录189449 > OR4E043BM416-DB (LATTICE SEMICONDUCTOR CORP) FPGA, 1296 CLBS, 380000 GATES, PBGA416 PDF资料下载

参数资料

| 型号: | OR4E043BM416-DB |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 1296 CLBS, 380000 GATES, PBGA416 |

| 封装: | PLASTIC, FBGA-416 |

| 文件页数: | 81/151页 |

| 文件大小: | 2680K |

| 代理商: | OR4E043BM416-DB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页当前第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页

Lattice Semiconductor

35

Data Sheet

September, 2002

ORCA Series 4 FPGAs

Programmable Input/Output Cells

(continued)

Inputs

There are many major options on the PIO inputs that

can be selected in the ORCA Foundry tools listed in

Table 14. Inputs may have a pull-up or pull-down resis-

tor selected on an input for signal stabilization and

power management. Input signals in a PIO are passed

to CIB routing and/or a fast route into the clock routing

system. A fast input from one PIO per PIC is also avail-

able to drive the edge clock network for fast I/O timing

to other nearby PIOs.

There is also a programmable delay available on the

input. When enabled, this delay affects the INFF and

INDD signals of each PIO, but not the clock input. The

delay allows any signal to have a guaranteed zero hold

time when input.

Inputs should have transition times of less than 100 ns

and should not be left oating. For full swing inputs, the

timing characterization is done for rise/fall times of

≥ 1 V/ns. If any pin is not used, it is 3-stated with an

internal pull-up resistor enabled automatically after

conguration. Floating inputs increase power con-

sumption, produce oscillations, and increase system

noise. The inputs in LVTTL, LVCMOS2, and

LVCMOS18 modes have a typical hysteresis of approx-

imately 250 mV to reduce sensitivity to input noise. The

PIC contains input circuitry which provides protection

against latch-up and electrostatic discharge.

The other features of the PIO inputs relate to the latch/

FF structure in the input path. In latch mode, the input

signal is fed to a latch that is clocked by either the pri-

mary, secondary, or edge clock signal. The clock may

be inverted or noninverted. There is also a local set/

reset signal to the latch. The senses of these signals

are also programmable as well as the capability to

enable or disable the global set/reset signal and select

the set/reset priority. The same control signals may

also be used to control the input latch/FF when it is

congured as a FF instead of a latch, with the addition

of another control signal used as a clock enable. The

PIOs are paired together and have independent CE,

Set/reset, and GSRN control signals per PIO pair.

There are two options for zero-hold input capture in the

PIO. If input delay mode is selected to delay the signal

from the input pin, data can be either registered or

latched with guaranteed zero-hold time in the PIO

using a global primary system clock. The fast zero-hold

mode of the PIO input takes advantage of a latch/FF

combination to latch the data quickly for zero-hold

using a fast edge clock before passing the data to the

FF which is clocked by a global primary system clock.

The combination of input register capability with non-

registered inputs provides for input signal demultiplex-

ing without any additional resources. The PIO input

signal is sent to both the input register and directly to

the unregistered input (INDD). The signal is latched

and output to routing at INFF. These signals may then

be registered or otherwise processed in the PLCs.

Every PIO input can also perform input double data

rate (DDR) functions with no PLC resources required.

This type of scheme is necessary for DDR applications

which require data to be clocked in from the I/O on both

edges of the clock. In this scheme the input of INFF

and INSH are captured on the positive and negative

edges of the clock.

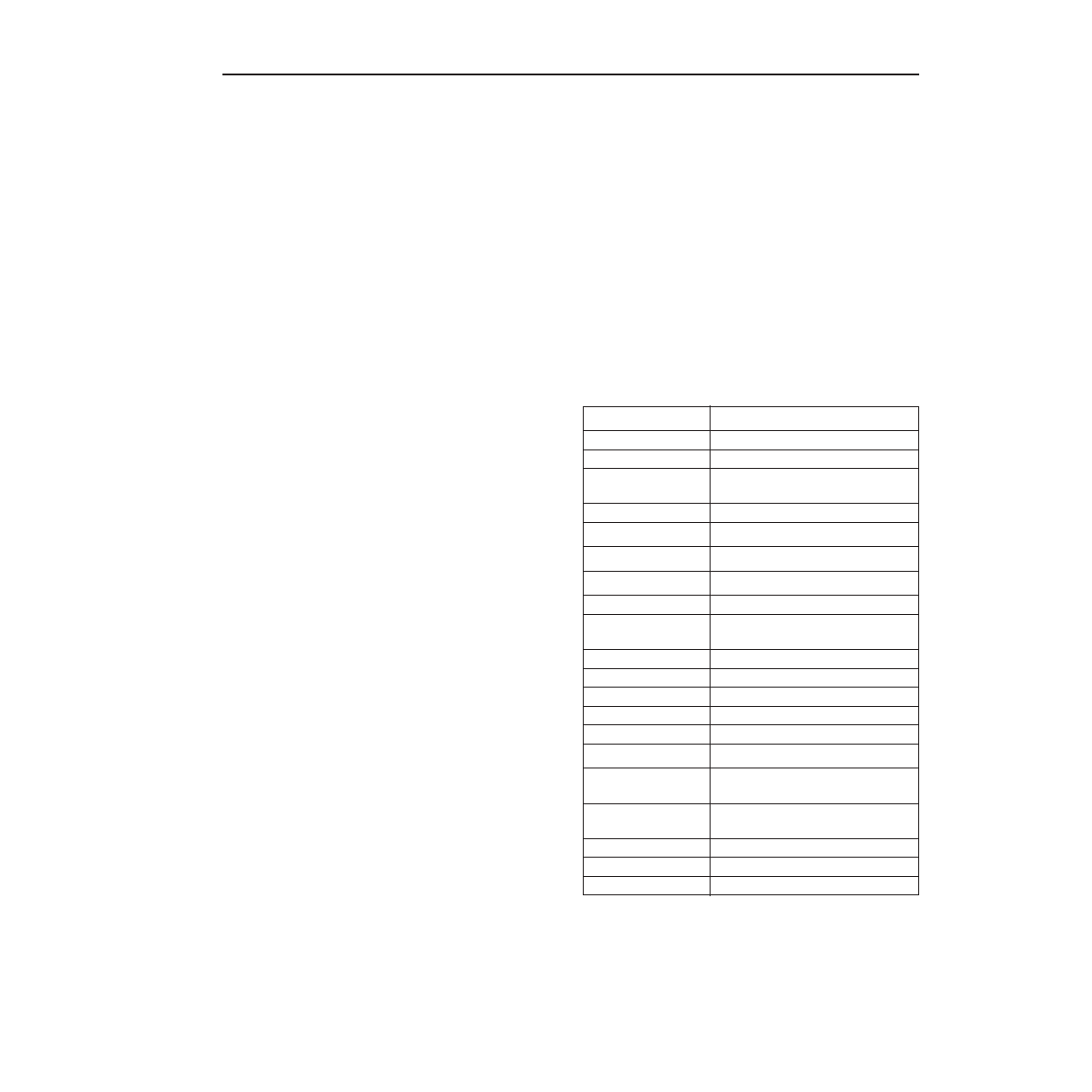

Table 14. PIO Options

Input

Option

InputSpeed

Fast,Delayed,Normal

FloatValue

Pull-up,Pull-down,None

RegisterMode

Latch,FF,FastZeroHoldFF,

None(directinput)

ClockSense

Inverted,Noninverted

KeeperMode

on,off

LVDSResistor

on,off

Output

Option

OutputSpeed

Fast,Slew

OutputDrive

Current

12mA/6mA,6mA/3mA,or

24mA/12mA

OutputFunction

Normal,FastOpenDrain

OutputSense

Active-high,Active-low

3-StateSense

Active-high,Active-low

ClockSense

Inverted,Noninverted

Logic Options

See Table 15

I/OControls

Option

ClockEnable

Active-high,Active-low,

AlwaysEnabled

Set/ResetLevel

Active-high,Active-low,

NoLocalReset

Set/ResetType

Synchronous,Asynchronous

Set/ResetPriority

CEoverLSR,LSRoverCE

GSRControl

EnableGSR,DisableGSR

相关PDF资料 |

PDF描述 |

|---|---|

| OR4E043BM680-DB | FPGA, 1296 CLBS, 380000 GATES, PBGA680 |

| OR4E061BA352-DB | FPGA, 2024 CLBS, 515000 GATES, PBGA352 |

| OR4E061BM680-DB | FPGA, 2024 CLBS, 515000 GATES, PBGA680 |

| OR4E062BA352-DB | FPGA, 2024 CLBS, 515000 GATES, PBGA352 |

| OR4E062BM680-DB | FPGA, 2024 CLBS, 515000 GATES, PBGA680 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| OR4E04-3BM680C | 功能描述:FPGA - 现场可编程门阵列 10368 LUT 466 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| OR4E06 | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:ORCASeries 4 FPGAs |

| OR4E06-1BA352C | 功能描述:FPGA - 现场可编程门阵列 16192 LUT 466 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| OR4E06-1BA352I | 功能描述:FPGA - 现场可编程门阵列 16192 LUT 466 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| OR4E06-1BM680C | 功能描述:FPGA - 现场可编程门阵列 16192 LUT 466 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

发布紧急采购,3分钟左右您将得到回复。