- 您现在的位置:买卖IC网 > PDF目录189449 > ORT82G51BM680-DB (LATTICE SEMICONDUCTOR CORP) FPGA, 1296 CLBS, 380000 GATES, PBGA680 PDF资料下载

参数资料

| 型号: | ORT82G51BM680-DB |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 1296 CLBS, 380000 GATES, PBGA680 |

| 封装: | PLASTIC, FBGA-680 |

| 文件页数: | 24/109页 |

| 文件大小: | 1379K |

| 代理商: | ORT82G51BM680-DB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页

21

Lattice Semiconductor

Data Sheet

April, 2002

8b/10b SERDES Backplane Interface FPSC

ORCA ORT82G5 1.0-1.25/2.0-2.5/3.125-3.5 Gbits/s

Backplane Transceiver Core Detailed Description (continued)

SERDES Transmit and Receive PLLs

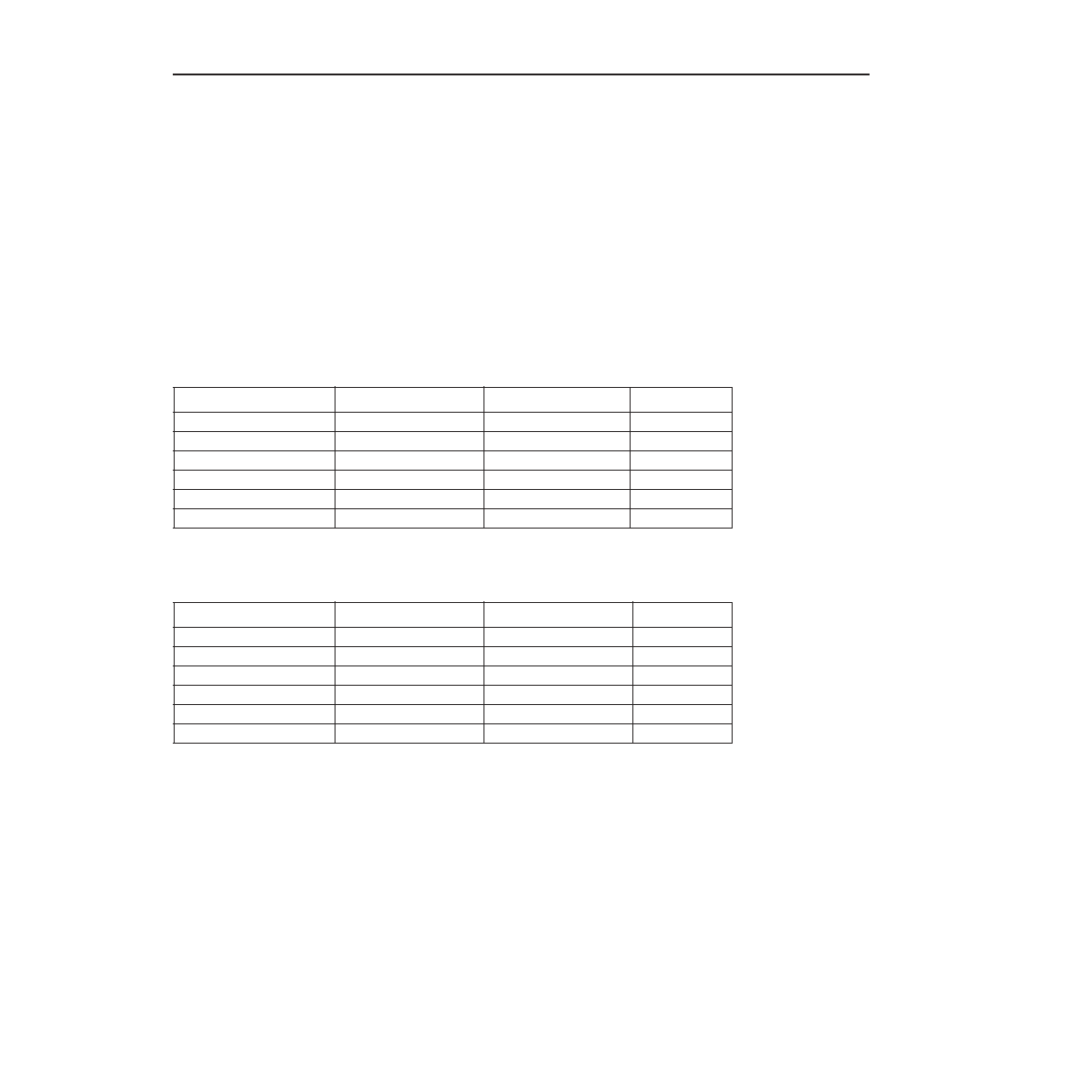

The high-speed transmit and receive serial data can operate at 1.0—1.25 Gbits/s or 2.0—3.125 Gbits/s depending

on the state of the control bits from the microprocessor interface. Table 4 shows the relationship between the data

rates, the reference clock, and the transmit TWCKx clocks.

The receiver section receives high-speed serial data at its differential CML input port. These data are fed to the

clock recovery section which generates a recovered clock and retimes the data. This means that the receive clocks

are asynchronous between channels. The retimed data are deserialized and presented as a 10-bit encoded or a 8-

bit unencoded parallel data on the output port. RWCKx receive byte clocks are available synchronous with the par-

allel words. The receiver also recognizes the comma characters and aligns the bit stream to the proper word

boundary.

Table 5 shows the relationship between the data rates, the reference clock, and the RWCKx clocks.

Table 4. Transmit PLL Clock and Data Rates

Note: The selection of full-rate or half-rate for a given reference clock speed is set by a bit in the transmit control register and can be set per

channel.

Table 5. Receive PLL Clock and Data Rates

Note: The selection of full-rate or half-rate for a given reference clock speed is set by a bit in the receive control register and can be set per

channel.

Reference Clock

There are two pairs of reference clock inputs on the ORT82G5. The differential reference clock is distributed to all

four channels in a quad. Each channel has a differential buffer to isolate the clock from the other channels. The

input clock is preferably a differential signal; however, the device can operate with a single-ended input. The input

reference clock directly impacts the transmit data eye, so the clock should have low jitter. In particular, jitter compo-

nents in the dc—5 MHz range should be minimized.

Note: The reference clock, REFCLK, is equivalent to REFINP and REFINN; throughout the text simply refer to the

reference clock as REFCLK.

For more information on the reference clock input requirements and connections to either single ended or differen-

tial inputs, see the SERDES reference clock application note.

Data Rate

Reference Clock

TCK78[A, B] Clock

Rate

1.0 Gbits/s

100 MHz

25 MHz

Half

1.25 Gbits/s

125 MHz

31.25 MHz

Half

2.0 Gbits/s

100 MHz

50 MHz

Full

2.5 Gbits/s

125 MHz

62.5 MHz

Full

3.125 Gbits/s

156 MHz

78 MHz

Full

3.5 Gbits/s

175 MHz

87.5 MHz

Full

Data Rate

Reference Clock

RWCKx Clocks

Rate

1.0 Gbits/s

100 MHz

25 MHz

Half

1.25 Gbits/s

125 MHz

31.25 MHz

Half

2.0 Gbits/s

100 MHz

50 MHz

Full

2.5 Gbits/s

125 MHz

62.5 MHz

Full

3.125 Gbits/s

156 MHz

78 MHz

Full

3.5 Gbits/s

175 MHz

87.5 MHz

Full

相关PDF资料 |

PDF描述 |

|---|---|

| OSC-1B1FREQ | TCVCXO, CLIPPED SINE OUTPUT, 10 MHz - 50 MHz |

| OSC-3A110MHZ | TCVCXO, CLIPPED SINE OUTPUT, 10 MHz |

| OSC-3B219.68MHZ | TCVCXO, CLIPPED SINE OUTPUT, 19.68 MHz |

| OSC1213A | TCVCXO, SINE OUTPUT, 13 MHz |

| OSC1218D | TCVCXO, SINE OUTPUT, 12.8 MHz |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ORT82G5-1BM680I | 功能描述:FPGA - 现场可编程门阵列 10368 LUT 372 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| ORT82G5-1F680C | 功能描述:FPGA - 现场可编程门阵列 ORCA FPSC 3.7GBITS/s BP XCVR 643K RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| ORT82G5-1F680I | 功能描述:FPGA - 现场可编程门阵列 ORCA FPSC 2.7Gbits/s BP XCVR 643K RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| ORT82G5-1FN680C | 功能描述:FPGA - 现场可编程门阵列 ORCA FPSC 1.5V 3.7 G b Bpln Xcvr 643K Gt RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| ORT82G5-1FN680C1 | 功能描述:FPGA - 现场可编程门阵列 10368 LUT 372 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

发布紧急采购,3分钟左右您将得到回复。