- 您现在的位置:买卖IC网 > PDF目录369949 > PCF8890 240 + 1 outputs TFT LCD gate driver PDF资料下载

参数资料

| 型号: | PCF8890 |

| 英文描述: | 240 + 1 outputs TFT LCD gate driver |

| 中文描述: | 240 1输出TFT液晶栅极驱动器 |

| 文件页数: | 48/76页 |

| 文件大小: | 385K |

| 代理商: | PCF8890 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页当前第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

2002 Aug 16

48

Philips Semiconductors

Preliminary specification

STN RGB - 384 output column driver

PCF8832

12.2

I

2

C-bus Hs-mode protocol

The PCF8832 is a slave receiver/transmitter. If data is to

be read from the device, the SDACK pin must be

connected, otherwise SDACK may be unused.

Hs-mode can only commence after the following

conditions:

START condition (S)

8-bit master code (00001XXX)

Not-acknowledge bit (A).

The master code has two functions, it allows arbitration

and synchronization between competing masters at

F/S-modespeeds,resultinginonewinner.Alsothemaster

code indicates the beginning of an Hs-mode transfer.

In Figs 50 and 51 these conditions are visualized.

As no device is allowed to acknowledge the master code,

the master code is followed by a not-acknowledge (A).

After this A-bit, and the SCL line has been pulled up to a

HIGH level, the active master switches to Hs-mode and

enables at t

H

the current-source pull-up circuit for the SCL

signal (see Fig.51).

The active master will then send a repeated START

condition (Sr) followed by a 7-bit slave address with a

R/W-bit and receives an acknowledge bit (A) from the

selected slave. After each acknowledge bit (A) or

not-acknowledge bit (A), the active master disables its

current-source pull-up circuit. The active master

re-enables its current source again when all devices have

released and the SCL signal reaches a HIGH level. The

rising of the SCL is done by a resistor pull-up and so is

slower, the last part of the SCL rise time is speeded up

because the current source is enabled. Data transfer only

switches back to F/S-mode after a stop condition (P).

A write sequence after the Hs-mode is selected

(see Fig.53) is initiated with a START condition (S) from

the I

2

C-bus master and this is followed by the slave

address. All slaves with the corresponding address

acknowledge in parallel, all the others will ignore the

I

2

C-bus transfer.

After acknowledgement of a write (W) condition, one or

more command words follow which define the status of the

addressed slaves. A command word consists of a control

byte, which defines CO and D/C, plus a data byte

(see Table 21, Table 22 and Fig.52).

The last control byte is tagged with a cleared most

significant bit, the continuation bit CO. The control and

data bytes are also acknowledged by all addressed slaves

on the bus.

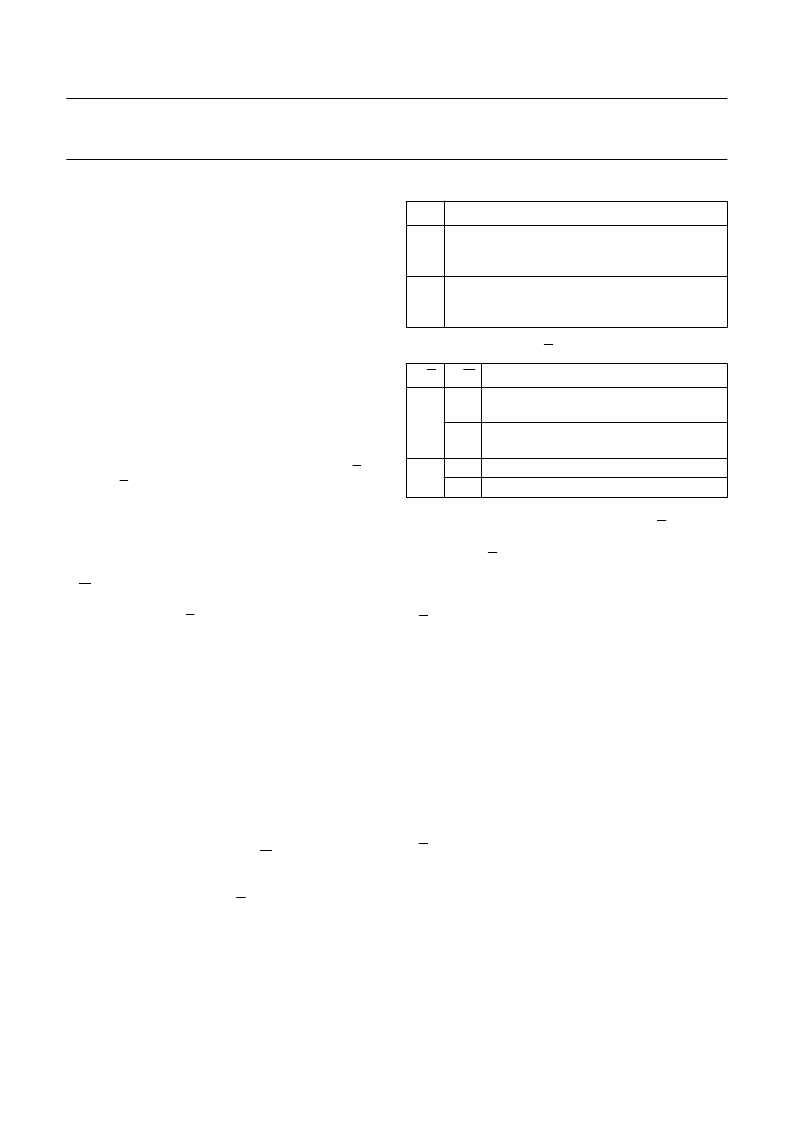

Table 21

Definition of CO

Table 22

Definition of D/C

Afterthelastcontrolbyte,dependingontheD/Cbitsetting,

a series of display data bytes or command data bytes may

follow. If the D/C bit was set to logic 1, these display bytes

are stored in the display RAM at the address specified by

the data pointer. The data pointer is updated automatically

and the data is directed to the intended PCF8832. If the

D/C bit of the last control byte was set to ‘0’, these

command bytes will be decoded and the setting of the

device will be changed according to the received

commands. The acknowledgement after each byte is

made only by the addressed PCF8832. At the end of the

transmission the I

2

C-bus master issues a STOP

condition (P) and switches back to F/S-mode, however, to

reduce the overhead of the master code, it is possible for

a master to link a number of Hs-mode transfers, separated

by repeated START conditions (Sr).

A read sequence (Fig.53) follows after the Hs-mode is

selected. The PCF8832 will immediately start to output the

requested data until a NOT acknowledge is transmitted by

the master. Before the read access, the user has to set the

D/C bit to the appropriate value by a preceding write

access. The write access should be terminated by a

repeated START condition so that the Hs-mode is not

disabled.

CO

ACTION

0

last control byte to be sent; only a stream of data

bytes are allowed to follow; this stream may only

be terminated by a STOP or RE-START condition

another control byte will follow this control byte

unless a STOP or RE-START condition is

received

1

D/C

R/W

ACTION

0

0

command byte will be decoded and used

to set up the device

command byte of requested ADR will be

returned

data byte will be stored in the display RAM

RAM read-back is not supported

1

1

0

1

相关PDF资料 |

PDF描述 |

|---|---|

| PCF93C110 | 32-Bit Microcontroller |

| PCB93C110 | 32-Bit Microcontroller |

| PCG3N60C3W | TRANSISTOR | IGBT | N-CHAN | 600V V(BR)CES | CHIP |

| PCG4AX280MM | FUEHRUNGSSCHIENE LEITERPLATTE 280MM |

| PCH-1415FN | CLIP PIPE 15MM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| P-CF8GB-266W-DVDC | 制造商:PNY Technologies 功能描述:OPTIMA PRO UDMA 8GB CF CARD - Bulk |

| P-CF8GB-266X-DVDC | 制造商:PNY Technologies 功能描述:OPTIMA PRO UDMA 8GB CF CARD - Bulk |

| PCF-A-03 | 制造商:Adam Technologies Inc 功能描述:03 Positions RECEPTACLE WITH BOARD HOOKS Top entry |

| PCFA-1GC02A-301N | 制造商:SMART Modular Technology Inc 功能描述:FLASH CARD WITH CONNECTOR - Trays |

| PCFA-1GC03AN-301 | 制造商:SMART Modular Technology Inc 功能描述:FLASH CARD WITH CONNECTOR - Trays |

发布紧急采购,3分钟左右您将得到回复。