- 您现在的位置:买卖IC网 > PDF目录69322 > RK80532PG072512 (INTEL CORP) 2800 MHz, MICROPROCESSOR, PGA478 PDF资料下载

参数资料

| 型号: | RK80532PG072512 |

| 厂商: | INTEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 2800 MHz, MICROPROCESSOR, PGA478 |

| 封装: | FLIP CHIP, MICRO, PGA-478 |

| 文件页数: | 51/79页 |

| 文件大小: | 2634K |

| 代理商: | RK80532PG072512 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页当前第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页

Intel Pentium 4 Processor on 90 nm Process Datasheet

55

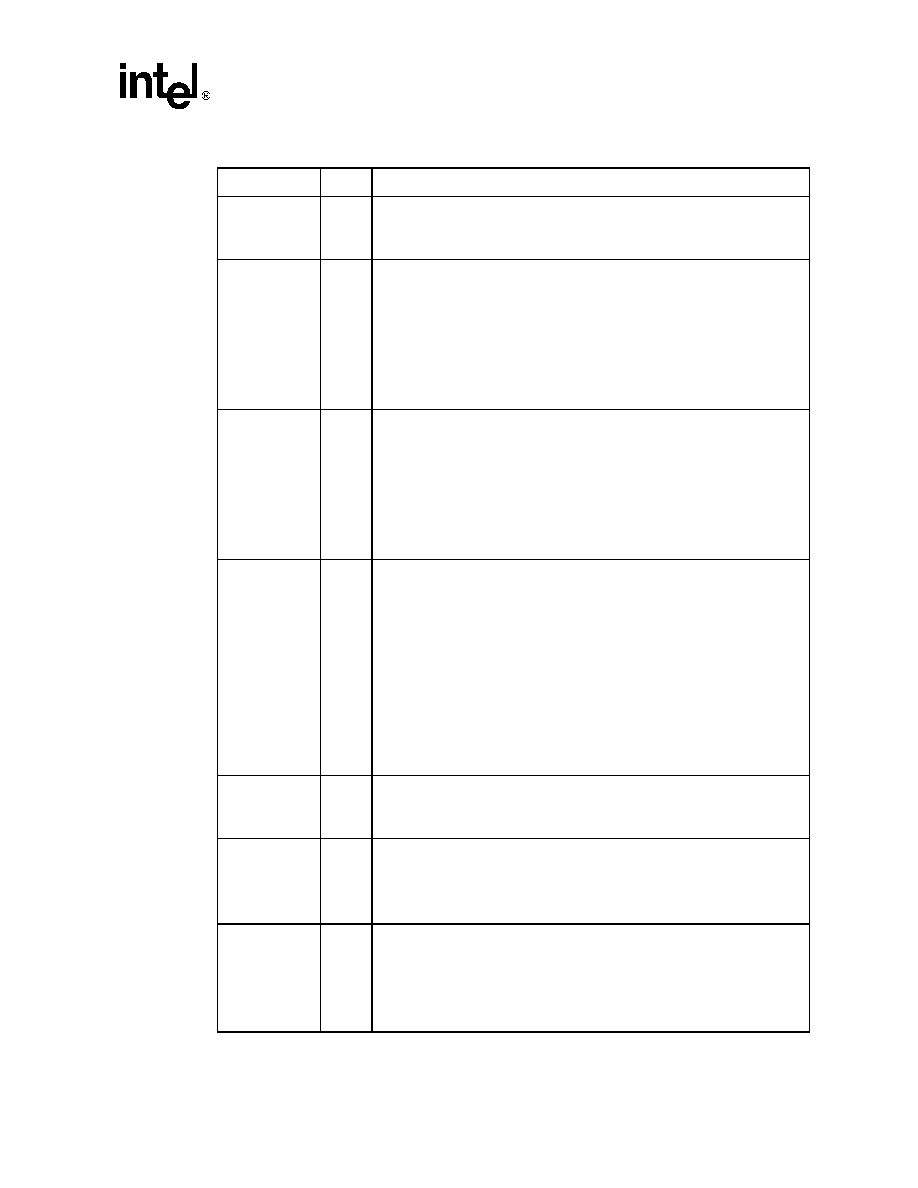

Pin List and Signal Description

DRDY#

Input/

Output

DRDY# (Data Ready) is asserted by the data driver on each data transfer,

indicating valid data on the data bus. In a multi-common clock data transfer,

DRDY# may be de-asserted to insert idle clocks. This signal must connect the

appropriate pins of all processor FSB agents.

DSTBN[3:0]#

Input/

Output

Data strobe used to latch in D[63:0]#.

DSTBP[3:0]#

Input/

Output

Data strobe used to latch in D[63:0]#.

FERR#/PBE#

Output

FERR#/PBE# (Floating Point Error/Pending Break Event) is a multiplexed signal

and its meaning is qualified by STPCLK#. When STPCLK# is not asserted,

FERR#/PBE# indicates a floating-point error and will be asserted when the

processor detects an unmasked floating-point error. When STPCLK# is not

asserted, FERR#/PBE# is similar to the ERROR# signal on the Intel 387

coprocessor, and is included for compatibility with systems using MS-DOS*-type

floating-point error reporting.

When STPCLK# is asserted, an assertion of FERR#/PBE# indicates that the

processor has a pending break event waiting for service. The assertion of

FERR#/PBE# indicates that the processor should be returned to the Normal

state. For additional information on the pending break event functionality,

including the identification of support of the feature and enable/disable

information, refer to volume 3 of the Intel Architecture Software Developer's

Manual and the Intel Processor Identification and the CPUID Instruction

application note.

GTLREF

Input

GTLREF determines the signal reference level for GTL+ input pins. GTLREF is

used by the GTL+ receivers to determine if a signal is a logical 0 or logical 1.

Refer to the Intel 865G/865GV/865PE/865P Chipset Platform Design Guide for

more information.

HIT#

HITM#

Input/

Output

Input/

Output

HIT# (Snoop Hit) and HITM# (Hit Modified) convey transaction snoop operation

results. Any FSB agent may assert both HIT# and HITM# together to indicate

that it requires a snoop stall, which can be continued by reasserting HIT# and

HITM# together.

IERR#

Output

IERR# (Internal Error) is asserted by a processor as the result of an internal

error. Assertion of IERR# is usually accompanied by a SHUTDOWN transaction

on the processor FSB. This transaction may optionally be converted to an

external error signal (e.g., NMI) by system core logic. The processor will keep

IERR# asserted until the assertion of RESET#.

This signal does not have on-die termination. Refer to Section 2.4 for

termination requirements.

Table 25. Signal Description (Page 4 of 8)

Name

Type

Description

Signals

Associated Strobe

D[15:0]#, DBI0#

DSTBN0#

D[31:16]#, DBI1#

DSTBN1#

D[47:32]#, DBI2#

DSTBN2#

D[63:48]#, DBI3#

DSTBN3#

Signals

Associated Strobe

D[15:0]#, DBI0#

DSTBP0#

D[31:16]#, DBI1#

DSTBP1#

D[47:32]#, DBI2#

DSTBP2#

D[63:48]#, DBI3#

DSTBP3#

相关PDF资料 |

PDF描述 |

|---|---|

| RK80532RC049128 | 32-BIT, 2100 MHz, MICROPROCESSOR, CPGA478 |

| RK80532RC056128 | 2400 MHz, MICROPROCESSOR, CPGA478 |

| RK80546KG0882MM | 64-BIT, 3200 MHz, MICROPROCESSOR, CPGA604 |

| RK80546KG1042MM | 64-BIT, 3600 MHz, MICROPROCESSOR, CPGA604 |

| RK80546KG0802MM | 64-BIT, 3000 MHz, MICROPROCESSOR, CPGA604 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| RK80532PG072512S L6WJ | 制造商:Intel 功能描述:MPU Pentium 制造商:Intel 功能描述:MPU Pentium? 4 Processor 64-Bit 0.13um 2.8GHz 478-Pin FCPGA2 |

| RK80532PG080512 | 制造商:Intel 功能描述:P4 3.0GHZ 800MHZ FSB - Trays |

| RK80532PG080512SL6WK | 制造商:Intel 功能描述:MPU Pentium? 4 Processor NetBurst 64-Bit 0.13um 3GHz 478-Pin FCPGA2 |

| RK80532PG0882M | 制造商:Intel 功能描述:MPU PENTIUM 4 PROCESSOR NETBURST 64-BIT 0.13UM 3.2GHZ 478-P - Trays |

| RK80532PG096512 | 制造商:Intel 功能描述:MPU PENTIUM 4 PROCESSOR NETBURST 64-BIT 0.13UM 3.4GHZ - Trays |

发布紧急采购,3分钟左右您将得到回复。