- 您现在的位置:买卖IC网 > PDF目录192305 > S71GL064A04BAI0B3 (Spansion Inc.) Stacked Multi-Chip Product (MCP) Flash Memory and RAM PDF资料下载

参数资料

| 型号: | S71GL064A04BAI0B3 |

| 厂商: | Spansion Inc. |

| 英文描述: | Stacked Multi-Chip Product (MCP) Flash Memory and RAM |

| 中文描述: | 堆叠式多芯片产品(MCP)的闪存和RAM |

| 文件页数: | 55/102页 |

| 文件大小: | 1606K |

| 代理商: | S71GL064A04BAI0B3 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页当前第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页

56

S71GL032A Based MCPs

S71GL032A_00_A0 March 31, 2005

Advance

Info rmation

Command Definitions

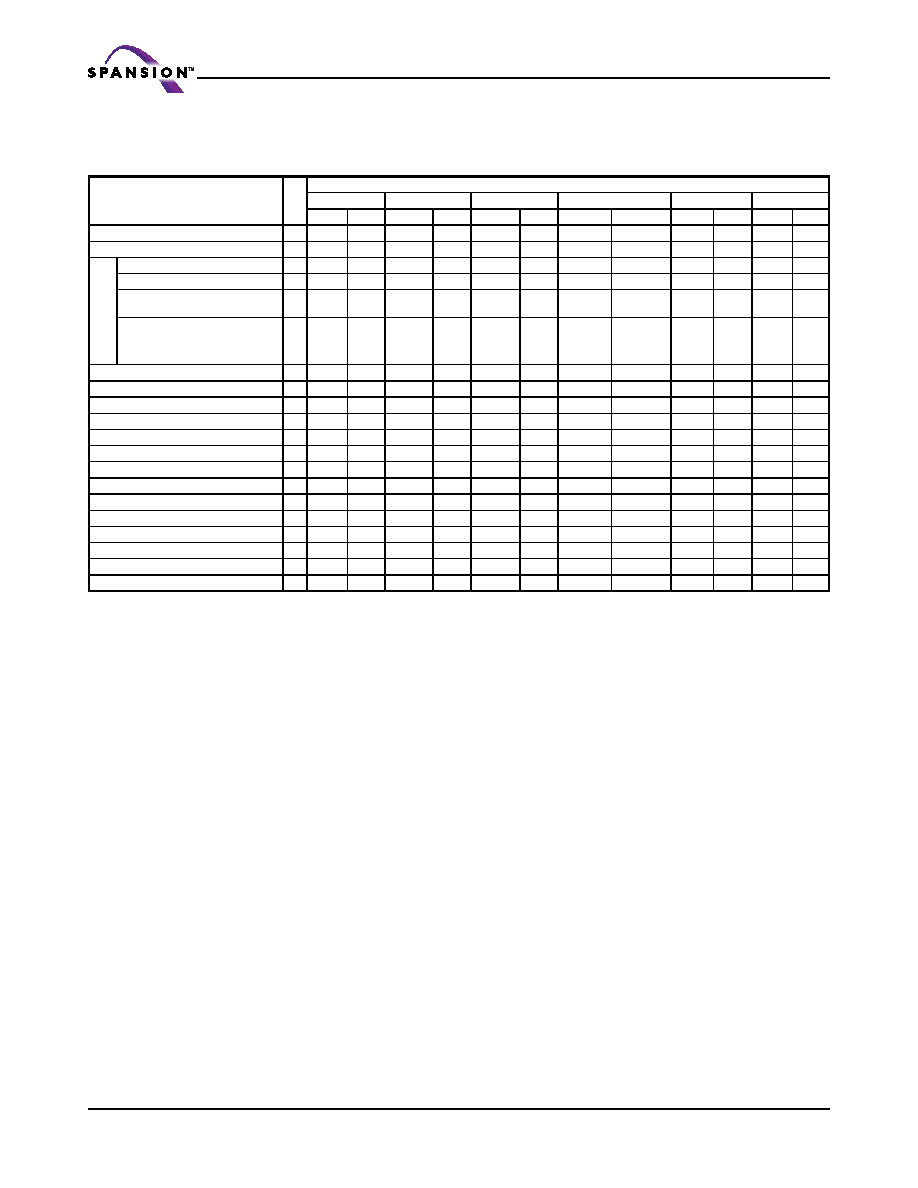

Table 22. Command Definitions (x16 Mode)

Command

Sequence

(Note 1)

Cy

cl

es

Bus Cycles (Notes 2–5)

First

Second

Third

Fourth

Fifth

Sixth

Addr Data

Addr

Data

Addr

Data

Addr

Data

Addr

Data Addr Data

Read (Note 6)

1

RA

RD

Reset (Note 7)

1

XXX

F0

Auto

select

(Note

8)

Manufacturer ID

4

555

AA

2AA

55

555

90

X00

0001

Device ID (Note 9)

4

555

AA

2AA

55

555

90

X01

227E

X0E

X0F

Secured Silicon Sector Factory

Protect (Note 10)

4

555

AA

2AA

55

555

90

X03

(Note 10)

Sector Group Protect Verify (Note

12)

4

555

AA

2AA

55

555

90

(SA)X02

00/01

Enter Secured Silicon Sector Region

3

555

AA

2AA

55

555

88

Exit Secured Silicon Sector Region

4

555

AA

2AA

55

555

90

XXX

00

Program

4

555

AA

2AA

55

555

A0

PA

PD

Write to Buffer (Note 11)

3

555

AA

2AA

55

SA

25

SA

WC

PA

PD

WBL

PD

Program Buffer to Flash

1

SA

29

Write to Buffer Abort Reset (Note 13)

3

555

AA

2AA

55

555

F0

Unlock Bypass

3

555

AA

2AA

55

555

20

Unlock Bypass Program (Note 14)

2

XXX

A0

PA

PD

Unlock Bypass Reset (Note 15)

2

XXX

90

XXX

00

Chip Erase

6

555

AA

2AA

55

555

80

555

AA

2AA

55

555

10

Sector Erase

6

555

AA

2AA

55

555

80

555

AA

2AA

55

SA

30

Program/Erase Suspend (Note 16)

1

XXX

B0

Program/Erase Resume (Note 17)

1

XXX

30

CFI Query (Note 18)

1

55

98

Legend:

X = Don’t care

RA = Read Address of memory location to be read.

RD = Read Data read from location RA during read operation.

PA = Program Address. Addresses latch on falling edge of WE# or

CE# pulse, whichever happens later.

PD = Program Data for location PA. Data latches on rising edge of

WE# or CE# pulse, whichever happens first.

SA = Sector Address of sector to be verified (in autoselect mode) or

erased. Address bits A21–A15 uniquely select any sector.

WBL = Write Buffer Location. Address must be within same write

buffer page as PA.

WC = Word Count. Number of write buffer locations to load minus 1.

Notes:

1. See Table 1 for description of bus operations.

2. All values are in hexadecimal.

3. Shaded cells indicate read cycles. All others are write cycles.

4. During unlock and command cycles, when lower address bits are

555 or 2AA as shown in table, address bits above A11 and data

bits above DQ7 are don’t care.

5. No unlock or command cycles required when device is in read

mode.

6. Reset command is required to return to read mode (or to erase-

suspend-read mode if previously in Erase Suspend) when device

is in autoselect mode, or if DQ5 goes high while device is

providing status information.

7. Fourth cycle of the autoselect command sequence is a read

cycle. Data bits DQ15–DQ8 are don’t care. Except for RD, PD

and WC. See Autoselect Command Sequence section for more

information.

8. Device ID must be read in three cycles.

9. If WP# protects highest address sector, data is 98h for factory

locked and 18h for not factory locked. If WP# protects lowest

address sector, data is 88h for factory locked and 08h for not

factor locked.

10. Data is 00h for an unprotected sector group and 01h for a

protected sector group.

11. Total number of cycles in command sequence is determined by

number of words written to write buffer. Maximum number of

cycles in command sequence is 21, including “Program Buffer to

Flash” command.

12. Command sequence resets device for next command after

aborted write-to-buffer operation.

13. Unlock Bypass command is required prior to Unlock Bypass

Program command.

14. Unlock Bypass Reset command is required to return to read

mode when device is in unlock bypass mode.

15. System may read and program in non-erasing sectors, or enter

autoselect mode, when in Erase Suspend mode. Erase Suspend

command is valid only during a sector erase operation.

16. Erase Resume command is valid only during Erase Suspend

mode.

17. Command is valid when device is ready to read array data or

when device is in autoselect mode.

相关PDF资料 |

PDF描述 |

|---|---|

| S71GL064A04BAI0F3 | Stacked Multi-Chip Product (MCP) Flash Memory and RAM |

| S71GL064A04BAW0B3 | Stacked Multi-Chip Product (MCP) Flash Memory and RAM |

| S71GL064A04BAW0F3 | Stacked Multi-Chip Product (MCP) Flash Memory and RAM |

| S71GL064A04BFI0B2 | Stacked Multi-Chip Product (MCP) Flash Memory and RAM |

| S71GL064A04BFI0B3 | Stacked Multi-Chip Product (MCP) Flash Memory and RAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| S71GL064A04BAI0F0 | 制造商:SPANSION 制造商全称:SPANSION 功能描述:Stacked Multi-Chip Product (MCP) Flash Memory and RAM |

| S71GL064A04BAI0F2 | 制造商:SPANSION 制造商全称:SPANSION 功能描述:Stacked Multi-Chip Product (MCP) Flash Memory and RAM |

| S71GL064A04BAI0F3 | 制造商:SPANSION 制造商全称:SPANSION 功能描述:Stacked Multi-Chip Product (MCP) Flash Memory and RAM |

| S71GL064A04BAW0B0 | 制造商:SPANSION 制造商全称:SPANSION 功能描述:Stacked Multi-Chip Product (MCP) Flash Memory and RAM |

| S71GL064A04BAW0B2 | 制造商:SPANSION 制造商全称:SPANSION 功能描述:Stacked Multi-Chip Product (MCP) Flash Memory and RAM |

发布紧急采购,3分钟左右您将得到回复。