- 您现在的位置:买卖IC网 > PDF目录85252 > SDED7-256M-N9Y (SANDISK CORP) FLASH MEMORY DRIVE CONTROLLER, PBGA115 PDF资料下载

参数资料

| 型号: | SDED7-256M-N9Y |

| 厂商: | SANDISK CORP |

| 元件分类: | 存储控制器/管理单元 |

| 英文描述: | FLASH MEMORY DRIVE CONTROLLER, PBGA115 |

| 封装: | 12 X 9 MM, 1.20 MM HEIGHT, FBGA-115 |

| 文件页数: | 16/87页 |

| 文件大小: | 1675K |

| 代理商: | SDED7-256M-N9Y |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页

Rev. 1.2

Product Overview

mDOC H3 EFD Featuring Embedded TrueFFS Data Sheet

23

92-DS-1205-10

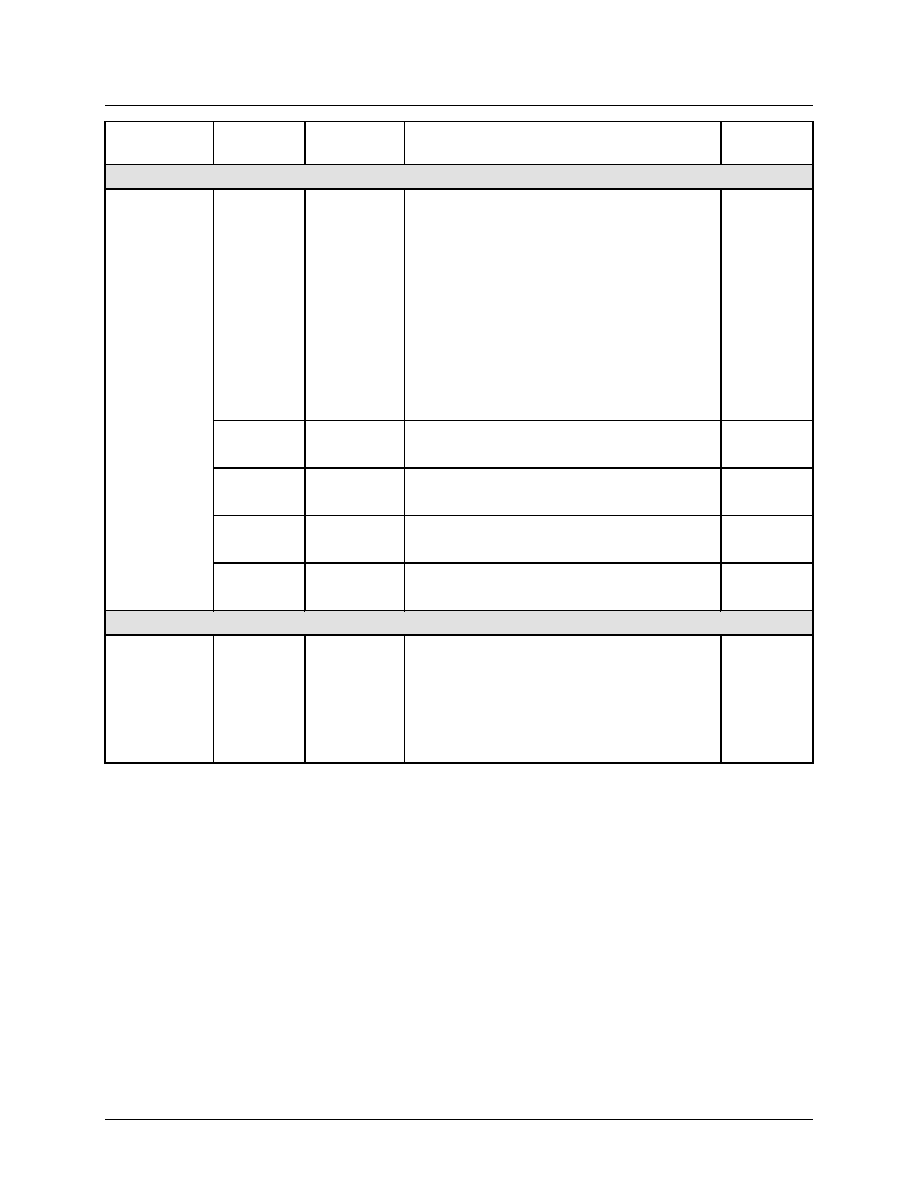

Signal

Ball No.

Signal Type

1

Description

Signal

Direction

Reserved

C2, C3, C4,

C5, C6, C7,

C8, C9,

C10, D1,

D2, D9,

D10, E9, F1,

F9, G1, H1,

J1, K1, K2,

L2, L9, L10,

M2, M3, M4,

M5, M6,M7,

M8, M9,

M10

-

All reserved signals are not connected

internally, and if not identified in this document

then it is recommended to leave them floating

to guarantee forward compatibility with future

products. They should not be connected to

arbitrary signals.

P1

ST/PU

Test Data In (JTAG).

Used for dedicated developer product only

4.

Input

M1

CMOS output Test Data Out (JTAG).

Used for dedicated developer product only

4.

Output

L1

ST/PU

Test Mode Select (JTAG)

Used for dedicated developer product only

4.

Input

RSRVD

N1

ST/PU

Test Clock (JTAG).

Used for dedicated developer product only

4.

Input

Mechanical

NC

A1, A2, A9,

A10, B1, B2,

B9, B10,

G5, G6, H5,

H6, N2, N9,

N10, P2,

P9, P10

-

Not Connected.

1.

The following abbreviations are used: ST - Schmidt Trigger input. IN/PD – CMOS input with internal pull down resistor (77K to 312K;

135K typical), which is enabled only when the 8KB memory window is in use, ST/PU - Schmitt Trigger input with internal pull up

resistor (95K to 261 K; 149 K typical).

2.

When mDOC H3 is used as a Master device, SO is used for Serial Interface Data In, and SI used for Serial Interface Data Out.

3.

The capacitor is required only for 1.8V Core and 1.8V I/O configuration. Please see section 9.5 for further details.

4.

The RSRVD JTAG balls will only be enabled on special versions of the mDOC H3 devices that will be used for debugging severe system

problems. In order to support this feature, the JTAG balls should be brought out to a separate header or test points. The JTAG RSRVD

balls must not be connected to the JTAG scan chain that is used for the rest of the PCB. If not used they should be left floating.

5.

BUSY#, DMARQ# and IRQ# should not be pulled up to any voltage higher than VCCQ. A pull-up resistor is required if this pin will be

connected to an input. A 10K ohm resistor to Vccq is recommended, however the exact value depends on system power, timing and signal

integrity requirements.

2.3.3

System Interface

See Figure 5 for a simplified I/O diagram of multiplexed interface mDOC H3. The power

connections and capacitors in this diagram are for illustration only. For detailed

recommendations regarding power connections and required capacitors, please refer to section

相关PDF资料 |

PDF描述 |

|---|---|

| SPMC68336AVFT20 | 32-BIT, MROM, 20.97 MHz, MICROCONTROLLER, PQFP160 |

| SPMC68336GCFT20 | 32-BIT, MROM, 20.97 MHz, MICROCONTROLLER, PQFP160 |

| SC104002VPVR2 | 16-BIT, FLASH, 40 MHz, MICROCONTROLLER, PQFP112 |

| S9S12XF512J0MLH | MICROCONTROLLER, QFP64 |

| SC9S12XF512J0CLMR | MICROCONTROLLER, QFP112 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SDED7-512M-NAT | 功能描述:IC MDOC H3 512MB FBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:150 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:4K (2 x 256 x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:2.5 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-VFDFN 裸露焊盘 供应商设备封装:8-DFN(2x3) 包装:管件 产品目录页面:1445 (CN2011-ZH PDF) |

| SDED7-512M-NAY | 功能描述:IC MDOC H3 512MB FBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:150 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:4K (2 x 256 x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:2.5 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-VFDFN 裸露焊盘 供应商设备封装:8-DFN(2x3) 包装:管件 产品目录页面:1445 (CN2011-ZH PDF) |

| SDEG-15P | 制造商:HRS 制造商全称:HRS 功能描述:STRAIGHT/METAL PCB D-SUB |

| SDEG-15P05 | 制造商:HRS 制造商全称:HRS 功能描述:STRAIGHT/METAL PCB D-SUB |

| SDEG-15S | 制造商:HRS 制造商全称:HRS 功能描述:STRAIGHT/METAL PCB D-SUB |

发布紧急采购,3分钟左右您将得到回复。