- 您现在的位置:买卖IC网 > PDF目录7463 > SFPA8192Q1BO2TO-I-QT-223-STD (Swissbit NA Inc)FLASH SSD SMART UDMA 2.5" 8GB PDF资料下载

参数资料

| 型号: | SFPA8192Q1BO2TO-I-QT-223-STD |

| 厂商: | Swissbit NA Inc |

| 文件页数: | 24/76页 |

| 文件大小: | 0K |

| 描述: | FLASH SSD SMART UDMA 2.5" 8GB |

| 视频文件: | Swissbit Manufacturing Overview |

| RoHS指令信息: | Environment Protection Declaration |

| 标准包装: | 4 |

| 系列: | P-120 |

| 存储容量: | 8GB |

| 存储器类型: | FLASH |

| 其它名称: | 1052-1025 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

�� �

�

�

�j)�

�k)�

�l)�

�m)�

�n)�

�o)�

�p)�

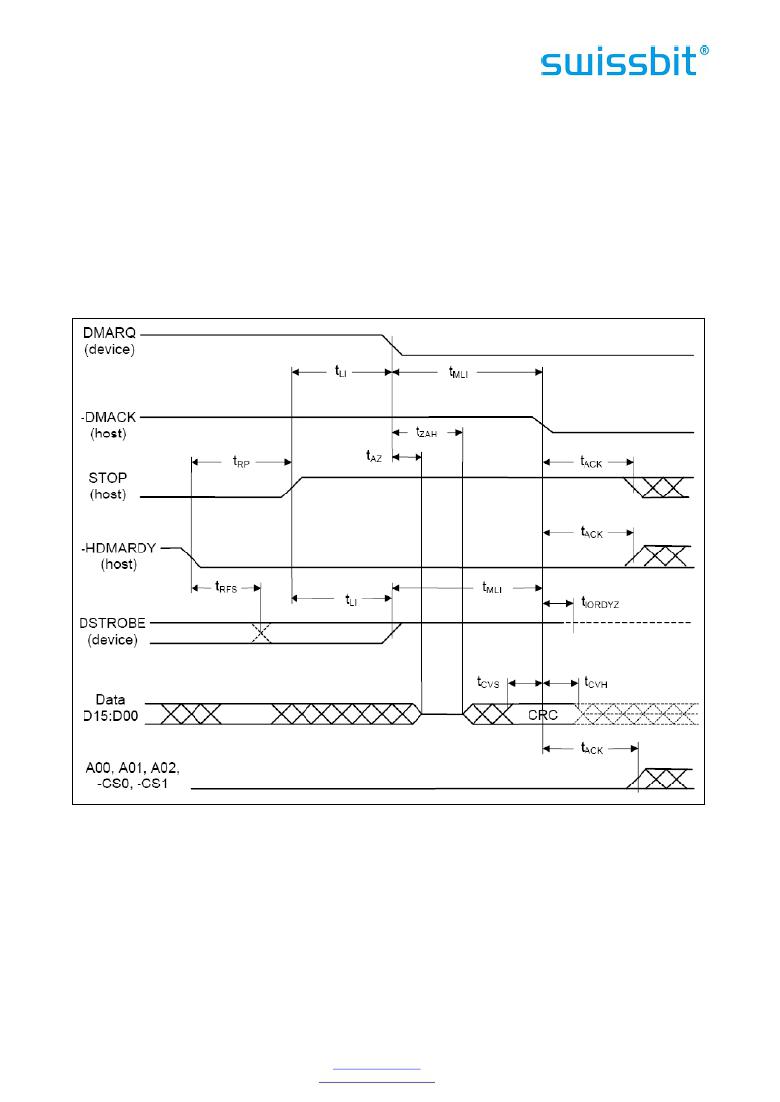

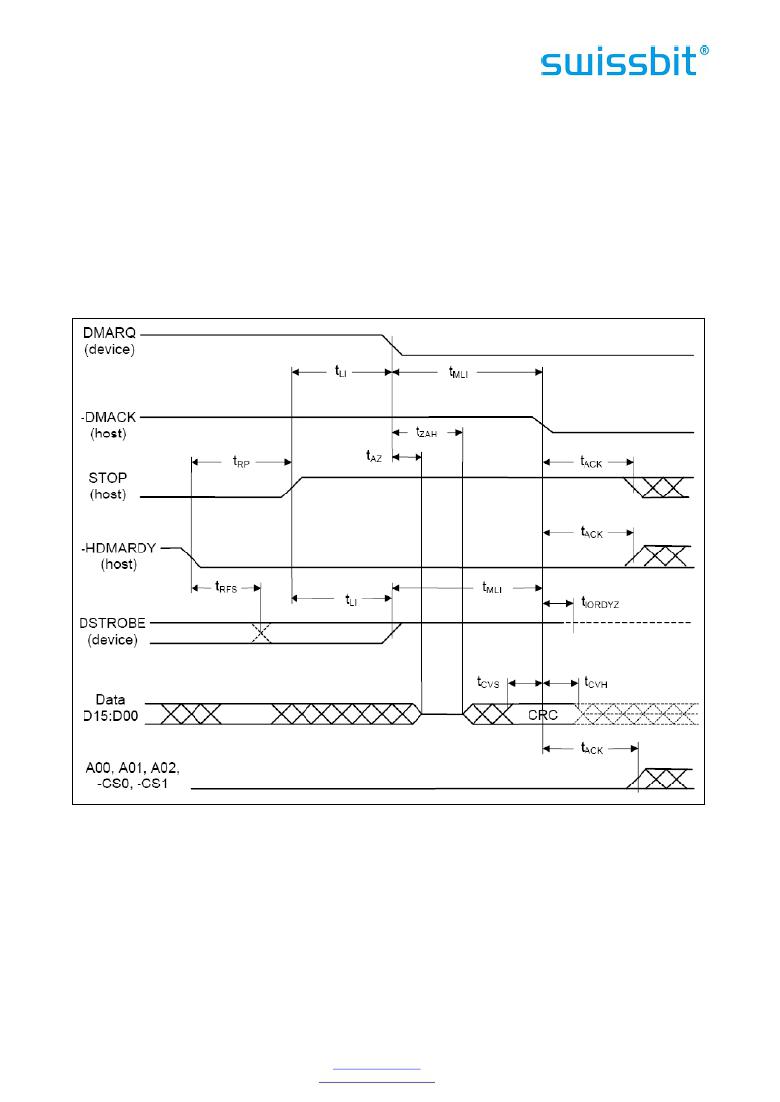

�If� the� host� has� not� placed� the� result� of� its� CRC� calculation� on� D[15:00]� since� first� driving� D[15:00]�

�during� (9),� the� host� shall� place� the� result� of� its� CRC� calculation� on� D[15:00]� (see� 6.3.2.5� ).�

�The� host� shall� negate� -DMACK� no� sooner� than� t� MLI� after� the� device� has� asserted� DSTROBE� and� negated�

�DMARQ� and� the� host� has� asserted� STOP� and� negated� -HDMARDY,� and� no� sooner� than� t� DVS� after� the�

�host� places� the� result� of� its� CRC� calculation� on� D[15:00].�

�The� device� shall� latch� the� host’s� CRC� data� from� D[15:00]� on� the� negating� edge� of� -DMACK.�

�The� device� shall� compare� the� CRC� data� received� from� the� host� with� the� results� of� its� own� CRC�

�calculation.� If� a� miscompare� error� occurs� during� one� or� more� Ultra� DMA� burst� for� any� one� command,�

�at� the� end� of� the� command,� the� device� shall� report� the� first� error� that� occurred� (see� 6.3.2.5� ).�

�The� device� shall� release� DSTROBE� within� t� IORDYZ� after� the� host� negates� -DMACK.�

�The� host� shall� neither� negate� STOP� nor� assert� -HDMARDY� until� at� least� t� ACK� after� the� host� has� negated�

�-DMACK.�

�The� host� shall� not� assert� -IORD,� -CS0,� -CS1,� DA2,� DA1,� or� DA0� until� at� least� t� ACK� after� negating� DMACK.�

�Figure� 7:� Ultra� DMA� Data-In� Burst� Host� Termination� Timing�

�Notes:� The� definitions� for� the� STOP,� HDMARDY,� and� DSTROBE� signal� lines� are� no� longer� in� effect� after�

�DMARQ� and� DMACK� are� negated.�

�6.3.2.4.6� Initiating� an� Ultra� DMA� Data-Out� Burst�

�An� Ultra� DMA� Data-out� burst� is� initiated� by� following� the� steps� lettered� below.� The� timing� diagram�

�is� shown� in� Figure� 8:� Ultra� DMA� Data-Out� Burst� Initiation� Timing.� The� timing� parameters� are�

�specified� in� Table� 22:� Ultra� DMA� Data� Burst� Timing� Requirements� and� are� described� in� Table� 23:� Ultra� DMA�

��The� following� steps� shall� occur� in� the� order� they� are� listed� unless� otherwise� specifically� allowed:�

�a)� The� host� shall� keep� -DMACK� in� the� negated� state� before� an� Ultra� DMA� burst� is� initiated.�

�b)� The� device� shall� assert� DMARQ� to� initiate� an� Ultra� DMA� burst.�

�c)�

�Steps� (c),� (d),� and� (e)� may� occur� in� any� order� or� at� the� same� time.� The� host� shall� assert� STOP.�

�d)� The� host� shall� assert� HSTROBE.�

�Swissbit� AG�

�Industriestrasse� 4�

�Swissbit� reserves� the� right� to� change� products� or� specifications� without� notice.�

�Revision:� 1.00�

�CH-9552� Bronschhofen�

�Switzerland�

�www.swissbit.com�

�industrial@swissbit.com�

�P-120_data_sheet_PA-QxBO_Rev100.doc�

�Page� 24� of� 76�

�相关PDF资料 |

PDF描述 |

|---|---|

| 3-1437653-5 | CONN BARRIER STRIP 10CIRC .375 |

| 6432.0153.15 | MOD PWR IN/OUT/SW/1PL QC 1.5 PNL |

| 4306R-102-391 | RES ARRAY 390 OHM 3 RES 6-SIP |

| SFSA8192V1BR4TO-I-DT-226-STD | FLASH SLC UDMA/MDMA/PIO 8GB |

| 6432.0151.15 | MOD PWR IN/OUT/SW/1PL SLD 1.5PNL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SFPA8192Q1BO2TO-I-QT-243 | 制造商:Swissbit 功能描述: |

| SFPA8192Q1BO2TO-I-QT-243-STD | 制造商:SWISSBIT NA INC 功能描述:FLASH 制造商:SWISSBIT 功能描述:SSD PATA 8GB 2.5" IND P-120 制造商:SWISSBIT 功能描述:SSD, PATA, 8GB, 2.5", IND, P-120 |

| SFPAB13202 | 制造商:Panasonic Industrial Company 功能描述:KNOB |

| SFPAB17206 | 制造商:Panasonic Industrial Company 功能描述:KNOB |

| SFPAB18201K | 制造商:Panasonic Industrial Company 功能描述:PLATE |

发布紧急采购,3分钟左右您将得到回复。