参数资料

| 型号: | SM3E-19.44M |

| 厂商: | Connor-Winfield |

| 文件页数: | 4/36页 |

| 文件大小: | 0K |

| 描述: | IC MOD TIMING 19.440MHZ STRAT 3E |

| 标准包装: | 1 |

| 系列: | SM3 |

| 类型: | 定时模块,系统时钟 |

| PLL: | 是 |

| 主要目的: | 以太网,ADM,DSLAM,SONET/SDH,Stratum,TDM |

| 输入: | LVCMOS |

| 输出: | LVCMOS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 8:3 |

| 差分 - 输入:输出: | 无/无 |

| 频率 - 最大: | 19.44MHz |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 通孔 |

| 封装/外壳: | 32-DIP 模块 |

| 包装: | 管件 |

| 其它名称: | CW643 SM3E 19.44M SM3E19.44M |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

SM3E Data Sheet #:

TM054

Page 12 of 36 Rev: 04 Date: 01/26/11

Copyright 2011 The Connor-Winfield Corp. All Rights Reserved

Specifications subject to change without notice

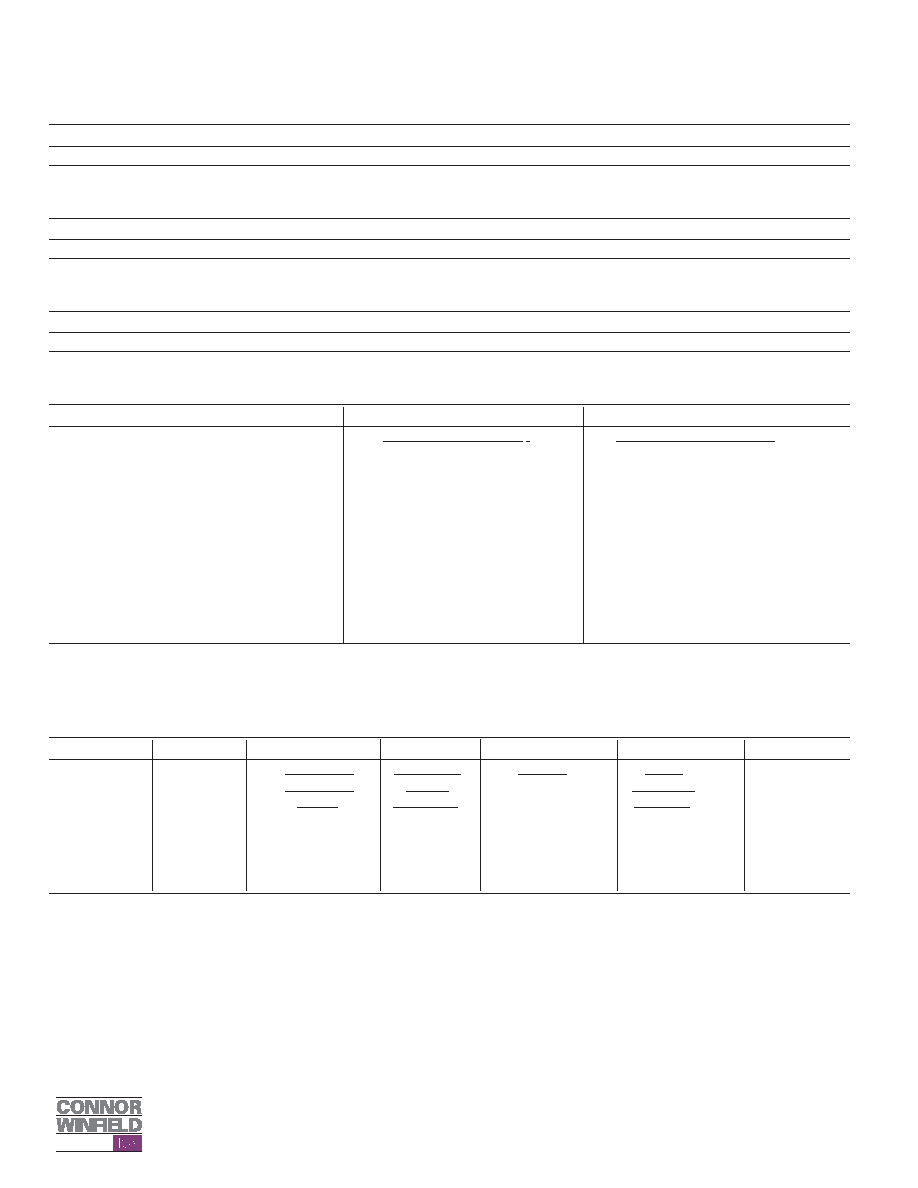

Register Descriptions and Operation

Chip_ID_low, 0x00 (R)

Bit7~Bit0

LowbyteofchipID:0x11

Chip_ID_High, 0x01 (R)

Bit7~Bit0

HighbyteofchipID:0x30

Chip_Revision, 0x02 (R)

Bit7~Bit0

Chiprevisionnumber:0x05

Bandwidth_PBO, 0x03 (R/W)

Bit7~Bit5

Bit4

Bit3~Bit0

Reserved

PhaseBuild-outOption:

BandwidthSelectioninHz:

1:Enable

0000:0.00084

0:Disable

0001:0.0016

Default:1

0010:0.0032

0011:0.0063

0100:0.012

0101:0.025

0110:0.049

0111:0.098(ResetDefault)

1000:0.20

1001:0.39

1010:0.78

1011-1111:1.6

BITS 3 - 0 select the phase lock loop bandwidth in Hertz. The reset default is 0.098 Hz. Bit 4 enables or disables phase

build-out for active reference phase hits. Phase build-out operation requires register access operation of the device.

Ctl_Mode, 0x04 (R/W)

Bit7~Bit6Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

Reserved

Default:0

M/SOutput

BITSClock

HMRef:

Active

Reserved

Pulsewidth

Output

0:Registercontrol

Reference

control:

Frequency:

ofopmode/ref

Selection:

0:50%

1:1.544MHz

(Willalways

1:Manual

1:Controlledby 0:2.048MHz

be0)

0:Automatic

FR_Pulse_Width

(readonly)

Default:1

register

Default:0

When bit 1 is reset (automatic reference and mode selection), Bits 3 - 0 of the Op_Mode register become

read-only. The power-up default for Bit 1 = 1 for manual reference selection and default for Bit 4 = 0 for 50% duty

cycle on M/S Output.

When the device is in slave mode, it will lock to the M/S REF, independent of the values written to BITS 3 - 0

of the Op_mode register. The operational mode and reference selection written to Bits 3 - 0 while in slave mode will,

however, take effect when the device is made the master.

When bit 1 of the Ctl_Mode register is reset (automatic reference and mode selection) and the device is in

master mode,

BITS 3 - 0 of the Op_Mode register become read-only.

相关PDF资料 |

PDF描述 |

|---|---|

| SM802104UMG TR | IC SYNTHESIZER 2CH 24-QFN |

| SM802105UMG TR | IC SYNTHESIZER 2CH 24-QFN |

| SM802108UMG | IC SYNTEHSIZER 156.25MHZ 24QFN |

| SM802109UMG TR | IC SYNTHESIZER QUAD 100MHZ 24QFN |

| SM840002KA TR | IC CLK SYNTHESIZER LN 16-TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SM3F-100TQ-ACTEL | 功能描述:ADAPTER MODULE 100TQFP RoHS:否 类别:编程器,开发系统 >> 适配器 系列:* 标准包装:96 系列:- 模块/板类型:TQFP 插座模块 适用于相关产品:- |

| SM3F-100VQ-ACT | 制造商:Microsemi Corporation 功能描述:ACTEL VQ100 ADAPTER MODULES |

| SM3F-100VQ-ACTEL | 功能描述:ADAPTER MODULE 100VQFP RoHS:否 类别:编程器,开发系统 >> 适配器 系列:* 标准包装:96 系列:- 模块/板类型:TQFP 插座模块 适用于相关产品:- |

| SM3F-108QN-ACTEL | 功能描述:ADAPTER MODULE 108QFN RoHS:否 类别:编程器,开发系统 >> 适配器 系列:* 标准包装:96 系列:- 模块/板类型:TQFP 插座模块 适用于相关产品:- |

| SM3F-121CS-ACTEL | 功能描述:ADAPTER MODULE 121CSP RoHS:否 类别:编程器,开发系统 >> 适配器 系列:* 标准包装:96 系列:- 模块/板类型:TQFP 插座模块 适用于相关产品:- |

发布紧急采购,3分钟左右您将得到回复。