- 您现在的位置:买卖IC网 > PDF目录373464 > SN65LVDS302_07 (Texas Instruments, Inc.) PROGRAMMABLE 27-BIT SERIAL-TO-PARALLEL RECEIVER PDF资料下载

参数资料

| 型号: | SN65LVDS302_07 |

| 厂商: | Texas Instruments, Inc. |

| 英文描述: | PROGRAMMABLE 27-BIT SERIAL-TO-PARALLEL RECEIVER |

| 中文描述: | 可编程27位串行到并行接收机 |

| 文件页数: | 17/41页 |

| 文件大小: | 1412K |

| 代理商: | SN65LVDS302_07 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页

www.ti.com

4 MHz

9 %

8 MHz

9 %

20 MHz

8.7 %

15 MHz

8.1 %

30 MHz

8.1 %

Spec Limit

1 ChM

Spec Limit

2 ChM

Spec Limit

3 ChM

65 MHz

7.5 %

9.0

8.5

7.5

7.0

6.5

8.0

6.0

0

10

20

30

40

50

60

70

PCLK - Frequency - MHz

P

12

11

10

9

8

7

6

5

4

P

PLL - Frequency - MHz

100

0

200

300

400

600

500

700

TIMING CHARACTERISTICS

ps

480

f

30

2

1

CLK

-

·

·

ps

480

f

15

2

1

CLK

-

·

·

ps

410

f

10

2

1

CLK

-

·

·

SN65LVDS302

SLLS733B–JUNE 2006–REVISED FEBRUARY 2007

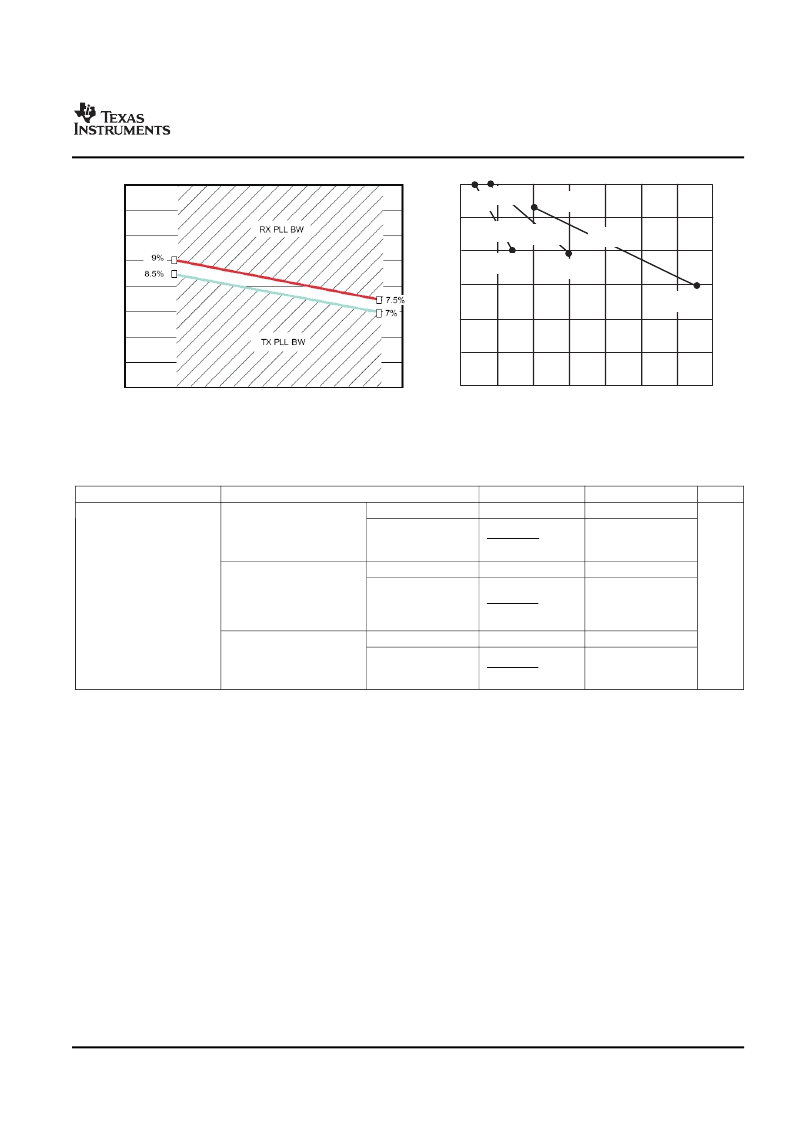

Figure 6. SN65LVDS302 PLL Bandwidth (also showing the SN65LVDS301 PLL bandwidth)

PARAMETER

TEST CONDITIONS

MIN

MAX

UNIT

1ChM: x=0..29, f

PCLK

=15 MHz;

RXEN at V

DD

, V

IH

,

V

=GND, R

L

=100

, test setup

as in

Figure 8

, test pattern as in

Table 11

f

CLK

=15 MHz

(4)

f

CLK

=4 MHz to 15 MHz

(5)

630

2ChM: x = 0..14,

f

=30 MHz

RXEN at V

DD

, V

IH

=V

,

V

=GND, R

L

=100

, test setup

as in

Figure 8

, test pattern as in

Table 12

f

CLK

=30 MHz

(4)

f

CLK

=8 MHz to 30 MHz

(5)

630

Receiver input skew

margin; see

(3)

and

Figure 43

t

(RSKMx

ps

3ChM:

RXEN at V

, V

=V

,

V

=GND, test setup as in

Figure 8

, test pattern as in

Table 13

f

CLK

= 65 MHz

(4)

f

= 20 MHz to 65

MHz

(5)

360

(1)

Receiver Input Skew Margin (t

) is the timing margin available for transmitter output pulse position (t

), interconnect skew, and

interconnect inter-symbol interference. tRSKM represents the reminder of the serial bit time not taken up by the receiver strobe

uncertainty;. The t

assumes a bit error rate better than 10

-12

.

t

is indirectly proportional to the internal set-up and hold time uncertainty, ISI and duty cycle distortion from the front end receiver,

the skew missmatch between CLK and data D0, D1, and D2, as well as the PLL cycle-to-cycle jitter.

This includes the receiver internal set-up and hold time uncertainty, all PLL related high-frequency random and deterministic jitter

components that impact the jitter budget, ISI and duty cycle distortion from the front end receiver, and the skew between CLK and data

D0, D1, and D2; The pulse position min/max variation is given with a bit error rate target of 10

–12

; Measurements of the total jitter are

taken over a sample amount of > 10

–12

samples.

The Minimum and Maximum Limits are based on statistical analysis of the device performance over process, voltage, and temp ranges.

These Minimum and Maximum Limits are simulated only.

(2)

(3)

(4)

(5)

17

Submit Documentation Feedback

相关PDF资料 |

PDF描述 |

|---|---|

| SN65LVDS305ZQE | PROGRAMMABLE 27-BIT DISPLAY SERIAL INTERFACE TRANSMITTER |

| SN65LVDS386EVM | Single Supply RS232C Line Driver/Receiver(?????μ?o?RS232C ?o?????????¨???2???2??????) |

| SN65LVDS387EVM | Single Supply RS232C Line Driver/Receiver(?????μ?o?RS232C ?o?????????¨???2???2??????) |

| SN65LVDT390DRG4 | HIGH-SPEED DIFFERENTIAL LINE RECEIVERS |

| SN65LVDTS33D | HIGH-SPEED DIFFERENTIAL RECEIVERS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SN65LVDS302ZQE | 功能描述:串行器/解串器 - Serdes Program 27B Display Ser Interface RoHS:否 制造商:Texas Instruments 类型:Deserializer 数据速率:1.485 Gbit/s 输入类型:ECL/LVDS 输出类型:LVCMOS 输入端数量:1 输出端数量:20 工作电源电压:2.375 V to 2.625 V 工作温度范围:0 C to + 70 C 封装 / 箱体:TQFP-64 |

| SN65LVDS302ZQER | 功能描述:串行器/解串器 - Serdes Programmable 27B Displ Ser Interface RoHS:否 制造商:Texas Instruments 类型:Deserializer 数据速率:1.485 Gbit/s 输入类型:ECL/LVDS 输出类型:LVCMOS 输入端数量:1 输出端数量:20 工作电源电压:2.375 V to 2.625 V 工作温度范围:0 C to + 70 C 封装 / 箱体:TQFP-64 |

| SN65LVDS303ZQE | 功能描述:IC PROG 27BIT SERDES TX 80-BGA RoHS:否 类别:集成电路 (IC) >> 接口 - 串行器,解串行器 系列:65LVDS 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 功能:解串器 数据速率:2.5Gbps 输入类型:串行 输出类型:并联 输入数:- 输出数:24 电源电压:1.8 V ~ 3.3 V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:64-TQFP 裸露焊盘 供应商设备封装:64-TQFP-EP(10x10) 包装:管件 |

| SN65LVDS303ZQER | 功能描述:串行器/解串器 - Serdes QVGA-VGA 27B Display Serial Interface RoHS:否 制造商:Texas Instruments 类型:Deserializer 数据速率:1.485 Gbit/s 输入类型:ECL/LVDS 输出类型:LVCMOS 输入端数量:1 输出端数量:20 工作电源电压:2.375 V to 2.625 V 工作温度范围:0 C to + 70 C 封装 / 箱体:TQFP-64 |

| SN65LVDS304ZQER | 功能描述:串行器/解串器 - Serdes QVGAVGA 27B Display Ser Interface RoHS:否 制造商:Texas Instruments 类型:Deserializer 数据速率:1.485 Gbit/s 输入类型:ECL/LVDS 输出类型:LVCMOS 输入端数量:1 输出端数量:20 工作电源电压:2.375 V to 2.625 V 工作温度范围:0 C to + 70 C 封装 / 箱体:TQFP-64 |

发布紧急采购,3分钟左右您将得到回复。