- 您现在的位置:买卖IC网 > PDF目录69348 > ST5451D (STMICROELECTRONICS) 1 CHANNEL(S), SERIAL COMM CONTROLLER, PDSO28 PDF资料下载

参数资料

| 型号: | ST5451D |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 1 CHANNEL(S), SERIAL COMM CONTROLLER, PDSO28 |

| 封装: | SO-28 |

| 文件页数: | 19/34页 |

| 文件大小: | 269K |

| 代理商: | ST5451D |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页

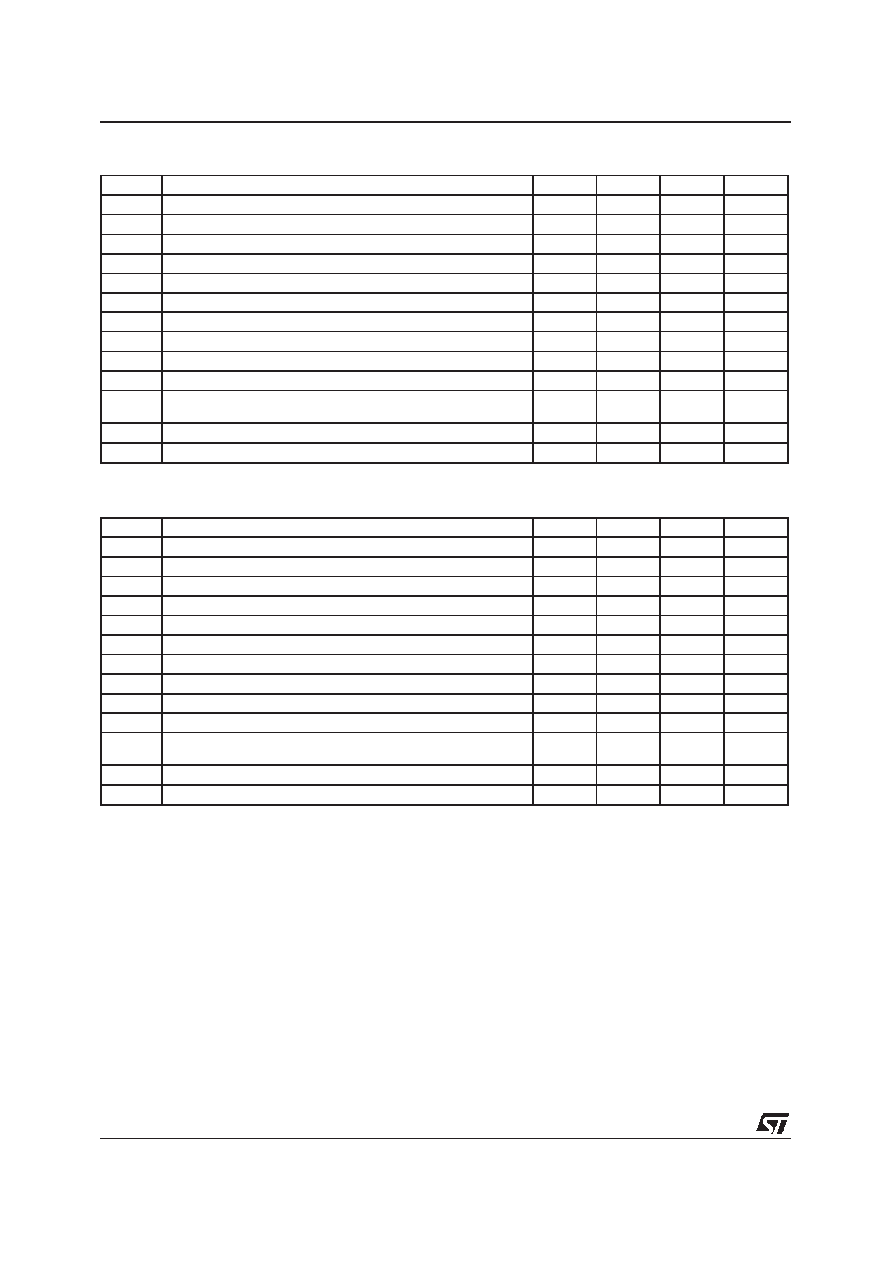

DYNAMIC ELECTRICAL CHARACTERISTICS - Double Clock Interface

Symbol

Parameter

Min.

Typ.

Max.

Unit

FSync

8 KHz

8

KHz

FCLK

16 x n x FSync 1

≤ n ≤ 64

128

8192

KHz

tWCH

Period of CLK High

50

ns

tWCL

Period of CLK Low

50

ns

tRC

Rise Time of CLK

10

ns

tFC

Full Time of CLK

10

ns

tHCF

Hold Time: CLK - FS

0

ns

tSFC

Set-up Time: FS - CLK

30

ns

tDCD

Delay Time: CLK High to data valid. out: 150 pF

80

ns

tDCZ

Delay Time: to Data Disabled

0

80

ns

tDFD

Delay Time: FSync. High to data valid. count: 150 pF. Applies

only if Sync rises later than CLK raising edge.

80

ns

tSDC

Set-up Time: Data valid to CLK receive edge.

30

ns

tHDC

Hold Time: CLK low to data invalid.

30

ns

ELECTRICAL CHARACTERISTICS - Single Clock Interface

Symbol

Parameter

Min.

Typ.

Max.

Unit

FSync

8 KHz

8

KHz

FCLK

8 x n x FSync 1

≤ n ≤ 64

64

4096

KHz

tWCH

Period of CLK High

80

ns

tWCL

Period of CLK Low

80

ns

tRC

Rise Time of CLK

10

ns

tFC

Full Time of CLK

10

ns

tHCF

Hold Time: CLK - FS

0

ns

tSFC

Set-up Time: FS - CLK

100

ns

tDCD

Delay Time: CLK High to data valid. out: 150 pF

80

ns

tDCZ

Delay Time: to Data Disabled

0

80

ns

tDFD

Delay Time: FSync. High to data valid. count: 150 pF. Applies

only if Sync rises later than CLK raising edge.

80

ns

tSDC

Set-up Time: Data valid to CLK receive edge.

30

ns

tHDC

Hold Time: CLK low to data invalid.

30

ns

ST5451

26/34

相关PDF资料 |

PDF描述 |

|---|---|

| ST6200CN1/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO16 |

| ST6203CB3/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP16 |

| ST6201CN6/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO16 |

| ST6201CM3/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO16 |

| ST6201CM6/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST5451L | 制造商:Valor 功能描述: |

| ST5451N | 制造商:未知厂家 制造商全称:未知厂家 功能描述:ISDN, Other/Special/Miscellaneous |

| ST5452L | 制造商:Pulse 功能描述:- Bulk |

| ST5453L | 制造商:Pulse 功能描述:- Bulk |

| ST5454L | 制造商:Pulse 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。