- 您现在的位置:买卖IC网 > PDF目录98285 > TPS65040ZQER (TEXAS INSTRUMENTS INC) 8-CHANNEL POWER SUPPLY MANAGEMENT CKT, PBGA71 PDF资料下载

参数资料

| 型号: | TPS65040ZQER |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 电源管理 |

| 英文描述: | 8-CHANNEL POWER SUPPLY MANAGEMENT CKT, PBGA71 |

| 封装: | 5 X 5 MM, 0.50 MM PITCH, GREEN, PLASTIC, MICRO, BGA-71 |

| 文件页数: | 11/73页 |

| 文件大小: | 1928K |

| 代理商: | TPS65040ZQER |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页

www.ti.com

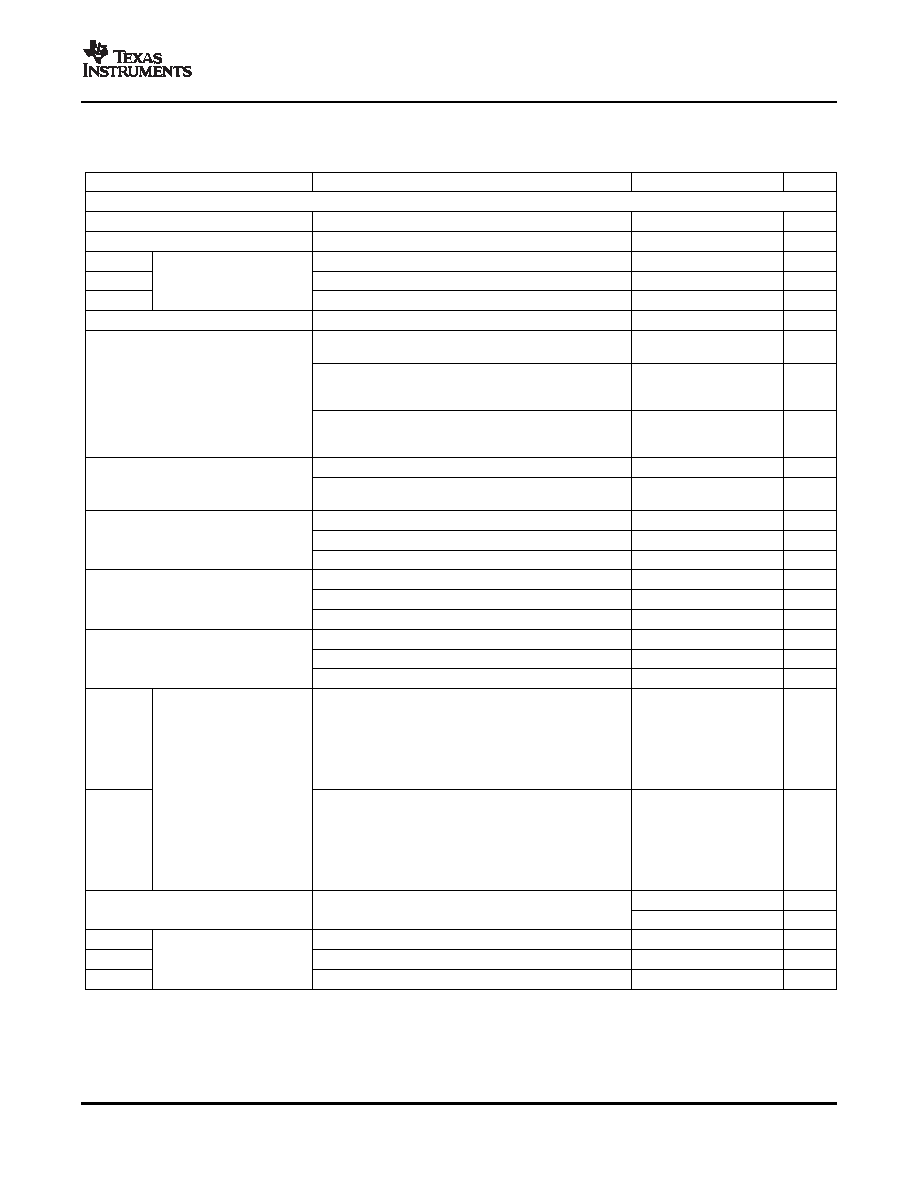

ELECTRICAL CHARACTERISTICS

SLVS708B – NOVEMBER 2006 – REVISED APRIL 2007

Over recommended input conditions, T

A = –30°C to 85°C, typical values are VBAT = 3.8 V, VIO1V8 = 1.85 V at TA = 25°C

(unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

CLOCK DISTRIBUTION

Input voltage(1)

0.75

1

VPP

fOUT

Output frequency(2)

26

MHz

VO1(CLKD)

SYSCLK_IN pin to SIN_SYSCLK1 pin

–3.5

–3

–2.5

dB

VO2(CLKD)

Output gain level(2)

SYSCLK_IN pin to SIN_SYSCLK2 pin

–1.5

–1

–0.5

dB

VO3(CLKD)

SYSCLK_IN pin to SIN_SYSCLK3 pin

–1.5

–1

–0.5

dB

ISD(CLKD)

Shutdown current

VBN3 pin at TA = 25°C

1

A

VBN3 pin, SIN_SYSCLK1 pin with CL1 = 15 pF,

2.3

4

mA

RL1 = 3 k at TA = 25°C

VBN3 pin, SIN_SYSCLK1 pin with CL1 = 15 pF,

RL1 = 3 k and SIN_SYSCLK2 pin with CL2 = 10 pF,

4.4

6.5

mA

IQ(CLKD)

Quiescent current

RL2 = 10 k at TA = 25°C

VBN3 pin, SIN_SYSCLK1 pin with CL1 = 15 pF,

RL1 =3 k and SIN_SYSCLK3 pin with CL3 = 10 pF,

4.4

6.5

mA

RL3 = 10 k at TA = 25°C

SIN_SYSCLK1 pin with CL1 = 15 pF, RL1 = 3 k

40%

60%

Duty cycle

SIN_SYSCLK2 pin with CL2 = 10 pF, RL2 = 10 k

40%

60%

SIN_SYSCLK3 pin with CL3 = 10 pF, RL3 = 10 k

1 kHz offset with CL1 = 15 pF, RL1 = 3 k

134

dBc/Hz

Phase noise(1)(3)

12.5 kHz offset with CL1 = 15 pF, RL1 = 3 k

146

dBc/Hz

SIN_SYSCLK1 pin

100 kHz offset with CL1 = 15 pF, RL1 = 3 k

147

dBc/Hz

1 kHz offset with CL2 = 10 pF, RL2 = 10 k

135

dBc/Hz

Phase noise(1)(3)

12.5 kHz offset with CL2 = 10 pF, RL2 = 10 k

147

dBc/Hz

SIN_SYSCLK2 pin

100 kHz offset with CL2 = 10 pF, RL2 = 10 k

149

dBc/Hz

1 kHz offset with CL3 = 10 pF, RL3 = 10 k

135

dBc/Hz

Phase noise(1)(3)

12.5 kHz offset with CL3 = 10 pF, RL3 = 10 k

147

dBc/Hz

SIN_SYSCLK3 pin

100 kHz offset with CL3 = 10 pF, RL3 = 10 k

149

dBc/Hz

SIN_SYSCLK2 pin with CL2 = 10 pF, RL2 = 10 k,

SIN_SYSCLK2 pin > 90% of final voltage

SYSCLK_EN pin = VVIO and

tST2(CLKD)

r[PSCNTSYSCLK_GSM](5) = 1 and SYSCLK_EN2 pin =

10

s

0V to VVIO, or

SYSCLK_EN pin = VVIO, SYSCLK_EN2 pin = VVIO and

r[PSCNTSYSCLK_GSM] = 0 to 1 (2)

Startup time(4)

SIN_SYSCLK3 pin with CL3 = 10 pF, RL3 = 10 k,

SIN_SYSCLK3 pin > 90% of final voltage

SYSCLK_EN pin = VVIO and

tST3(CLKD)

r[PSCNTSYSCLK_UMTS](6) = 1 and WRFON pin = 0V to

10

s

VVIO, or

SYSCLK_EN pin = VVIO, WRFON pin = VVIO and

r[PSCNTSYSCLK_UMTS] = 0 to 1(2)

3

4

pF

RIN

Input impedance(2)

SYSCLK_IN pin

14

18

22

k

CL1

SIN_SYSCKL1 pin

15

pF

CL2

Capacitive load

SIN_SYSCKL2 pin

10

pF

CL3

SIN_SYSCKL3 pin

10

pF

(1)

Not production tested. Specified by using the reference EVM. Using the external VCTCXO: TCO-5870 [TOYOCOM]

(2)

Not production tested. Specified by using the reference EVM.

(3)

Buck boost DC/DC converter is OFF

(4)

SIN_SYSCLK1 pin startup time depends on the VTCXO LDO startup time.

(5)

r[PSCNTSYSCLK_GSM] is a name of register command by serial interface.

(6)

r[PSCNTSYSCLK_UMTS] is the name of a register command by serial interface.

19

相关PDF资料 |

PDF描述 |

|---|---|

| TPS650531IRGERQ1 | POWER SUPPLY SUPPORT CKT, PQCC24 |

| TPS650532RGET | 5-CHANNEL POWER SUPPLY SUPPORT CKT, PQCC24 |

| TPS650531RGER | 5-CHANNEL POWER SUPPLY SUPPORT CKT, PQCC24 |

| TPS65055RSMR | 1.8 A DUAL SWITCHING CONTROLLER, 2475 kHz SWITCHING FREQ-MAX, PQCC32 |

| TPS65058RGET | 1.8 A DUAL SWITCHING CONTROLLER, 2475 kHz SWITCHING FREQ-MAX, PQCC32 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TPS65050EVM-195 | 功能描述:电源管理IC开发工具 TPS65050-195 Eval Mod RoHS:否 制造商:Maxim Integrated 产品:Evaluation Kits 类型:Battery Management 工具用于评估:MAX17710GB 输入电压: 输出电压:1.8 V |

| TPS65050RSMR | 功能描述:PMIC 解决方案 6-Ch Pwr Mgmt IC RoHS:否 制造商:Texas Instruments 安装风格:SMD/SMT 封装 / 箱体:QFN-24 封装:Reel |

| TPS65050RSMRG4 | 功能描述:PMIC 解决方案 6Ch Pwr Mgmt IC RoHS:否 制造商:Texas Instruments 安装风格:SMD/SMT 封装 / 箱体:QFN-24 封装:Reel |

| TPS65050RSMT | 功能描述:PMIC 解决方案 6-Channel Power Management IC RoHS:否 制造商:Texas Instruments 安装风格:SMD/SMT 封装 / 箱体:QFN-24 封装:Reel |

| TPS65050RSMTG4 | 功能描述:PMIC 解决方案 6-Ch Pwr Mgmt IC RoHS:否 制造商:Texas Instruments 安装风格:SMD/SMT 封装 / 箱体:QFN-24 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。