- 您现在的位置:买卖IC网 > PDF目录98285 > TPS65040ZQER (TEXAS INSTRUMENTS INC) 8-CHANNEL POWER SUPPLY MANAGEMENT CKT, PBGA71 PDF资料下载

参数资料

| 型号: | TPS65040ZQER |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 电源管理 |

| 英文描述: | 8-CHANNEL POWER SUPPLY MANAGEMENT CKT, PBGA71 |

| 封装: | 5 X 5 MM, 0.50 MM PITCH, GREEN, PLASTIC, MICRO, BGA-71 |

| 文件页数: | 66/73页 |

| 文件大小: | 1928K |

| 代理商: | TPS65040ZQER |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页当前第66页第67页第68页第69页第70页第71页第72页第73页

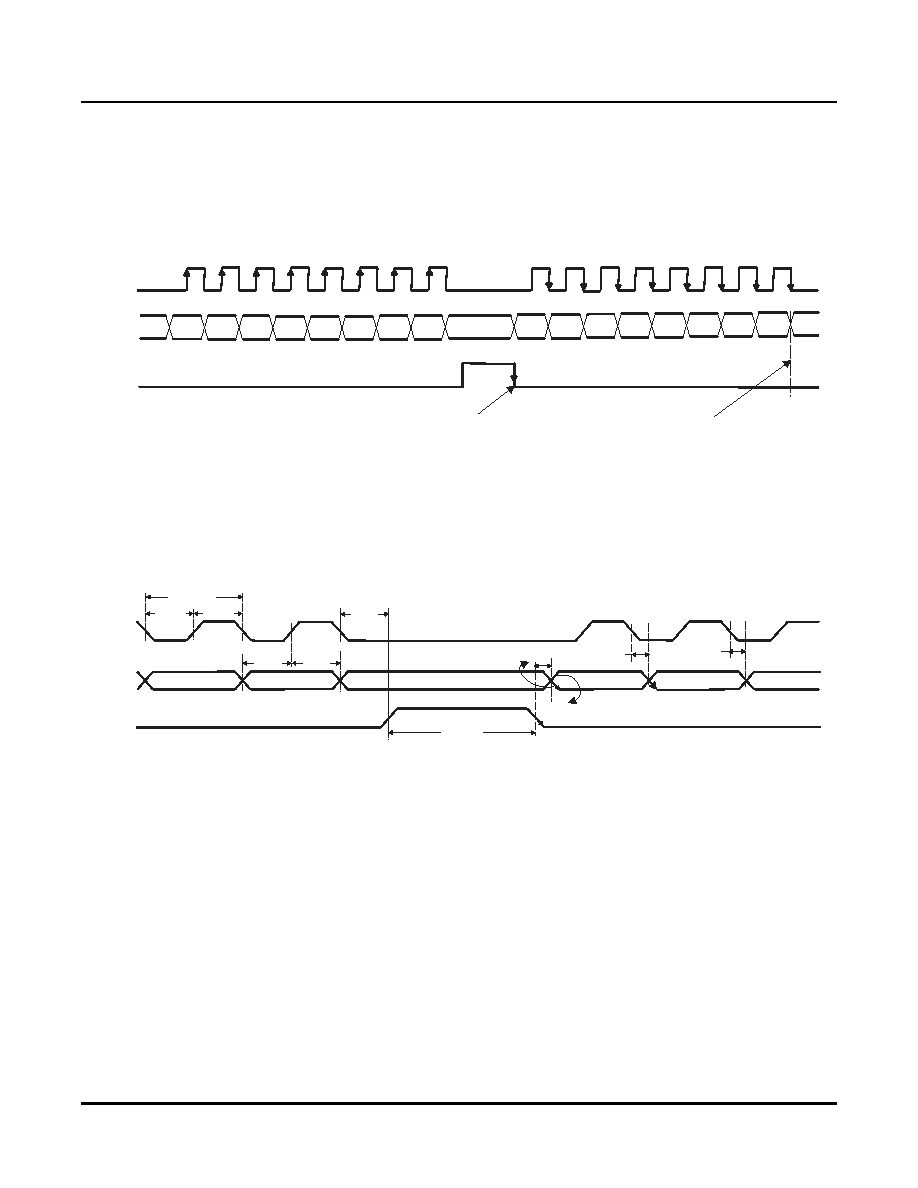

CSPI Read Operation

CDATA

CCLK

CSTB

A6

A7

A5

A4

A3

A2

A1

A0

D6

D7

D5

D4

D3

D2

D1

D0

CDATA DirectionChange

fromOutputtoInput

CDATA DirectionChange

fromInputtoOutput

1.5CCLK

tcymc

twlmc

twhmc

tDS

tDH

tSD

twhms

tpSLH

tpSHL

tpHL

tpLH

CDATA

CCLK

CSTB

TSP

SLVS708B – NOVEMBER 2006 – REVISED APRIL 2007

In a READ operation, the 8-Bit advance data becomes the address, and the next 8-Bit group becomes the

READ operation. The CSTB must be input after the address of 8-Bit advance data. CDATA pin condition

remains in input mode until the falling edge of CSTB is input. Do not input CCLK and CDATA when CSTB is

high. CDATA pin changes from the input mode to the output mode at the falling edge of CSTB. At the falling

edge of CSTB, the data from CDATA pin is output, starting from MSB data. The next data will be read one by

one at the falling edge of CCLK. CDATA pin returns from the output mode to the input mode after CCLK inputs 8

clocks.

Figure 87. CSPI Read Format

Table 25 shows a register written, RESERVED in register map of CSPI. There are both registers for

READ/WRITE. Even if data is written in the register for WRITE, the TPS65040 is not affected at all, and the

TPS65040 continues the same operation before data is written. DATA doesn't change into the state of the

output by the falling edge of CSTB, even if data is read from the READ register. The data is not output from

TPS65040, and the CDATA pin maintains the input.

Figure 88. CSPI Timing

TSP is the interface that consists of three lines (TSPDIN pin, TSPCLK pin, and TSPEN pin as input). Data

length is 16-BIT (12-BIT data, and 4-BIT address). Figure 89 shows WRITE format, while Figure 90 shows the

WRITE timing of TSP. In a WRITE operation the first 4 BITs are the address bits, followed by 12 BITs of data.

When TSPEN is low the address and data are taken by the rising edge of TSPCLK, and reflected by the rising

edge of TSPEN. The register that TSP can control becomes AFCDATA, 2GLDOCTRL, and AFCDACCTL.

69

相关PDF资料 |

PDF描述 |

|---|---|

| TPS650531IRGERQ1 | POWER SUPPLY SUPPORT CKT, PQCC24 |

| TPS650532RGET | 5-CHANNEL POWER SUPPLY SUPPORT CKT, PQCC24 |

| TPS650531RGER | 5-CHANNEL POWER SUPPLY SUPPORT CKT, PQCC24 |

| TPS65055RSMR | 1.8 A DUAL SWITCHING CONTROLLER, 2475 kHz SWITCHING FREQ-MAX, PQCC32 |

| TPS65058RGET | 1.8 A DUAL SWITCHING CONTROLLER, 2475 kHz SWITCHING FREQ-MAX, PQCC32 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TPS65050EVM-195 | 功能描述:电源管理IC开发工具 TPS65050-195 Eval Mod RoHS:否 制造商:Maxim Integrated 产品:Evaluation Kits 类型:Battery Management 工具用于评估:MAX17710GB 输入电压: 输出电压:1.8 V |

| TPS65050RSMR | 功能描述:PMIC 解决方案 6-Ch Pwr Mgmt IC RoHS:否 制造商:Texas Instruments 安装风格:SMD/SMT 封装 / 箱体:QFN-24 封装:Reel |

| TPS65050RSMRG4 | 功能描述:PMIC 解决方案 6Ch Pwr Mgmt IC RoHS:否 制造商:Texas Instruments 安装风格:SMD/SMT 封装 / 箱体:QFN-24 封装:Reel |

| TPS65050RSMT | 功能描述:PMIC 解决方案 6-Channel Power Management IC RoHS:否 制造商:Texas Instruments 安装风格:SMD/SMT 封装 / 箱体:QFN-24 封装:Reel |

| TPS65050RSMTG4 | 功能描述:PMIC 解决方案 6-Ch Pwr Mgmt IC RoHS:否 制造商:Texas Instruments 安装风格:SMD/SMT 封装 / 箱体:QFN-24 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。