- 您现在的位置:买卖IC网 > PDF目录136904 > TSC87C51-L16IEB (ATMEL CORP) 8-BIT, OTPROM, 16 MHz, MICROCONTROLLER, PQFP44 PDF资料下载

参数资料

| 型号: | TSC87C51-L16IEB |

| 厂商: | ATMEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, OTPROM, 16 MHz, MICROCONTROLLER, PQFP44 |

| 封装: | 1.40 MM HEIGHT, VQFP-44 |

| 文件页数: | 151/176页 |

| 文件大小: | 2962K |

| 代理商: | TSC87C51-L16IEB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页当前第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页

76

2535J–AVR–08/10

ATtiny13

12. Timer/Counter Prescaler

12.1 Overview

The Timer/Counter can be clocked directly by the system clock (by setting the CSn2:0 = 1). This

provides the fastest operation, with a maximum Timer/Counter clock frequency equal to system

clock frequency (fCLK_I/O). Alternatively, one of four taps from the prescaler can be used as a

clock source. The prescaled clock has a frequency of either fCLK_I/O/8, fCLK_I/O/64, fCLK_I/O/256, or

fCLK_I/O/1024.

12.2 Prescaler Reset

The prescaler is free running, i.e., operates independently of the Clock Select logic of the

Timer/Counter. Since the prescaler is not affected by the Timer/Counter’s clock select, the state

of the prescaler will have implications for situations where a prescaled clock is used. One exam-

ple of prescaling artifacts occurs when the timer is enabled and clocked by the prescaler (6 >

CSn2:0 > 1). The number of system clock cycles from when the timer is enabled to the first count

occurs can be from 1 to N+1 system clock cycles, where N equals the prescaler divisor (8, 64,

256, or 1024).

It is possible to use the Prescaler Reset for synchronizing the Timer/Counter to program

execution.

12.3 External Clock Source

An external clock source applied to the T0 pin can be used as Timer/Counter clock (clkT0). The

T0 pin is sampled once every system clock cycle by the pin synchronization logic. The synchro-

nized (sampled) signal is then passed through the edge detector. Figure 12-1 on page 76 shows

a functional equivalent block diagram of the T0 synchronization and edge detector logic. The

registers are clocked at the positive edge of the internal system clock (clk

I/O). The latch is trans-

parent in the high period of the internal system clock.

The edge detector generates one clkT0 pulse for each positive (CSn2:0 = 7) or negative (CSn2:0

= 6) edge it detects.

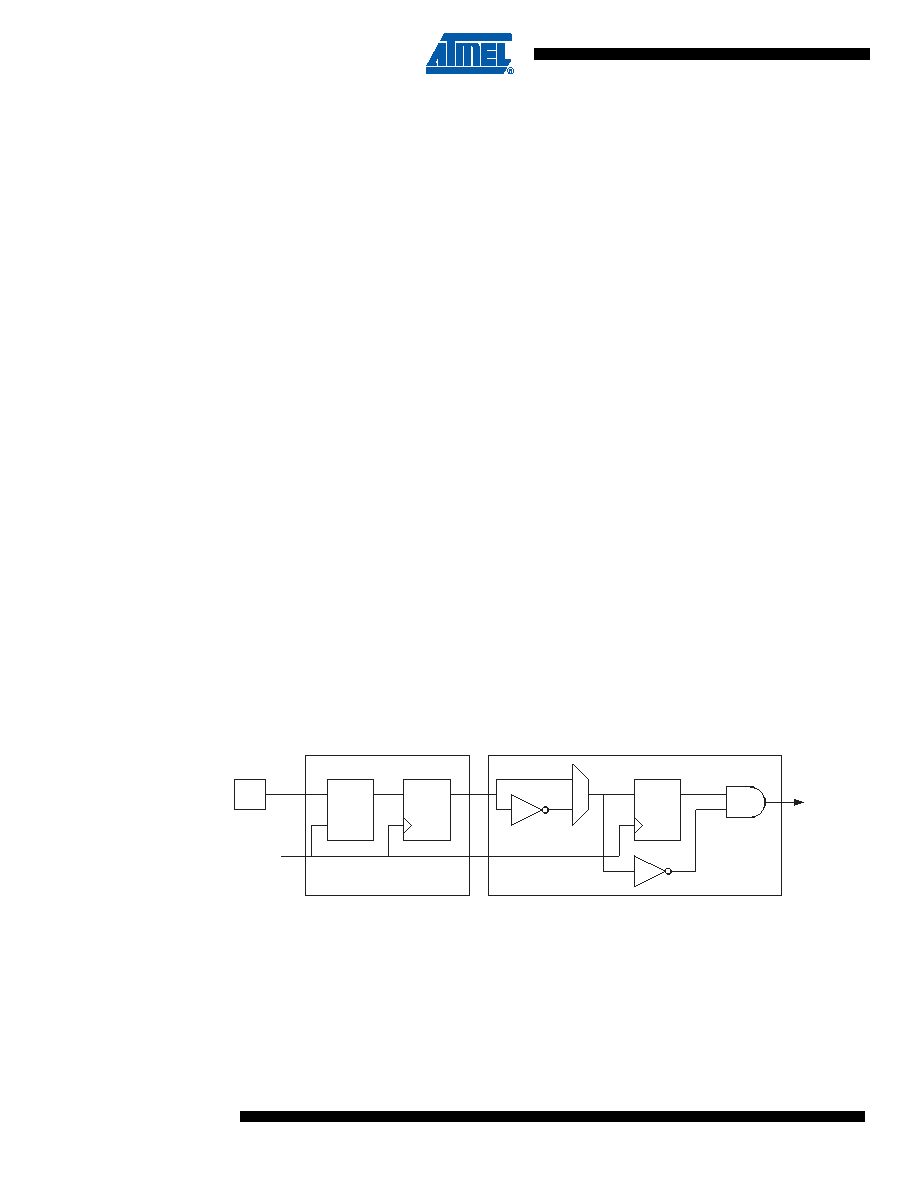

Figure 12-1. T0 Pin Sampling

The synchronization and edge detector logic introduces a delay of 2.5 to 3.5 system clock cycles

from an edge has been applied to the T0 pin to the counter is updated.

Enabling and disabling of the clock input must be done when T0 has been stable for at least one

system clock cycle, otherwise it is a risk that a false Timer/Counter clock pulse is generated.

Each half period of the external clock applied must be longer than one system clock cycle to

ensure correct sampling. The external clock must be guaranteed to have less than half the sys-

tem clock frequency (fExtClk < fclk_I/O/2) given a 50/50% duty cycle. Since the edge detector uses

Tn_sync

(To Clock

Select Logic)

Edge Detector

Synchronization

DQ

LE

DQ

Tn

clk

I/O

相关PDF资料 |

PDF描述 |

|---|---|

| TSC87C51-20CBR | 8-BIT, OTPROM, 20 MHz, MICROCONTROLLER, PQCC44 |

| TSC87C51-25CIB | 8-BIT, OTPROM, 25 MHz, MICROCONTROLLER, CQCC44 |

| TSC87C51-33CBB | 8-BIT, OTPROM, 33 MHz, MICROCONTROLLER, PQCC44 |

| TSC87C52-33CDB | 8-BIT, OTPROM, 33 MHz, MICROCONTROLLER, PQFP44 |

| T89C51RD2-3CVCM | 8-BIT, FLASH, 40 MHz, MICROCONTROLLER, PDIP40 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TSC888AILT | 功能描述:电流灵敏放大器 Sense Amplifier 20 Gain RoHS:否 制造商:Texas Instruments 通道数量: 共模抑制比(最小值):110 dB 输入补偿电压:80 uV 电源电压-最大:5.5 V 电源电压-最小:2.7 V 电源电流:350 uA 最大工作温度:+ 125 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-16 封装:Reel |

| TSC888BILT | 功能描述:电流灵敏放大器 Sense Amplifier 50 Gain RoHS:否 制造商:Texas Instruments 通道数量: 共模抑制比(最小值):110 dB 输入补偿电压:80 uV 电源电压-最大:5.5 V 电源电压-最小:2.7 V 电源电流:350 uA 最大工作温度:+ 125 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-16 封装:Reel |

| TSC888CILT | 功能描述:电流灵敏放大器 Sense Amplifier 100 Gain RoHS:否 制造商:Texas Instruments 通道数量: 共模抑制比(最小值):110 dB 输入补偿电压:80 uV 电源电压-最大:5.5 V 电源电压-最小:2.7 V 电源电流:350 uA 最大工作温度:+ 125 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-16 封装:Reel |

| TSC9 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:EURO TERMINAL BLOCKS |

| TSC903 | 制造商:Laird Technologies Inc 功能描述:CLIP TO-3P 制造商:Laird Technologies Inc 功能描述:CLIP, TO-3P 制造商:Laird Technologies Inc 功能描述:CLIP, TO-3P; External Width:6.5mm; SVHC:No SVHC (18-Jun-2012); Isolation Voltage:1kV; Length:30mm; Material:Steel; Package / Case:TO-3P, TO-218, TO-247; Packages Cooled:TO-3P, TO-218, TO-247; Pad Thickness Max:0.5mm; Panel Thickness ;RoHS Compliant: Yes 制造商:Laird Technologies Inc 功能描述:CLIP, TO-3P; External Width:6.5mm; SVHC:No SVHC (18-Jun-2012); Isolation Voltage:1kV; Length:30mm; Material:Steel; Package / Case:TO-3P, TO-218, TO-247; Packages Cooled:TO-218, TO-247, TO-3P; Pad Thickness Max:0.5mm; Panel Thickness ;RoHS Compliant: Yes |

发布紧急采购,3分钟左右您将得到回复。