- 您现在的位置:买卖IC网 > PDF目录98307 > TVP7002PZPR (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP100 PDF资料下载

参数资料

| 型号: | TVP7002PZPR |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 消费家电 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封装: | GREEN, PLASTIC, HTQFP-100 |

| 文件页数: | 34/57页 |

| 文件大小: | 517K |

| 代理商: | TVP7002PZPR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页当前第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页

SLES206B

– MAY 2007 – REVISED MAY 2011

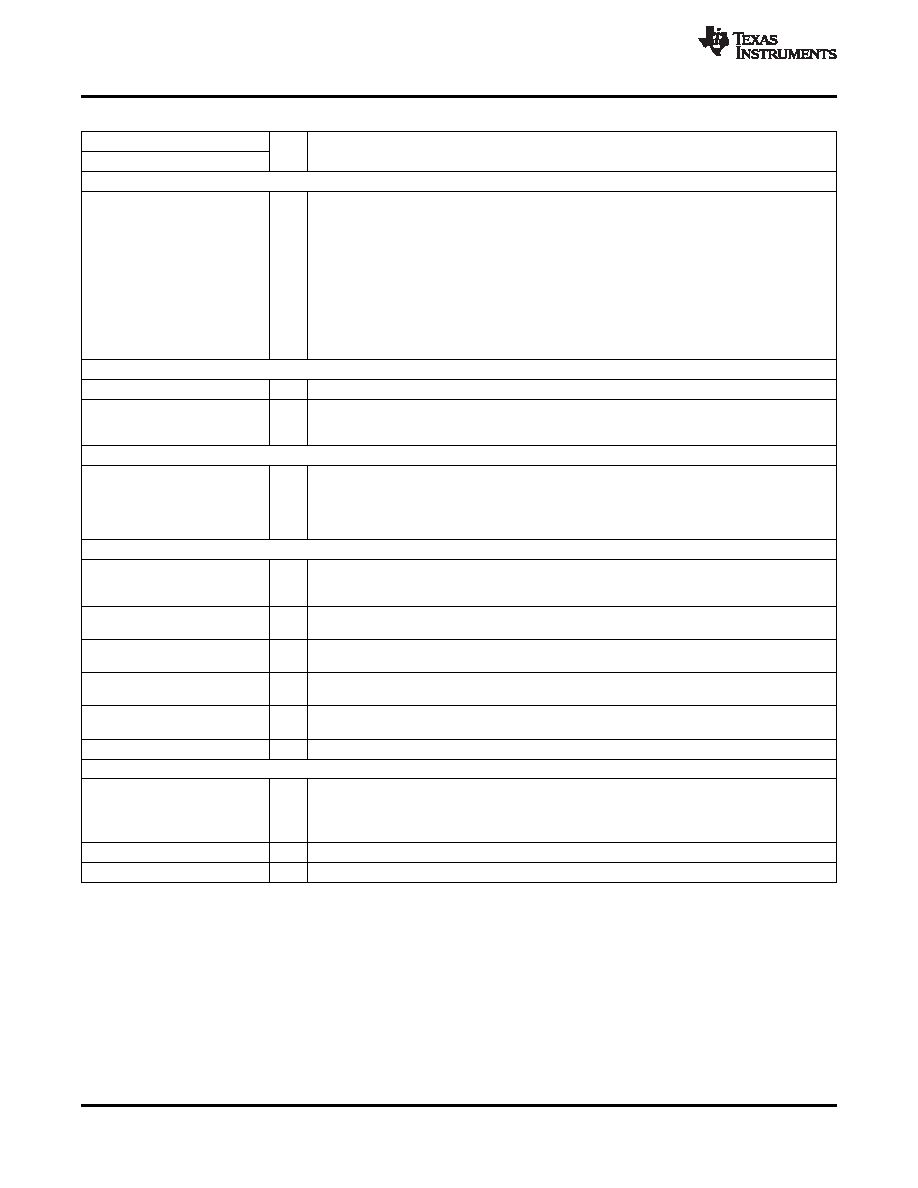

Table 1. Terminal Functions

TERMINAL

I/O

DESCRIPTION

NAME

NO.

Analog Video

RIN_1

11

I

Analog video input for R/Pr 1

RIN_2

10

I

Analog video input for R/Pr 2

RIN_3

9

I

Analog video input for R/Pr 3

GIN_1

2

I

Analog video input for G/Y 1

GIN_2

100

I

Analog video input for G/Y 2

GIN_3

98

I

Analog video input for G/Y 3

GIN_4

96

I

Analog video input for G/Y 4

BIN_1

18

I

Analog video input for B/Pb 1

BIN_2

17

I

Analog video input for B/Pb 2

BIN_3

16

I

Analog video input for B/Pb 3

The inputs must be ac coupled. The recommended coupling capacitor is 0.1

μF. Unused analog

inputs should be connected to ground using a 10-nF capacitor.

Clock Signals

DATACLK

28

O

Data clock output

EXT_CLK

80

I

External clock input. May be used as a timing reference for the mode detection block instead of

the internal clock reference. May also be used as the ADC sample clock instead of the H-PLL

generated clock.

Digital Video

R[9:0]

55

–59, 61–65

O

Digital video output of R/Cr, R[9] is the most significant bit (MSB).

G[9:0]

43-52

O

Digital video output of G/Y, G[9] is the MSB.

B[9:0]

29-38

O

Digital video output of B/Cb, B[9] is the MSB.

For 4:2:2 mode, multiplexed CbCr data is output on B[9:0].

Unused outputs can be left unconnected.

Miscellaneous Signals

PWDN

70

I

Power down input

0 = Normal mode

1 = Power down

RESETB

71

I

Reset input, active low. Outputs are placed in a high-impedance mode during reset (see

Table 11).

TMS

72

I

Test mode select input, active high. Used to enable scan test mode. For normal operation,

connect to ground.

FILT1

87

O

External filter connection for the horizontal PLL. A 0.1-

μF capacitor in series with a 1.5-k

resistor should be connected from this pin to pin 89 (see Figure 4).

FILT2

88

O

External filter connection for the horizontal PLL. A 4.7-nF capacitor should be connected from

this pin to pin 89 (see Figure 4).

PLL_F

89

I

Horizontal PLL filter internal supply connection

Host Interface

I2CA

73

I

I2C slave address input. The I2C slave address must be configured with an external pullup or

pulldown resistor (see Table 10).

0 = Slave address = B8h

1 = Slave address = BAh

SCL

74

I

I2C clock input

SDA

75

I/O

I2C data bus

4

Copyright

2007–2011, Texas Instruments Incorporated

相关PDF资料 |

PDF描述 |

|---|---|

| TVP7002PZP | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| TWL1101PFB | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TWL1101PFBR | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TWL1102PBS | SPECIALTY CONSUMER CIRCUIT, PQFP32 |

| TWL1102PBSR | SPECIALTY CONSUMER CIRCUIT, PQFP32 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TVP9000MZDSR | 制造商:Texas Instruments 功能描述: |

| TVP9000ZDS | 制造商:Texas Instruments 功能描述: |

| TVP9000ZDSR | 制造商:Texas Instruments 功能描述: |

| TVP9001ZDS | 制造商:Texas Instruments 功能描述: |

| TVP9001ZDSR | 制造商:Texas Instruments 功能描述: |

发布紧急采购,3分钟左右您将得到回复。