- 您现在的位置:买卖IC网 > PDF目录98307 > TVP7002PZPR (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP100 PDF资料下载

参数资料

| 型号: | TVP7002PZPR |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 消费家电 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封装: | GREEN, PLASTIC, HTQFP-100 |

| 文件页数: | 5/57页 |

| 文件大小: | 517K |

| 代理商: | TVP7002PZPR |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页

COAST

HSYNC

Phase

Detector

PLL Control

Register 03h

Bit [5:3]

PLL Control

Register 03h

Bit [7:6]

Phase Select

Register 04h

Bit [7:3]

Charge

Pump

VCO

Phase

Select

Divider

ADC

Sampling

CLK

External

Clock

PLL Divide

Register 01h and 02h

1:0]

Bit [1

Loop

Filter

N = 1 or 2

Post

Divider

÷N

Post Divider

Register 04h

Bit [0]

SLES206B

– MAY 2007 – REVISED MAY 2011

Automatic Level Control (ALC)

The ALC circuit maintains the level of the signal to be set at a value that is programmed at the fine offset I2C

register. It consists of a pixel averaging filter and feedback loop. This ALC function can be enabled or disabled by

the I2C register at subaddress 26h.

The ALC circuit needs a timing pulse generated internally but the user should program the position properly. The

ALC pulse must be positioned after the clamp pulse. The position of ALC pulse is controlled by ALC placement

I2C register at address 31h. This is available only for internal ALC pulse timing. When using an external clamp

pulse, the fine clamp and the ALC both start on the leading edge of the external clamp pulse. Therefore, it is

recommended to keep the external clamp pulse as long as possible.

Analog-to-Digital Converters (ADCs)

All ADCs have a resolution of 10 bits and can operate up to 165 MSPS. All A/D channels receive an identical

clock from the on-chip phase-locked loop (PLL) at a frequency between 12 MHz and 165 MHz. All ADC

reference voltages are generated internally. Also the external sampling clock can be used.

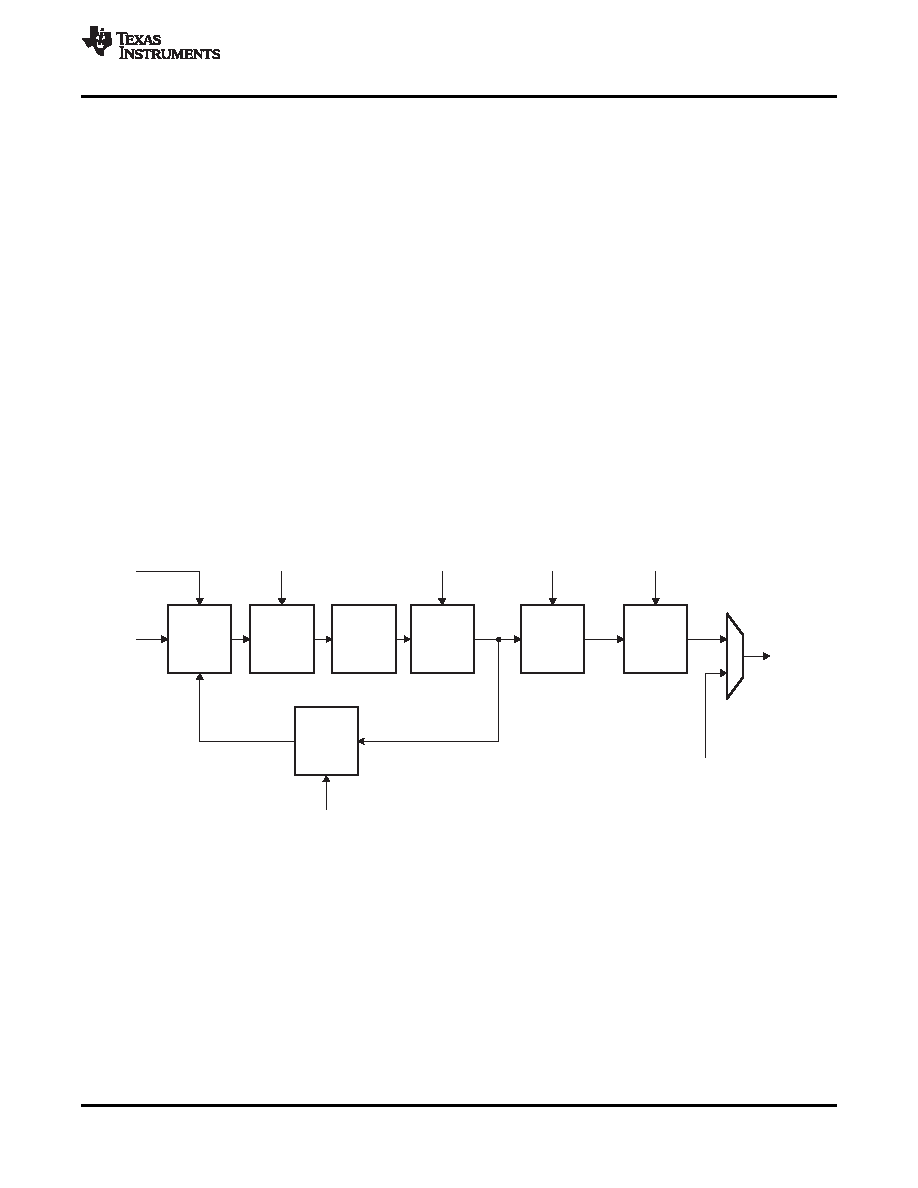

Horizontal PLL

The horizontal PLL generates a high-frequency internal clock used by the ADC sampling and data clocking out to

derive the pixel output frequency with programmable phase. The reference signal for this PLL is the horizontal

sync signal supplied on the HSYNC input or from extracted horizontal sync of the sync slicer block for embedded

sync signals. The horizontal PLL consists of a phase detector, charge pump, loop filter, voltage controlled

oscillator (VCO), phase select, feedback divider, and post divider. The horizontal PLL block diagram is shown in

Figure 3. Horizontal PLL Block Diagram

The COAST signal is used to allow the PLL to keep running at the same frequency, in the absence of the

incoming HSYNC signal or disordered HSYNC period. This is useful during the vertical sync period, or any other

time that the HSYNC is not available.

There are several PLL controls to produce the correct sampling clock. The 12-bit feedback divider register is

programmable to select exact multiplication number to generate the pixel clock in the range of 12 MHz to

165 MHz. The 3-bit loop filter current control register is to control the charge pump current that drives the

low-pass loop filter. The applicable current values are listed in the Table 4.

Copyright

2007–2011, Texas Instruments Incorporated

13

相关PDF资料 |

PDF描述 |

|---|---|

| TVP7002PZP | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| TWL1101PFB | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TWL1101PFBR | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TWL1102PBS | SPECIALTY CONSUMER CIRCUIT, PQFP32 |

| TWL1102PBSR | SPECIALTY CONSUMER CIRCUIT, PQFP32 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TVP9000MZDSR | 制造商:Texas Instruments 功能描述: |

| TVP9000ZDS | 制造商:Texas Instruments 功能描述: |

| TVP9000ZDSR | 制造商:Texas Instruments 功能描述: |

| TVP9001ZDS | 制造商:Texas Instruments 功能描述: |

| TVP9001ZDSR | 制造商:Texas Instruments 功能描述: |

发布紧急采购,3分钟左右您将得到回复。