- 您现在的位置:买卖IC网 > PDF目录20614 > USB-EA-CONVZ (Analog Devices Inc)SUPPORT BOARD ADUC8XX PDF资料下载

参数资料

| 型号: | USB-EA-CONVZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 44/68页 |

| 文件大小: | 0K |

| 描述: | SUPPORT BOARD ADUC8XX |

| 标准包装: | 1 |

| 类型: | 仿真器 |

| 适用于相关产品: | ADuC8xx |

| 所含物品: | 模块 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页当前第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

REV. B

ADuC824

–49–

SPIDAT

SPI Data Register

Function

The SPIDAT SFR is written by the user to transmit data over the SPI interface or read by user

code to read data just received by the SPI interface.

SFR Address

F7H

Power-On Default Value

00H

Bit Addressable

No

Using the SPI Interface

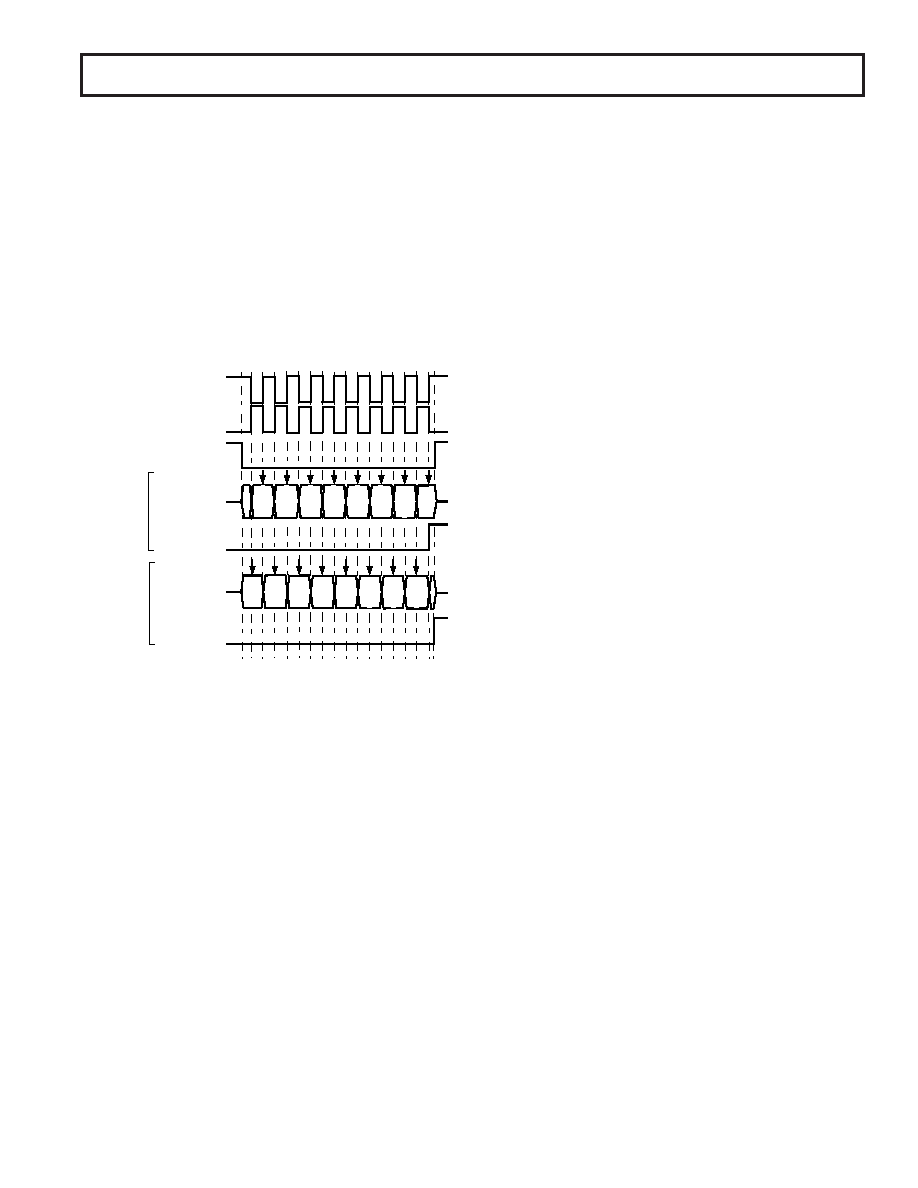

Depending on the configuration of the bits in the SPICON SFR

shown in Table XIX, the ADuC824 SPI interface will transmit

or receive data in a number of possible modes. Figure 33 shows

all possible ADuC824 SPI configurations and the timing rela-

tionships and synchronization between the signals involved.

Also shown in this figure is the SPI interrupt bit (ISPI) and how

it is triggered at the end of each byte-wide communication.

SCLOCK

(CPOL = 1)

SCLOCK

(CPOL = 0)

(CPHA = 1)

(CPHA = 0)

SAMPLE INPUT

DATA OUTPUT

ISPI FLAG

SAMPLE INPUT

DATA OUTPUT

?

MSB BIT 6 BIT 5

?

BIT 4 BIT 3 BIT 2 BIT 1 LSB

MSB

BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 LSB

SS

ISPI FLAG

Figure 33. SPI Timing, All Modes

SPI Interface—Master Mode

In master mode, the SCLOCK pin is always an output and gener-

ates a burst of eight clocks whenever user code writes to the

SPIDAT register. The SCLOCK bit rate is determined by

SPR0 and SPR1 in SPICON. It should also be noted that the

SS pin is not used in master mode. If the ADuC824 needs to

assert the

SS pin on an external slave device, a Port digital output

pin should be used.

In master mode a byte transmission or reception is initiated

by a write to SPIDAT. Eight clock periods are generated via the

SCLOCK pin and the SPIDAT byte being transmitted via MOSI.

With each SCLOCK period a data bit is also sampled via MISO.

After eight clocks, the transmitted byte will have been completely

transmitted and the input byte will be waiting in the input shift

register. The ISPI flag will be set automatically and an interrupt

will occur if enabled. The value in the shift register will be latched

into SPIDAT.

SPI Interface—Slave Mode

In slave mode the SCLOCK is an input. The

SS pin must

also be driven low externally during the byte communication.

Transmission is also initiated by a write to SPIDAT. In slave

mode, a data bit is transmitted via MISO and a data bit is received

via MOSI through each input SCLOCK period. After eight clocks,

the transmitted byte will have been completely transmitted and the

input byte will be waiting in the input shift register. The ISPI flag

will be set automatically and an interrupt will occur if enabled.

The value in the shift register will be latched into SPIDAT only

when the transmission/reception of a byte has been completed.

The end of transmission occurs after the eighth clock has been

received, if CPHA = 1 or when

SS returns high if CPHA = 0.

相关PDF资料 |

PDF描述 |

|---|---|

| RGP10KE-E3/54 | DIODE GPP 1A 800V 500NS DO-41 |

| A7NXB-1506G | CABLE D-SUB - AMN15B/AE15G/X |

| C1005C0G1H470J | CAP CER 47PF 50V 5% NP0 0402 |

| SLF6045T-220M1R1-3PF | INDUCTOR POWER 22UH 1.1A SMD |

| GBM12DRTI-S13 | CONN EDGECARD 24POS .156 EXTEND |

相关代理商/技术参数 |

参数描述 |

|---|---|

| USB-ETH ADAPTER | 制造商:DANAHER - FLUKE 功能描述:USB TO 10/100MBPS ETHERNET ADAPTER |

| USB-ETHERNET-AX88772B | 制造商:Olimex 功能描述:USB ETH ADAPTOR OLINUXINO |

| USB-EVAL | 功能描述:界面开发工具 USB products evalua- tion board unpopultd RoHS:否 制造商:Bourns 产品:Evaluation Boards 类型:RS-485 工具用于评估:ADM3485E 接口类型:RS-485 工作电源电压:3.3 V |

| USBEX02 | 制造商:Distributed By MCM 功能描述:15' USB 2.0 Active Extension Cable |

| USBEXT-150 | 制造商:DigitHead Inc 功能描述:USB EXTENDER 150' |

发布紧急采购,3分钟左右您将得到回复。