- 您现在的位置:买卖IC网 > PDF目录20614 > USB-EA-CONVZ (Analog Devices Inc)SUPPORT BOARD ADUC8XX PDF资料下载

参数资料

| 型号: | USB-EA-CONVZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 49/68页 |

| 文件大小: | 0K |

| 描述: | SUPPORT BOARD ADUC8XX |

| 标准包装: | 1 |

| 类型: | 仿真器 |

| 适用于相关产品: | ADuC8xx |

| 所含物品: | 模块 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页当前第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

REV. B

ADuC824

–53–

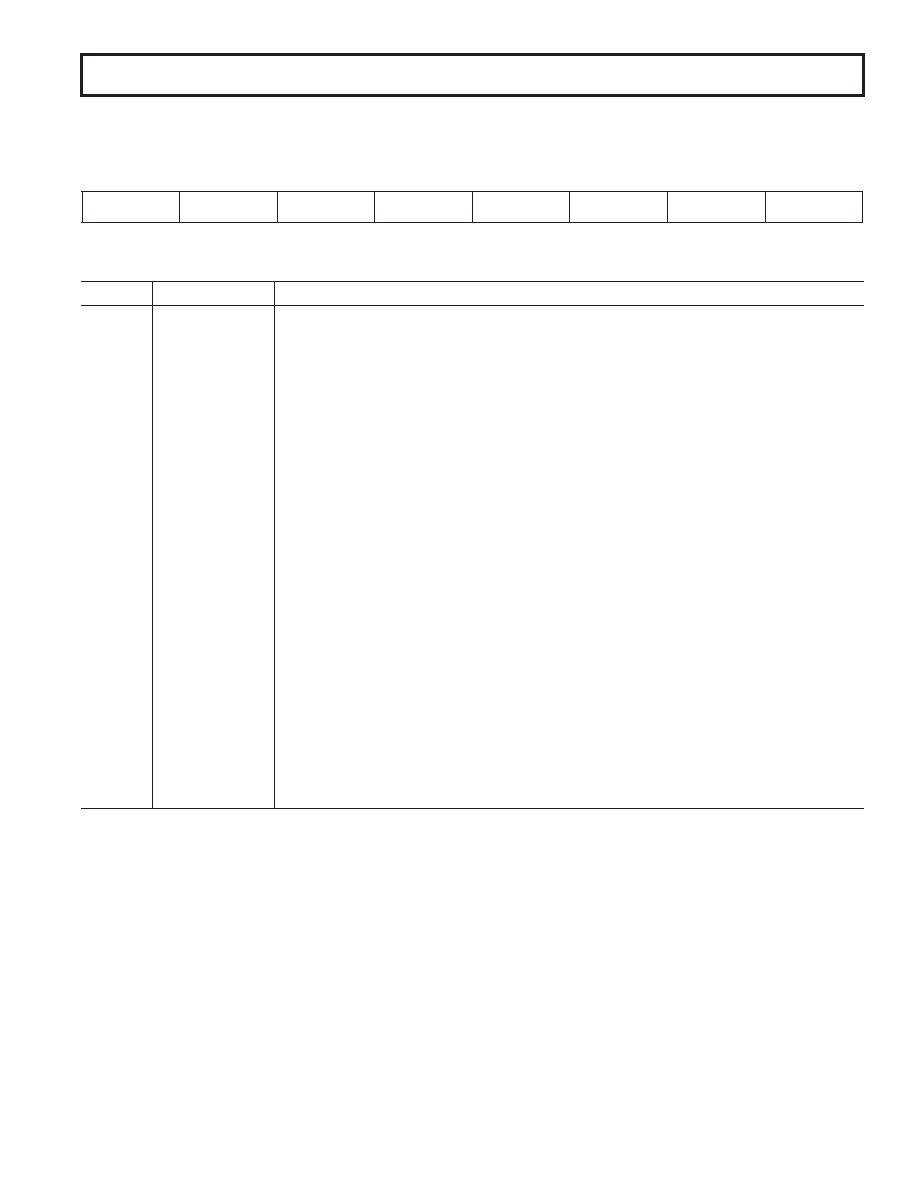

TCON

Timer/Counter 0 and 1 Control Register

SFR Address

88H

Power-On Default Value

00H

Bit Addressable

Yes

1

F

T1

R

T0

F

T0

R

T1

E

I

*

1

T

I

*

0

E

I

*

0

T

I

*

*These bits are not used in the control of timer/counter 0 and 1, but are used instead in the control and monitoring of the external INT0 and INT1 interrupt pins.

Table XXIV. TCON SFR Bit Designations

Bit

Name

Description

7

TF1

Timer 1 Overflow Flag

Set by hardware on a timer/counter 1 overflow.

Cleared by hardware when the Program Counter (PC) vectors to the interrupt service routine.

6

TR1

Timer 1 Run Control Bit

Set by user to turn on timer/counter 1.

Cleared by user to turn off timer/counter 1.

5

TF0

Timer 0 Overflow Flag

Set by hardware on a timer/counter 0 overflow.

Cleared by hardware when the PC vectors to the interrupt service routine.

4

TR0

Timer 0 Run Control Bit

Set by user to turn on timer/counter 0.

Cleared by user to turn off timer/counter 0.

3

IE1

External Interrupt 1 (

INT1) Flag

Set by hardware by a falling edge or zero level being applied to external interrupt pin

INT1, depending

on bit IT1 state.

Cleared by hardware when the when the PC vectors to the interrupt service routine only if the interrupt

was transition-activated. If level-activated, the external requesting source controls the request flag,

rather than the on-chip hardware.

2

IT1

External Interrupt 1 (IE1) Trigger Type

Set by software to specify edge-sensitive detection (i.e., 1-to-0 transition).

Cleared by software to specify level-sensitive detection (i.e., zero level).

1

IE0

External Interrupt 0 (

INT0) Flag

Set by hardware by a falling edge or zero level being applied to external interrupt pin

INT0, depending

on bit IT0 state.

Cleared by hardware when the PC vectors to the interrupt service routine only if the interrupt was

transition-activated. If level-activated, the external requesting source controls the request flag,

rather than the on-chip hardware.

0

IT0

External Interrupt 0 (IE0) Trigger Type

Set by software to specify edge-sensitive detection (i.e., 1-to-0 transition).

Cleared by software to specify level-sensitive detection (i.e., zero level).

Timer/Counter 0 and 1 Data Registers

Each timer consists of two 8-bit registers. These can be used as independent registers or combined to be a single 16-bit register

depending on the timer mode configuration.

TH0 and TL0

Timer 0 high byte and low byte.

SFR Address = 8Chex, 8Ahex respectively.

TH1 and TL1

Timer 1 high byte and low byte.

SFR Address = 8Dhex, 8Bhex respectively.

相关PDF资料 |

PDF描述 |

|---|---|

| RGP10KE-E3/54 | DIODE GPP 1A 800V 500NS DO-41 |

| A7NXB-1506G | CABLE D-SUB - AMN15B/AE15G/X |

| C1005C0G1H470J | CAP CER 47PF 50V 5% NP0 0402 |

| SLF6045T-220M1R1-3PF | INDUCTOR POWER 22UH 1.1A SMD |

| GBM12DRTI-S13 | CONN EDGECARD 24POS .156 EXTEND |

相关代理商/技术参数 |

参数描述 |

|---|---|

| USB-ETH ADAPTER | 制造商:DANAHER - FLUKE 功能描述:USB TO 10/100MBPS ETHERNET ADAPTER |

| USB-ETHERNET-AX88772B | 制造商:Olimex 功能描述:USB ETH ADAPTOR OLINUXINO |

| USB-EVAL | 功能描述:界面开发工具 USB products evalua- tion board unpopultd RoHS:否 制造商:Bourns 产品:Evaluation Boards 类型:RS-485 工具用于评估:ADM3485E 接口类型:RS-485 工作电源电压:3.3 V |

| USBEX02 | 制造商:Distributed By MCM 功能描述:15' USB 2.0 Active Extension Cable |

| USBEXT-150 | 制造商:DigitHead Inc 功能描述:USB EXTENDER 150' |

发布紧急采购,3分钟左右您将得到回复。