- 您现在的位置:买卖IC网 > PDF目录202172 > V58C2256404SHUR5 (PROMOS TECHNOLOGIES INC) 64M X 4 DDR DRAM, PBGA60 PDF资料下载

参数资料

| 型号: | V58C2256404SHUR5 |

| 厂商: | PROMOS TECHNOLOGIES INC |

| 元件分类: | DRAM |

| 英文描述: | 64M X 4 DDR DRAM, PBGA60 |

| 封装: | ROHS COMPLIANT, MO-233, FBGA-60 |

| 文件页数: | 17/60页 |

| 文件大小: | 1125K |

| 代理商: | V58C2256404SHUR5 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

24

V58C2256(804/404/164)SH Rev. 1.1 July 2010

ProMOS TECHNOLOGIES

V58C2256(804/404/164)SH

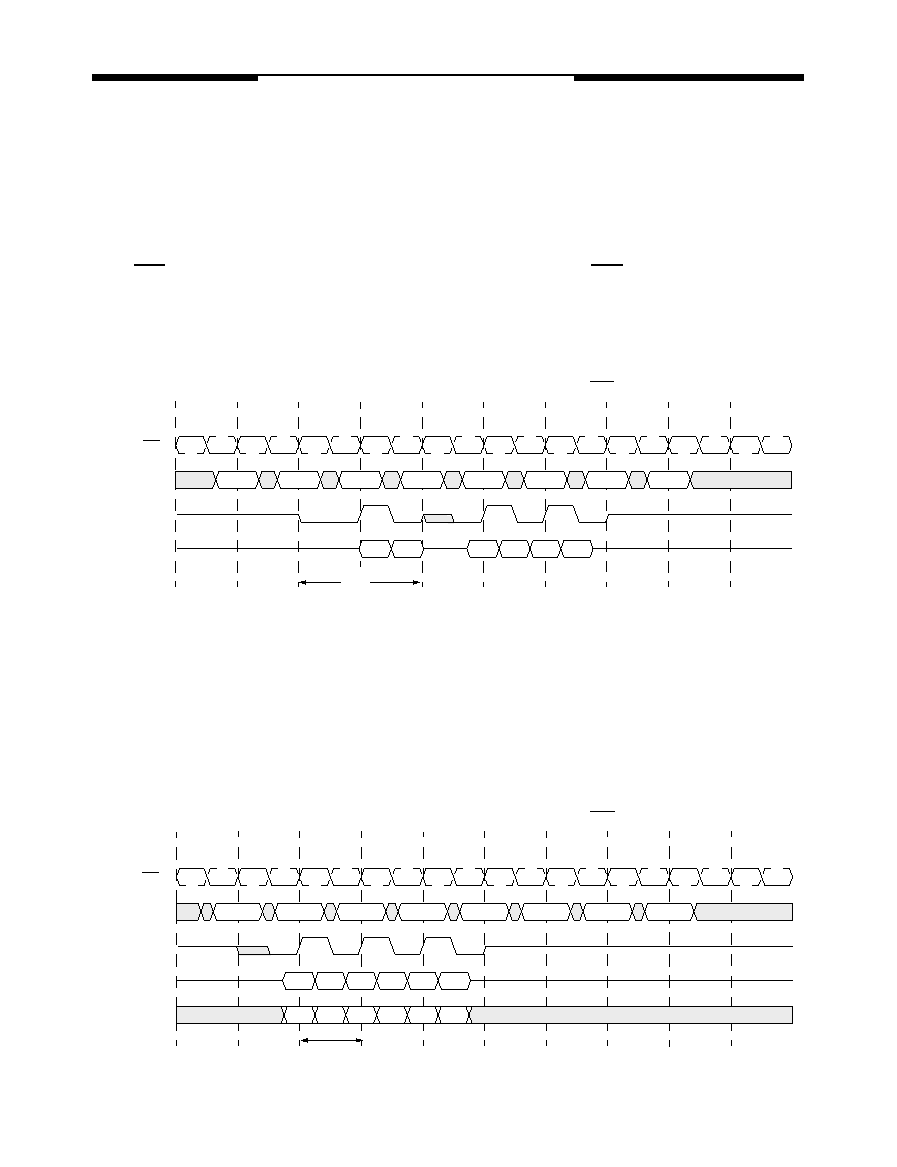

Read Interrupted by a Write

To interrupt a Burst Read with a Write command, a Burst Stop command must be asserted to stop the burst

read operation and 3-state the DQ bus. Additionally, control of the DQS bus must be turned around to allow

the memory controller to drive the data strobe signal (DQS) into the DDR SDRAM for the write cycles. Once

the Burst Stop command has been issued, a Write command can not be issued until a minimum delay or

latency (LBST) has been satisfied. This latency is measured from the Burst Stop command and is equivalent

to the CAS latency programmed into the mode register. In instances where CAS latency is measured in half

clock cycles, the minimum delay (LBST) is rounded up to the next full clock cycle (i.e., if CL=2 then LBST=2, if

CL=2.5 then LBST=3). It is illegal to interrupt a Read with autoprecharge command with a Write command.

Read Interrupted by Burst Stop Command Followed by a Write Command Timing

Write Interrupted by a Write

A Burst Write can be interrupted before completion by a new Write command to any bank. When the pre-

vious burst is interrupted, the remaining addresses are overridden with a full burst length starting with the new

address. The data from the first Write command continues to be input into the device until the Write Latency

of the interrupting Write command is satisfied (WL=1) At this point, the data from the interrupting Write com-

mand is input into the device. Write commands can be issued on each rising edge of the system clock. It is

illegal to interrupt a Write with autoprecharge command with a Write command.

Write Interrupted by a Write Command Timing

(CAS Latency = 2; Burst Length = 4)

T0

T1

T2

T3

T4

T5

T6

T7

T8

BST

NOP

Write

NOP

D0

D1

Read

D0

D1

D2

D3

CK, CK

Command

DQS

DQ

T9

LBST

(CAS Latency = Any; Burst Length = 4)

T0

T1

T2

T3

T4

T5

T6

T7

T8

WriteA

NOP

WriteB

NOP

DA0 DA1 DB0 DB1 DB2 DB3

CK, CK

Command

DQS

DQ

DM

T9

Write Latency

DM0 DM1 DM0 DM1 DM2 DM3

相关PDF资料 |

PDF描述 |

|---|---|

| V58C2256804SHLI4I | 32M X 8 DDR DRAM, PDSO66 |

| V58C2256804SHLJ6E | 32M X 8 DDR DRAM, PBGA60 |

| V58C2256804SHLS6I | 32M X 8 DDR DRAM, PBGA60 |

| V58C2256804SHLT6E | 32M X 8 DDR DRAM, PDSO66 |

| V58C2256804SHUD6E | 32M X 8 DDR DRAM, PDSO66 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| V58C2256804S | 制造商:MOSEL 制造商全称:MOSEL 功能描述:HIGH PERFORMANCE 2.5 VOLT 256 Mbit DDR SDRAM |

| V58C2256804SAT-5 | 制造商:Mosel Vitelic Corporation 功能描述:SDRAM, DDR, 32M x 8, 66 Pin, Plastic, TSSOP |

| V58C265164S | 制造商:MOSEL 制造商全称:MOSEL 功能描述:64 Mbit DDR SDRAM 2.5 VOLT 4M X 16 |

| V58C265404S | 制造商:MOSEL 制造商全称:MOSEL 功能描述:HIGH PERFORMANCE 2.5 VOLT 16M X 4 DDR SDRAM 4 BANKS X 4Mbit X 4 |

| V58C265804S | 制造商:MOSEL 制造商全称:MOSEL 功能描述:HIGH PERFORMANCE 2.5 VOLT 8M X 8 DDR SDRAM 4 BANKS X 2Mbit X 8 |

发布紧急采购,3分钟左右您将得到回复。