- 您现在的位置:买卖IC网 > Datasheet目录536 > X9470V24I (Intersil)IC BIAS CTRLR RF PA 24-TSSOP Datasheet资料下载

参数资料

| 型号: | X9470V24I |

| 厂商: | Intersil |

| 文件页数: | 14/24页 |

| 文件大小: | 0K |

| 描述: | IC BIAS CTRLR RF PA 24-TSSOP |

| 标准包装: | 62 |

| RF 型: | CDMA,GSM,EDGE |

| 封装/外壳: | 24-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 24-TSSOP 裸露焊盘 |

�� �

�

�

�X9470�

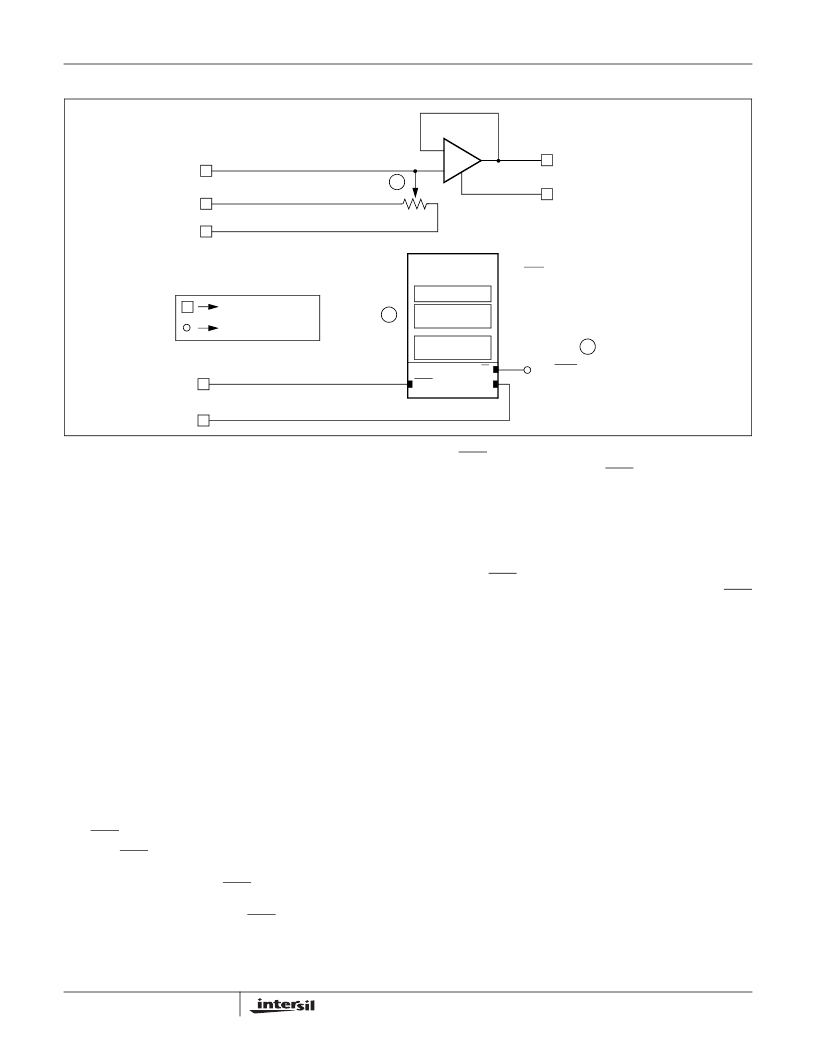

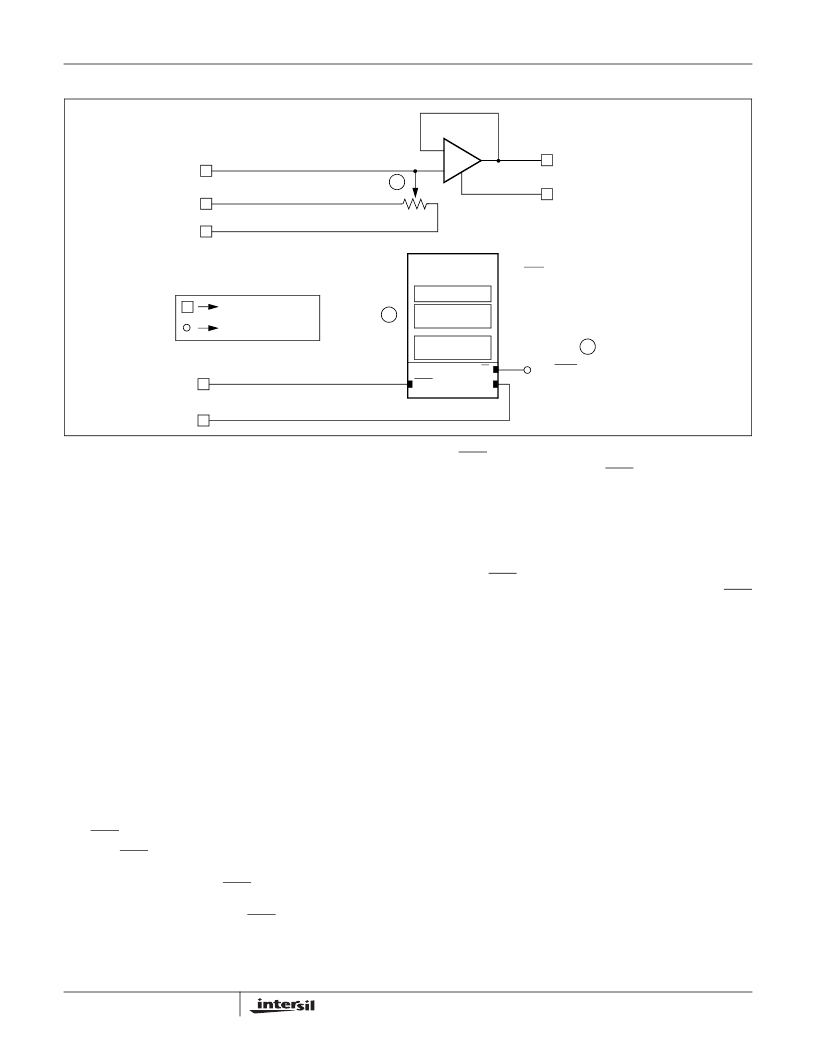

�Figure� 3.� Bias� Adjustment� Block� Diagram�

�V� BIAS� (unbuffered)�

�RW� BIAS�

�RH� BIAS�

�RL� BIAS�

�2�

�Gate� Bias�

�Op� Amp�

�–�

�+�

�R� BIAS�

�10k� ?�

�256-tap�

�V� BIAS�

�to� LDMOS� gate�

�SHDN�

�Legend�

�External� pin/signal�

�Internal� node/signal�

�3�

�XDCP�

�Memory� and� Control�

�WCR� (Rbias)�

�Bias� Register�

�non-volatile�

�INC/DEC� is� logic� HIGH� or� LOW�

�from� Sense/Scale� Block�

�and� is� used� to� increment� or�

�decrement� the� Rbias� resistor�

�(XDCP)� to� adjust� the� gate� voltage.�

�Power-On� Recall�

�(POR)�

�U/D�

�INC/DEC�

�1�

�SCL�

�INC�

�CS�

�Note:�

�1)� WCR� =� Wiper� Control� Register�

�CS�

�NON-VOLATILE� STORE� OF� THE� BIAS� POSITION�

�The� following� procedure� will� store� the� values� for� the�

�Rref� and� Rbias� wiper� positions� in� Non-Volatile� mem-�

�ory.� This� sequence� is� intended� to� be� performed� after� a�

�BiasLock� calibration� sequence� to� simplify� storage.� If�

�BiasLock� has� not� been� achieved,� then� the� Rbias� wiper�

�position� may� change� when� the� CS� pin� is� brought� high�

�and� SCL� begins� clocking.� See� Figure� 4� for� the� actual�

�sequence.�

�1.� Set� the� WEL� bit� with� a� write� command� (02h� to� reg-�

�ister� 0Fh)�

�2.� Peform� a� calibration� and� achieve� BiasLock.� Leave�

�CS� pin� high.�

�3.� Write� the� address� byte� only� (START,� followed� by�

�device/slave� address� and� a� 0� for� a� write,� see� page�

�19).�

�4.� Perform� a� STOP� command.�

�5.� With� SCL� still� low,� bring� the� CS� low.� The� falling�

�edge� of� the� CS� will� initiate� the� NV� write.�

�The� WEL� bit� may� be� reset� afterwards� to� prevent� fur-�

�ther� NV� writes.�

�INC/DEC� FUNCTION�

�The� INC/DEC� pin� is� an� open-drain� logic� output� that�

�tracks� the� activity� of� the� increment/decrement� compar-�

�ator.� A� logic� HIGH� at� INC/DEC� indicates� that� the� I� DQ�

�did� not� rise� up� to� the� desired� setting� indicated� by� V� REF�

�while� a� logic� LOW� at� the� INC/DEC� pin� indicates� that�

�the� IDQ� is� higher� than� the� desired� setting.�

�14�

�INC/DEC� is� used� as� an� internal� control� signal� as� well.�

�As� an� example,� when� INC/DEC� is� LOW,� the� Bias�

�Adjustment� Circuit� Block� will� start� to� move� the� Rbias�

�resistor� wiper� towards� the� RL� BIAS� terminal� end� when�

�CS� is� HIGH� and� SCL� is� clocking.� Consequently,� the�

�V� BIAS� voltage� will� decrease,� and� the� I� DQ� decreases� to�

�meet� the� desired� V� REF� setting.�

�The� INC/DEC� signal� can� also� be� used� to� detect� a�

�damaged� RF� power� FET.� For� instance,� If� INC/DEC�

�stays� HIGH� during� and� after� a� calibration� sequence� it�

�may� indicate� that� the� RF� power� FET� has� failed.� This�

�indicator� can� also� be� used� with� a� level� sense� on� the�

�V� OUT� pin� to� perform� diagnostics.�

�SHUTDOWN� MECHANISM�

�This� hardware� control� shutdown� pin� (SHDN)� will� pull�

�the� voltage� of� V� BIAS� to� VSS� with� an� internal� pull� down�

�resistor.� When� shutdown� is� disabled� (V� BIAS� is� active�

�when� SHDN� is� LOW),� the� V� BIAS� voltage� will� move� to�

�the� previous� desired� bias� voltage.�

�It� will� take� less� than� a� microsecond� to� enable� the� inter-�

�nal� output� buffer� depending� on� the� loading� condition� at�

�the� V� BIAS� pin.�

�OUTPUT� (V� BIAS� )�

�V� BIAS� is� a� buffered� output� of� RW� BIAS� (wiper� output).� It�

�can� deliver� a� high� current� for� driving� up� to� typically� 1nF�

�capacitive� loading� with� stable� performance� and� fast�

�settling� time.�

�FN8204.0�

�March� 8,� 2005�

�相关PDF资料 |

PDF描述 |

|---|---|

| XB24-DMDK | DIGIMESH 2.4 DEV KIT |

| XB24-PDK | KIT DEV PRO ZIGBEE |

| XBP09-DMUIT-156 | XBEE-PROMESH 900 RANGE |

| XBP24-AUI-080 | MODULE 802.15.4 100MW U.FL CON |

| XBP24-PKI-001-RA | MODULE 802.15.4 RS-232 ANT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| X9483919-2 | 功能描述:环形MIL规格工具、五金与附件 RoHS:否 制造商:Amphenol Industrial MIL 类型:MIL-DTL-5015 系列:97 产品类型:Dummy Receptacles 用于:97 Series Plugs |

| X9483919-3 | 功能描述:环形MIL规格工具、五金与附件 RoHS:否 制造商:Amphenol Industrial MIL 类型:MIL-DTL-5015 系列:97 产品类型:Dummy Receptacles 用于:97 Series Plugs |

| X9483919-4 | 功能描述:环形MIL规格工具、五金与附件 RoHS:否 制造商:Amphenol Industrial MIL 类型:MIL-DTL-5015 系列:97 产品类型:Dummy Receptacles 用于:97 Series Plugs |

| X9483919-5 | 功能描述:环形MIL规格工具、五金与附件 RoHS:否 制造商:Amphenol Industrial MIL 类型:MIL-DTL-5015 系列:97 产品类型:Dummy Receptacles 用于:97 Series Plugs |

| X9483919-7 | 功能描述:环形MIL规格工具、五金与附件 RoHS:否 制造商:Amphenol Industrial MIL 类型:MIL-DTL-5015 系列:97 产品类型:Dummy Receptacles 用于:97 Series Plugs |

发布紧急采购,3分钟左右您将得到回复。