参数资料

| 型号: | XC3S50AN-4FTG256C |

| 厂商: | Xilinx Inc |

| 文件页数: | 65/123页 |

| 文件大小: | 0K |

| 描述: | IC FPGA SPARTAN-3AN 256FTBGA |

| 标准包装: | 90 |

| 系列: | Spartan®-3AN |

| LAB/CLB数: | 176 |

| 逻辑元件/单元数: | 1584 |

| RAM 位总计: | 55296 |

| 输入/输出数: | 195 |

| 门数: | 50000 |

| 电源电压: | 1.14 V ~ 1.26 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 256-LBGA |

| 供应商设备封装: | 256-FTBGA |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页当前第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页

Spartan-3AN FPGA Family: DC and Switching Characteristics

DS557 (v4.1) April 1, 2011

Product Specification

46

LVCMOS12

Slow

2

17

40

4

–13

–25

6

–10

–18

Fast

2

12

9

31

4

–9

–13

6

–9

QuietIO

2

36

55

4

–33

–36

6

–27

–36

PCI33_3

9

16

PCI66_3

–9

–13

HSTL_I

–11

–20

HSTL_III

–7

–8

HSTL_I_18

13

17

HSTL_II_18

–5

HSTL_III_18

8

10

8

SSTL18_I

7

13

7

15

SSTL18_II

–9

SSTL2_I

10

18

SSTL2_II

–6

–9

SSTL3_I

7

8

10

SSTL3_II

5

6

7

Differential Standards (Number of I/O Pairs or Channels)

LVDS_25

8

–22

–

LVDS_33

8

–27

–

BLVDS_25

1

4

MINI_LVDS_25

8

–22

–

MINI_LVDS_33

8

–27

–

LVPECL_25

Input Only

LVPECL_33

Input Only

RSDS_25

8

–22

–

RSDS_33

8

–27

–

TMDS_33

8

–27

–

PPDS_25

8

–22

–

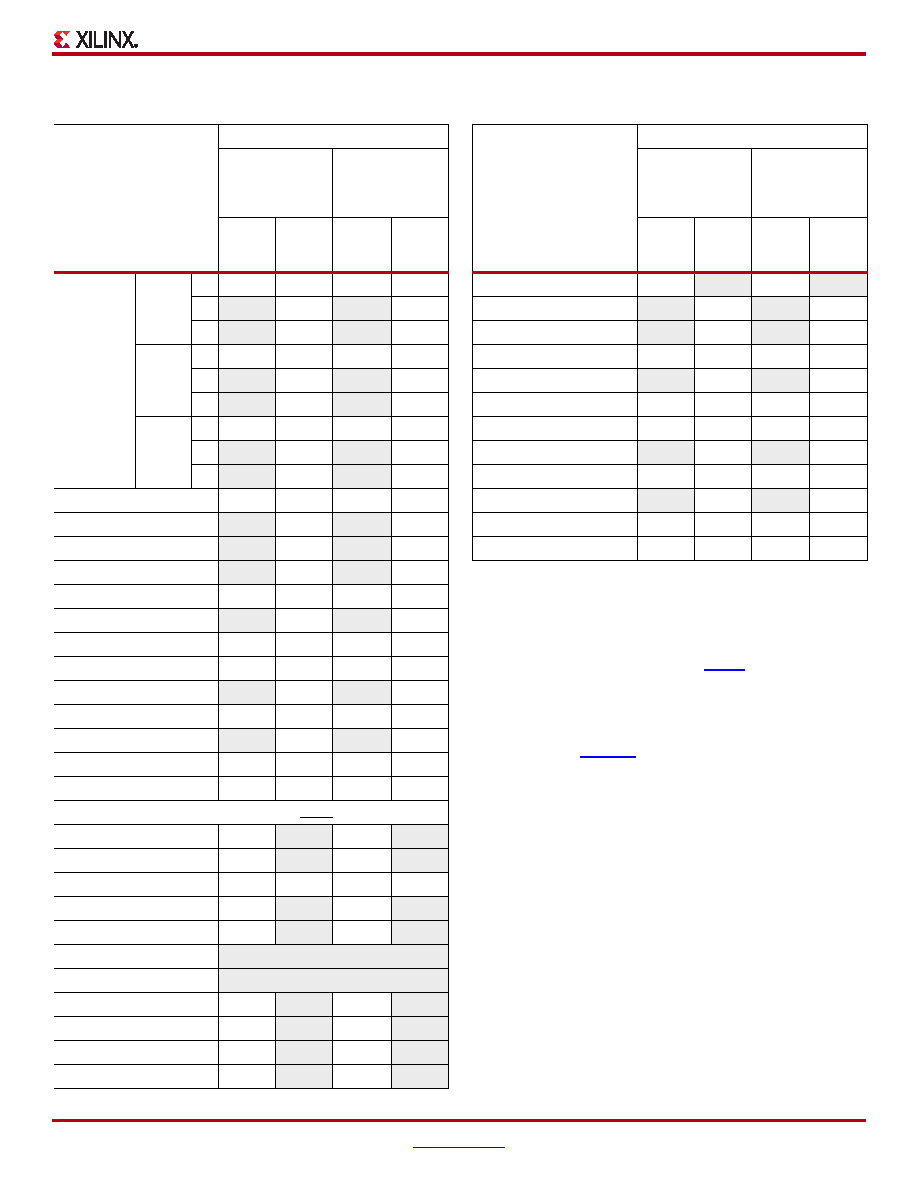

Table 32: Recommended Number of Simultaneously

Switching Outputs per VCCO-GND Pair (Cont’d)

Signal Standard

(IOSTANDARD)

Package Type

TQG144

FTG256,

FGG400,

FGG484,

FGG676

Top,

Bottom

Banks 0,2

Left,

Right

Banks 1,3

Top,

Bottom

Banks 0,2

Left,

Right

Banks 1,3

PPDS_33

8

–27

–

DIFF_HSTL_I

–5

–10

DIFF_HSTL_III

–3

–4

DIFF_HSTL_I_18

6

8

DIFF_HSTL_II_18

–2

DIFF_HSTL_III_18

4

5

4

DIFF_SSTL18_I

3

6

3

7

DIFF_SSTL18_II

–4

DIFF_SSTL2_I

5

9

DIFF_SSTL2_II

–3

–4

DIFF_SSTL3_I

3

4

5

DIFF_SSTL3_II

2

3

Notes:

1.

Not all I/O standards are supported on all I/O banks. The left and

right banks (I/O banks 1 and 3) support higher output drive

current than the top and bottom banks (I/O banks 0 and 2).

Similarly, true differential output standards, such as LVDS, RSDS,

PPDS, miniLVDS, and TMDS, are only supported in top or bottom

banks (I/O banks 0 and 2). Refer to UG331: Spartan-3

Generation FPGA User Guide for additional information.

2.

The numbers in this table are recommendations that assume

sound board lay out practice. Test limits are the VIL/VIH voltage

limits for the respective I/O standard.

3.

If more than one signal standard is assigned to the I/Os of a given

bank, refer to XAPP689: Managing Ground Bounce in Large

FPGAs for information on how to perform weighted average SSO

calculations.

Table 32: Recommended Number of Simultaneously

Switching Outputs per VCCO-GND Pair (Cont’d)

Signal Standard

(IOSTANDARD)

Package Type

TQG144

FTG256,

FGG400,

FGG484,

FGG676

Top,

Bottom

Banks 0,2

Left,

Right

Banks 1,3

Top,

Bottom

Banks 0,2

Left,

Right

Banks 1,3

相关PDF资料 |

PDF描述 |

|---|---|

| XC3S50A-5FT256C | IC SPARTAN-3A FPGA 50K 256FTBGA |

| XC3S200-4VQG100C | SPARTAN-3A FPGA 200K STD 100VQFP |

| RSM44DSAS | CONN EDGECARD 88POS R/A .156 SLD |

| RMM44DSAS | CONN EDGECARD 88POS R/A .156 SLD |

| ASM12DRES | CONN EDGECARD 24POS .156 EYELET |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC3S50AN-4FTG256I | 功能描述:IC FPGA SPARTAN-3AN 256FTBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3AN 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XC3S50AN-4TQ144I | 功能描述:IC FPGA SPARTAN 3AN 144TQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3AN 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XC3S50AN-4TQG144C | 功能描述:IC SPARTAN-3AN FPGA 50K 144TQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3AN 标准包装:60 系列:XP LAB/CLB数:- 逻辑元件/单元数:10000 RAM 位总计:221184 输入/输出数:244 门数:- 电源电压:1.71 V ~ 3.465 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:388-BBGA 供应商设备封装:388-FPBGA(23x23) 其它名称:220-1241 |

| XC3S50AN-4TQG144CES | 制造商:Xilinx 功能描述: |

| XC3S50AN-4TQG144I | 功能描述:IC FPGA SPARTAN-3AN50K 144-TQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3AN 标准包装:60 系列:XP LAB/CLB数:- 逻辑元件/单元数:10000 RAM 位总计:221184 输入/输出数:244 门数:- 电源电压:1.71 V ~ 3.465 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:388-BBGA 供应商设备封装:388-FPBGA(23x23) 其它名称:220-1241 |

发布紧急采购,3分钟左右您将得到回复。