参数资料

| 型号: | XC3S50AN-4TQ144I |

| 厂商: | Xilinx Inc |

| 文件页数: | 79/123页 |

| 文件大小: | 0K |

| 描述: | IC FPGA SPARTAN 3AN 144TQFP |

| 标准包装: | 60 |

| 系列: | Spartan®-3AN |

| LAB/CLB数: | 176 |

| 逻辑元件/单元数: | 1584 |

| RAM 位总计: | 55296 |

| 输入/输出数: | 108 |

| 门数: | 50000 |

| 电源电压: | 1.14 V ~ 1.26 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 144-LQFP |

| 供应商设备封装: | 144-TQFP(20x20) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页当前第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页

Spartan-3AN FPGA Family: DC and Switching Characteristics

DS557 (v4.1) April 1, 2011

Product Specification

59

Suspend Mode Timing

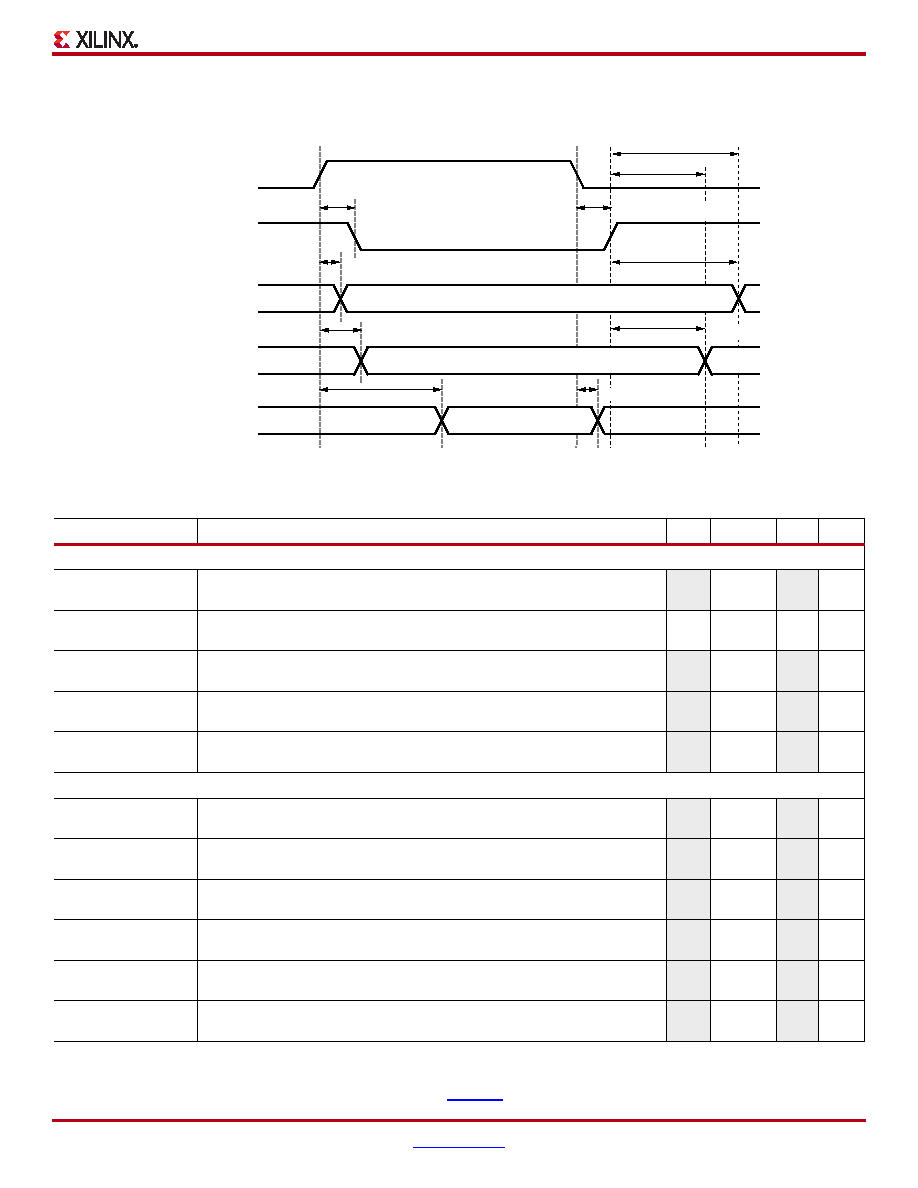

X-Ref Target - Figure 12

Figure 12: Suspend Mode Timing

Table 49: Suspend Mode Timing Parameters

Symbol

Description

Min

Typ

Max

Units

Entering Suspend Mode

TSUSPENDHIGH_AWAKE Rising edge of SUSPEND pin to falling edge of AWAKE pin without glitch filter

(suspend_filter:No)

–7

–ns

TSUSPENDFILTER

Adjustment to SUSPEND pin rising edge parameters when glitch filter enabled

(suspend_filter:Yes)

+160

+300

+600

ns

TSUSPEND_GTS

Rising edge of SUSPEND pin until FPGA output pins drive their defined

SUSPEND constraint behavior

–10

–ns

TSUSPEND_GWE

Rising edge of SUSPEND pin to write-protect lock on all writable clocked

elements

–< 5

–ns

TSUSPEND_DISABLE

Rising edge of the SUSPEND pin to FPGA input pins and interconnect

disabled

–

340

–ns

Exiting Suspend Mode

TSUSPENDLOW_AWAKE Falling edge of the SUSPEND pin to rising edge of the AWAKE pin

Does not include DCM lock time

–

4 to 108

–s

TSUSPEND_ENABLE

Falling edge of the SUSPEND pin to FPGA input pins and interconnect

re-enabled

–

3.7 to 109

–s

TAWAKE_GWE1

Rising edge of the AWAKE pin until write-protect lock released on all writable

clocked elements, using sw_clk:InternalClock and sw_gwe_cycle:1

–67

–ns

TAWAKE_GWE512

Rising edge of the AWAKE pin until write-protect lock released on all writable

clocked elements, using sw_clk:InternalClock and sw_gwe_cycle:512

–14

–s

TAWAKE_GTS1

Rising edge of the AWAKE pin until outputs return to the behavior described

in the FPGA application, using sw_clk:InternalClock and sw_gts_cycle:1

–57

–ns

TAWAKE_GTS512

Rising edge of the AWAKE pin until outputs return to the behavior described

in the FPGA application, using sw_clk:InternalClock and sw_gts_cycle:512

–14

–s

Notes:

1.

These parameters based on characterization.

2.

For information on using the Spartan-3AN Suspend feature, see XAPP480: Using Suspend Mode in Spartan-3 Generation FPGAs.

DS610-3_08_061207

Blocked

t

SUSPEND_DISABLE

t

SUSPEND_GWE

t

SUSPENDHIGH_AWAKE

t

AWAKE_GWE

t

AWAKE_GTS

t

SUSPEND_GTS

SUSPEND Input

AWAKE Output

Flip-Flops, Block RAM,

Distributed RAM

FPGA Outputs

FPGA Inputs,

Interconnect

Write Protected

Defined by SUSPEND constraint

Entering Suspend Mode

Exiting Suspend Mode

sw_gts_cycle

sw_gwe_cycle

t

SUSPEND_ENABLE

t

SUSPENDLOW_AWAKE

相关PDF资料 |

PDF描述 |

|---|---|

| 748333-2 | CONTACT, HD22 PIN, 30AU |

| 748333-5 | CONTACT, HD22 PIN, FLAU |

| 24LC024-E/MS | IC EEPROM 2KBIT 400KHZ 8MSOP |

| 24C02CT-E/MNY | IC SRL EEPROM 256KX8 V 8-TDFN |

| 24LC08BT-E/MNY | IC EEPROM 8KBIT 400KHZ 8TDFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC3S50AN-4TQG144C | 功能描述:IC SPARTAN-3AN FPGA 50K 144TQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3AN 标准包装:60 系列:XP LAB/CLB数:- 逻辑元件/单元数:10000 RAM 位总计:221184 输入/输出数:244 门数:- 电源电压:1.71 V ~ 3.465 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:388-BBGA 供应商设备封装:388-FPBGA(23x23) 其它名称:220-1241 |

| XC3S50AN-4TQG144CES | 制造商:Xilinx 功能描述: |

| XC3S50AN-4TQG144I | 功能描述:IC FPGA SPARTAN-3AN50K 144-TQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3AN 标准包装:60 系列:XP LAB/CLB数:- 逻辑元件/单元数:10000 RAM 位总计:221184 输入/输出数:244 门数:- 电源电压:1.71 V ~ 3.465 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:388-BBGA 供应商设备封装:388-FPBGA(23x23) 其它名称:220-1241 |

| XC3S50AN-4TQG144ICES | 制造商:Xilinx 功能描述: |

| XC3S50AN-5FT256C | 制造商:Xilinx 功能描述:SPARTAN3AN - Trays 制造商:Xilinx 功能描述:IC FPGA SPARTAN-3AN 50K 256BGA 制造商:Xilinx 功能描述:IC FPGA 195 I/O 256FTBGA |

发布紧急采购,3分钟左右您将得到回复。