参数资料

| 型号: | XCS40-3PQ208I |

| 厂商: | Xilinx Inc |

| 文件页数: | 17/83页 |

| 文件大小: | 0K |

| 描述: | IC FPGA 5V I-TEMP 208-PQFP |

| 产品变化通告: | Spartan,Virtex FPGA/SCD Discontinuation 18/Oct/2010 |

| 标准包装: | 24 |

| 系列: | Spartan® |

| LAB/CLB数: | 784 |

| 逻辑元件/单元数: | 1862 |

| RAM 位总计: | 25088 |

| 输入/输出数: | 169 |

| 门数: | 40000 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 208-BFQFP |

| 供应商设备封装: | 208-PQFP(28x28) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页

Spartan and Spartan-XL FPGA Families Data Sheet

24

DS060 (v2.0) March 1, 2013

Product Specification

R

Product Obsolete/Under Obsolescence

Even if the boundary scan symbol is used in a design, the

input pins TMS, TCK, and TDI can still be used as inputs to

be routed to internal logic. Care must be taken not to force

the chip into an undesired boundary scan state by inadver-

tently applying boundary scan input patterns to these pins.

The simplest way to prevent this is to keep TMS High, and

then apply whatever signal is desired to TDI and TCK.

Avoiding Inadvertent Boundary Scan

If TMS or TCK is used as user I/O, care must be taken to

ensure that at least one of these pins is held constant during

configuration. In some applications, a situation may occur

where TMS or TCK is driven during configuration. This may

cause the device to go into boundary scan mode and dis-

rupt the configuration process.

To prevent activation of boundary scan during configuration,

do either of the following:

TMS: Tie High to put the Test Access Port controller

in a benign RESET state.

TCK: Tie High or Low—do not toggle this clock input.

For more information regarding boundary scan, refer to the

Xilinx Application Note, "Boundary Scan in FPGA Devices. "

Boundary Scan Enhancements (Spartan-XL Family

Only)

Spartan-XL devices have improved boundary scan func-

tionality and performance in the following areas:

IDCODE: The IDCODE register is supported. By using the

IDCODE, the device connected to the JTAG port can be

determined. The use of the IDCODE enables selective con-

figuration dependent on the FPGA found.

The IDCODE register has the following binary format:

vvvv:ffff:fffa:aaaa:aaaa:cccc:cccc:ccc1

where

c = the company code (49h for Xilinx)

a = the array dimension in CLBs (ranges from 0Ah for

XCS05XL to 1Ch for XCS40XL)

f = the family code (02h for Spartan-XL family)

v = the die version number

Configuration State: The configuration state is available to

JTAG controllers.

Configuration Disable: The JTAG port can be prevented

from configuring the FPGA.

TCK Startup: TCK can now be used to clock the start-up

block in addition to other user clocks.

CCLK Holdoff: Changed the requirement for Boundary

Scan Configure or EXTEST to be issued prior to the release

of INIT pin and CCLK cycling.

Reissue Configure: The Boundary Scan Configure can be

reissued to recover from an unfinished attempt to configure

the device.

Bypass FF: Bypass FF and IOB is modified to provide

DRCLOCK only during BYPASS for the bypass flip-flop, and

during EXTEST or SAMPLE/PRELOAD for the IOB register.

Power-Down (Spartan-XL Family Only)

All Spartan/XL devices use a combination of efficient seg-

mented routing and advanced process technology to pro-

vide low power consumption under all conditions. The 3.3V

Spartan-XL family adds a dedicated active Low power-down

pin (PWRDWN) to reduce supply current to 100

μA typical.

The PWRDWN pin takes advantage of one of the unused

No Connect locations on the 5V Spartan device. The user

must de-select the "5V Tolerant I/Os" option in the Configu-

ration Options to achieve the specified Power Down current.

The PWRDWN pin has a default internal pull-up resistor,

allowing it to be left unconnected if unused.

VCC must continue to be supplied during Power-down, and

configuration data is maintained. When the PWRDWN pin is

pulled Low, the input and output buffers are disabled. The

inputs are internally forced to a logic Low level, including the

MODE pins, DONE, CCLK, and TDO, and all internal

pull-up resistors are turned off. The PROGRAM pin is not

affected by Power Down. The GSR net is asserted during

Power Down, initializing all the flip-flops to their start-up

state.

PWRDWN has a minimum pulse width of 50 ns (Figure 23).

On entering the Power-down state, the inputs will be dis-

abled and the flip-flops set/reset, and then the outputs are

disabled about 10 ns later. The user may prefer to assert the

GTS or GSR signals before PWRDWN to affect the order of

events. When the PWRDWN signal is returned High, the

inputs will be enabled first, followed immediately by the

release of the GSR signal initializing the flip-flops. About 10

ns later, the outputs will be enabled. Allow 50 ns after the

release of PWRDWN before using the device.

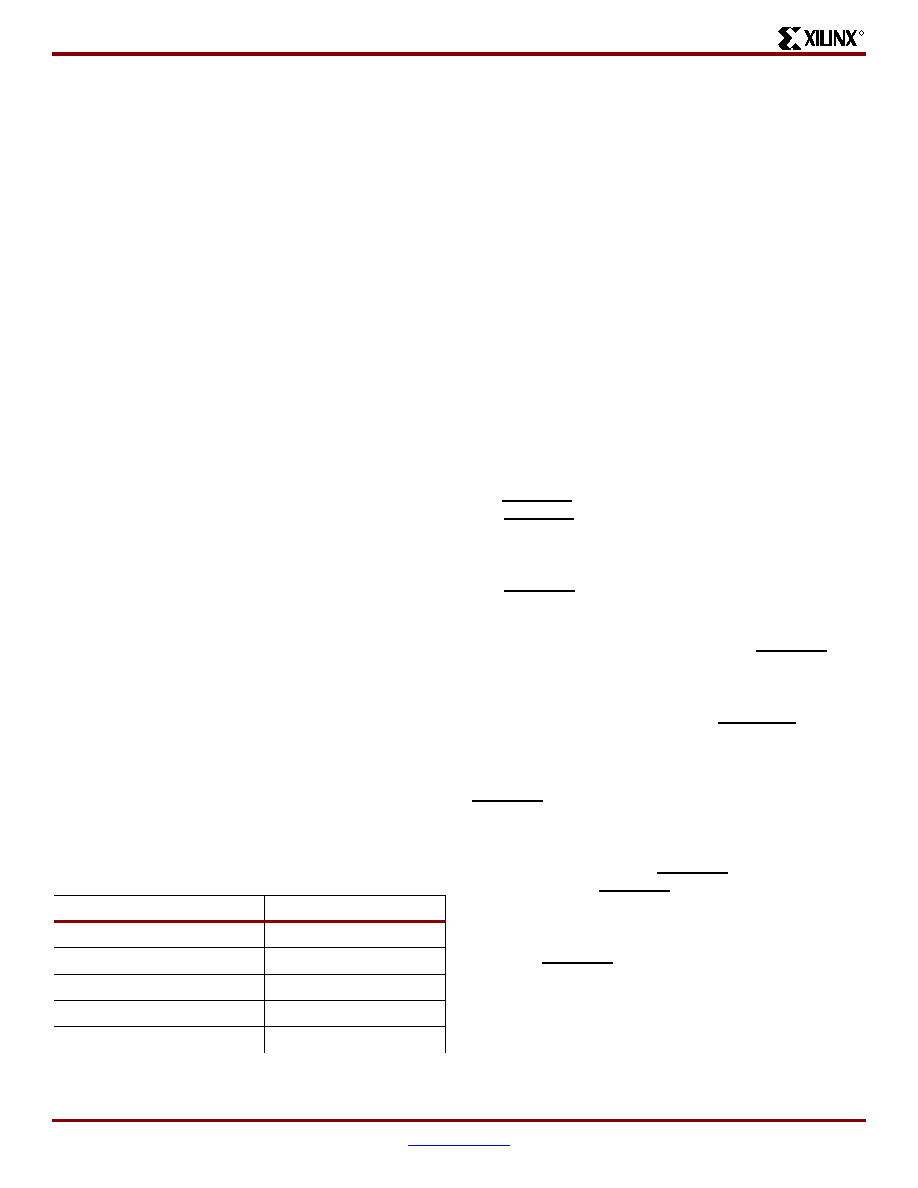

Table 13: IDCODEs Assigned to Spartan-XL FPGAs

FPGA

IDCODE

XCS05XL

0040A093h

XCS10XL

0040E093h

XCS20XL

00414093h

XCS30XL

00418093h

XCS40XL

0041C093h

相关PDF资料 |

PDF描述 |

|---|---|

| XCS40-3PQ208C | IC FPGA 5V C-TEMP 208-PQFP |

| XCS40-3BG256C | IC FPGA 5V C-TEMP 256-PBGA |

| ASM15DRES | CONN EDGECARD 30POS .156 EYELET |

| FMC25DRYI-S93 | CONN EDGECARD 50POS .100 DIP SLD |

| ASC65DRTS-S93 | CONN EDGECARD 130PS DIP .100 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XCS40-3PQ240C | 功能描述:IC FPGA 5V C-TEMP 240-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan® 标准包装:1 系列:Kintex-7 LAB/CLB数:25475 逻辑元件/单元数:326080 RAM 位总计:16404480 输入/输出数:350 门数:- 电源电压:0.97 V ~ 1.03 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:900-BBGA,FCBGA 供应商设备封装:900-FCBGA(31x31) 其它名称:122-1789 |

| XCS40-3PQ240I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS40-3PQ256C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS40-3PQ256I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS40-3PQ280C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

发布紧急采购,3分钟左右您将得到回复。