参数资料

| 型号: | XCS40-3PQ208I |

| 厂商: | Xilinx Inc |

| 文件页数: | 5/83页 |

| 文件大小: | 0K |

| 描述: | IC FPGA 5V I-TEMP 208-PQFP |

| 产品变化通告: | Spartan,Virtex FPGA/SCD Discontinuation 18/Oct/2010 |

| 标准包装: | 24 |

| 系列: | Spartan® |

| LAB/CLB数: | 784 |

| 逻辑元件/单元数: | 1862 |

| RAM 位总计: | 25088 |

| 输入/输出数: | 169 |

| 门数: | 40000 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 208-BFQFP |

| 供应商设备封装: | 208-PQFP(28x28) |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页

Spartan and Spartan-XL FPGA Families Data Sheet

DS060 (v2.0) March 1, 2013

13

Product Specification

R

Product Obsolete/Under Obsolescence

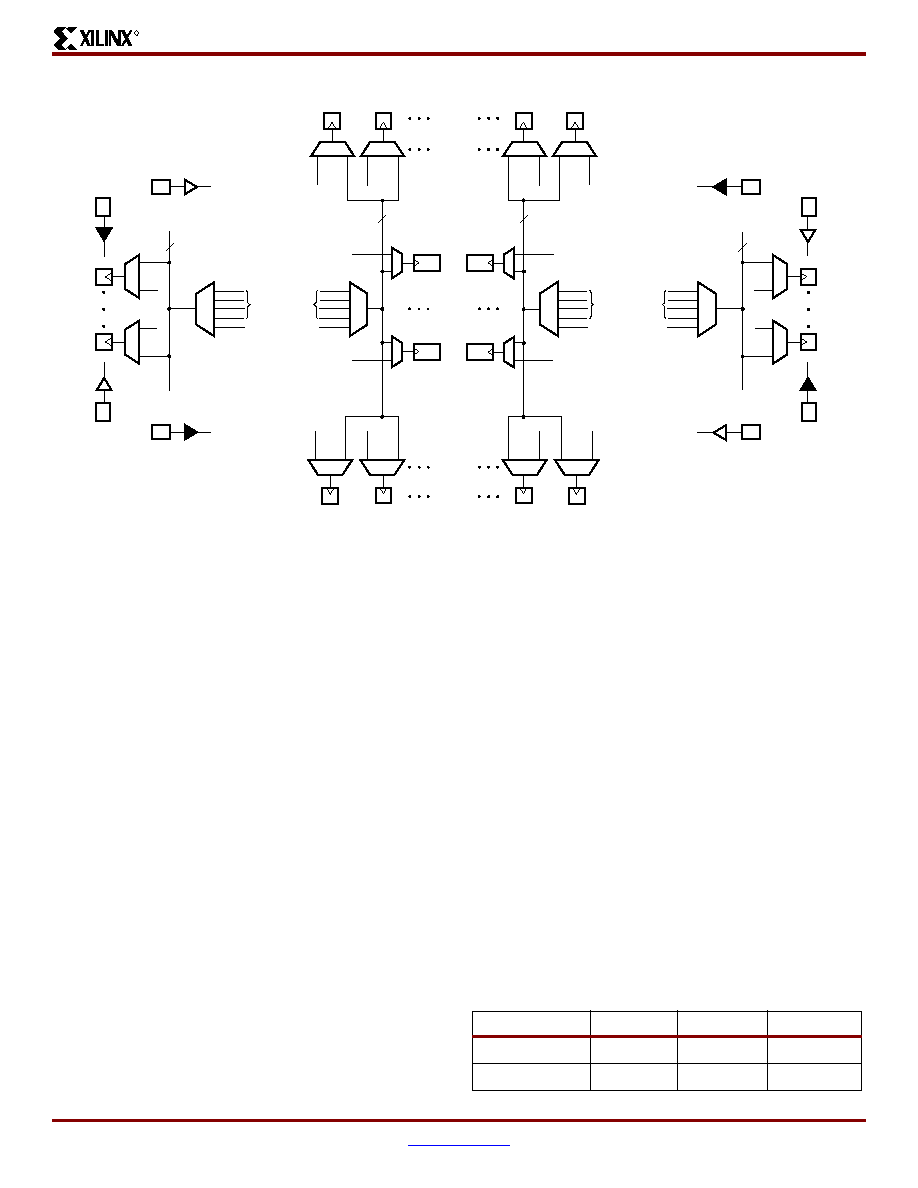

The four Primary Global buffers offer the shortest delay and

negligible skew. Four Secondary Global buffers have

slightly longer delay and slightly more skew due to poten-

tially heavier loading, but offer greater flexibility when used

to drive non-clock CLB inputs. The eight Global Low-Skew

buffers in the Spartan-XL devices combine short delay, neg-

ligible skew, and flexibility.

The Primary Global buffers must be driven by the semi-ded-

icated pads (PGCK1-4). The Secondary Global buffers can

be sourced by either semi-dedicated pads (SGCK1-4) or

internal nets. Each corner of the device has one Primary

buffer and one Secondary buffer. The Spartan-XL family

has eight global low-skew buffers, two in each corner. All

can be sourced by either semi-dedicated pads (GCK1-8) or

internal nets.

Using the library symbol called BUFG results in the software

choosing the appropriate clock buffer, based on the timing

requirements of the design. A global buffer should be spec-

ified for all timing-sensitive global signal distribution. To use

a global buffer, place a BUFGP (primary buffer), BUFGS

(secondary buffer), BUFGLS (Spartan-XL family global

low-skew buffer), or BUFG (any buffer type) element in a

schematic or in HDL code.

Advanced Features Description

Distributed RAM

Optional modes for each CLB allow the function generators

(F-LUT and G-LUT) to be used as Random Access Memory

(RAM).

Read and write operations are significantly faster for this

on-chip RAM than for off-chip implementations. This speed

advantage is due to the relatively short signal propagation

delays within the FPGA.

Memory Configuration Overview

There are two available memory configuration modes: sin-

gle-port RAM and dual-port RAM. For both these modes,

write operations are synchronous (edge-triggered), while

read operations are asynchronous. In the single-port mode,

a single CLB can be configured as either a 16 x 1, (16 x 1)

x 2, or 32 x 1 RAM array. In the dual-port mode, a single

CLB can be configured only as one 16 x 1 RAM array. The

different CLB memory configurations are summarized in

Table 8. Any of these possibilities can be individually pro-

grammed into a Spartan/XL FPGA CLB.

Figure 11: 5V Spartan Family Global Net Distribution

X4

ds060_11_080400

X4

4

One BUFGP

per Global Line

One BUFGP

per Global Line

Any BUFGS

BUFGP

PGCK4

SGCK4

PGCK3

SGCK3

BUFGS

BUFGP

BUFGS

IOB

BUFGS

BUFGP

SGCK1

PGCK1

SGCK2

PGCK2

IOB

X4

locals

4

CLB

locals

CLB

locals

Table 8: CLB Memory Configurations

Mode

16 x 1

(16 x 1) x 2

32 x 1

Single-Port

√√

√

Dual-Port

√

相关PDF资料 |

PDF描述 |

|---|---|

| XCS40-3PQ208C | IC FPGA 5V C-TEMP 208-PQFP |

| XCS40-3BG256C | IC FPGA 5V C-TEMP 256-PBGA |

| ASM15DRES | CONN EDGECARD 30POS .156 EYELET |

| FMC25DRYI-S93 | CONN EDGECARD 50POS .100 DIP SLD |

| ASC65DRTS-S93 | CONN EDGECARD 130PS DIP .100 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XCS40-3PQ240C | 功能描述:IC FPGA 5V C-TEMP 240-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan® 标准包装:1 系列:Kintex-7 LAB/CLB数:25475 逻辑元件/单元数:326080 RAM 位总计:16404480 输入/输出数:350 门数:- 电源电压:0.97 V ~ 1.03 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:900-BBGA,FCBGA 供应商设备封装:900-FCBGA(31x31) 其它名称:122-1789 |

| XCS40-3PQ240I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS40-3PQ256C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS40-3PQ256I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS40-3PQ280C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

发布紧急采购,3分钟左右您将得到回复。