参数资料

| 型号: | XCS40-3PQ208I |

| 厂商: | Xilinx Inc |

| 文件页数: | 56/83页 |

| 文件大小: | 0K |

| 描述: | IC FPGA 5V I-TEMP 208-PQFP |

| 产品变化通告: | Spartan,Virtex FPGA/SCD Discontinuation 18/Oct/2010 |

| 标准包装: | 24 |

| 系列: | Spartan® |

| LAB/CLB数: | 784 |

| 逻辑元件/单元数: | 1862 |

| RAM 位总计: | 25088 |

| 输入/输出数: | 169 |

| 门数: | 40000 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 208-BFQFP |

| 供应商设备封装: | 208-PQFP(28x28) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页当前第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页

Spartan and Spartan-XL FPGA Families Data Sheet

6

DS060 (v2.0) March 1, 2013

Product Specification

R

Product Obsolete/Under Obsolescence

The four internal control signals are:

EC: Enable Clock

SR: Asynchronous Set/Reset or H function generator

Input 0

DIN: Direct In or H function generator Input 2

H1: H function generator Input 1.

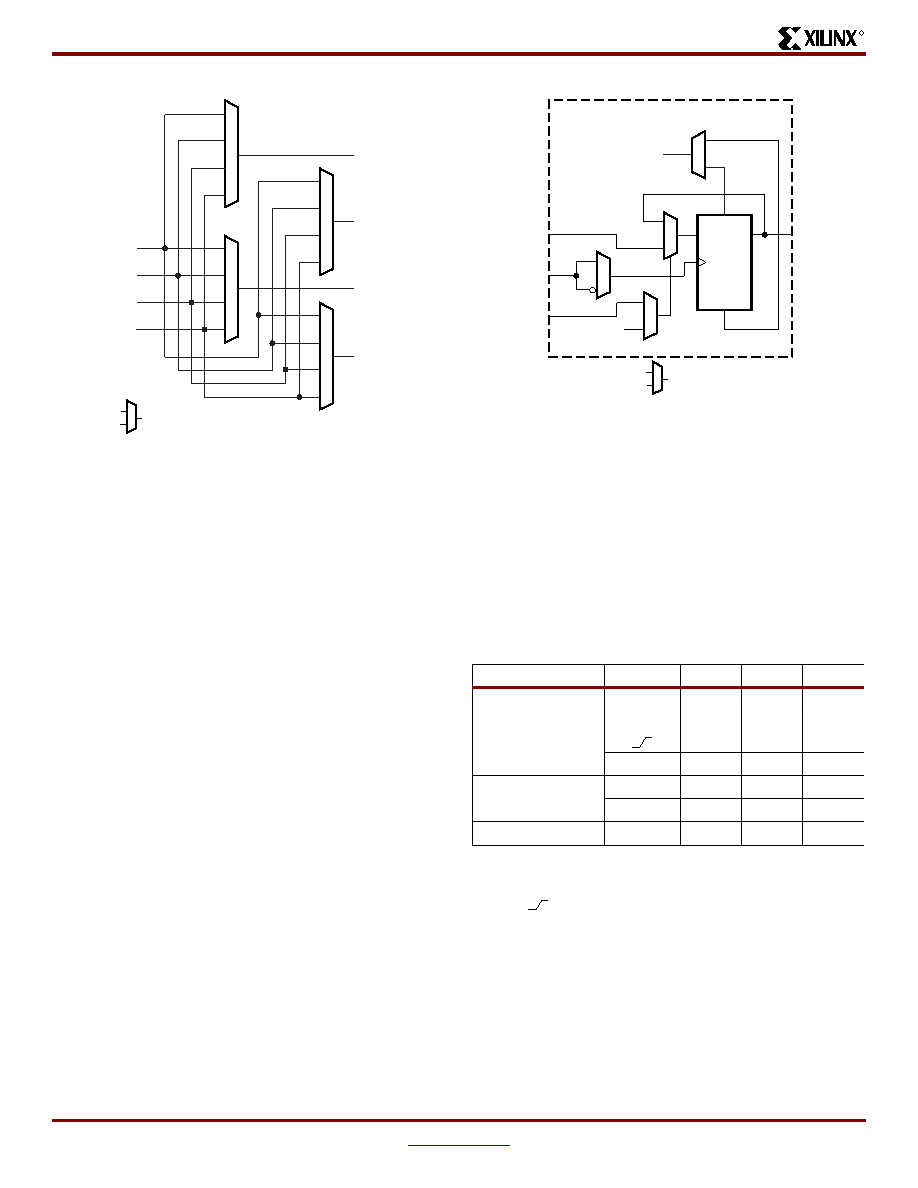

Input/Output Blocks (IOBs)

User-configurable input/output blocks (IOBs) provide the

interface between external package pins and the internal

logic. Each IOB controls one package pin and can be con-

figured for input, output, or bidirectional signals. Figure 6

shows a simplified functional block diagram of the Spar-

tan/XL FPGA IOB.

IOB Input Signal Path

The input signal to the IOB can be configured to either go

directly to the routing channels (via I1 and I2 in Figure 6) or

to the input register. The input register can be programmed

as either an edge-triggered flip-flop or a level-sensitive

latch. The functionality of this register is shown in Table 3,

and a simplified block diagram of the register can be seen in

Figure 4: CLB Control Signal Interface

Multiplexer Controlled

by Configuration Program

C1

DIN

H1

SR

EC

C2

C3

C4

DS060_04_081100

Figure 5: IOB Flip-Flop/Latch Functional Block

Diagram

Table 3: Input Register Functionality

Mode

CK

EC

D

Q

Power-Up or

GSR

XX

X

SR

Flip-Flop

1*

D

0X

X

Q

Latch

1

1*

X

Q

01*

D

Both

X

0

X

Q

Legend:

XDon’t care.

Rising edge (clock not inverted).

SR

Set or Reset value. Reset is default.

0*

Input is Low or unconnected (default

value)

1*

Input is High or unconnected (default

value)

Multiplexer Controlled

by Configuration Program

DQ

Q

D

GSR

Vcc

CK

EC

SD

RD

DS060_05_041901

相关PDF资料 |

PDF描述 |

|---|---|

| XCS40-3PQ208C | IC FPGA 5V C-TEMP 208-PQFP |

| XCS40-3BG256C | IC FPGA 5V C-TEMP 256-PBGA |

| ASM15DRES | CONN EDGECARD 30POS .156 EYELET |

| FMC25DRYI-S93 | CONN EDGECARD 50POS .100 DIP SLD |

| ASC65DRTS-S93 | CONN EDGECARD 130PS DIP .100 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XCS40-3PQ240C | 功能描述:IC FPGA 5V C-TEMP 240-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan® 标准包装:1 系列:Kintex-7 LAB/CLB数:25475 逻辑元件/单元数:326080 RAM 位总计:16404480 输入/输出数:350 门数:- 电源电压:0.97 V ~ 1.03 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:900-BBGA,FCBGA 供应商设备封装:900-FCBGA(31x31) 其它名称:122-1789 |

| XCS40-3PQ240I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS40-3PQ256C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS40-3PQ256I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS40-3PQ280C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

发布紧急采购,3分钟左右您将得到回复。