参数资料

| 型号: | XR16M698IQ100-F |

| 厂商: | Exar Corporation |

| 文件页数: | 30/58页 |

| 文件大小: | 0K |

| 描述: | IC UART FIFO 32B OCTAL 100QFP |

| 标准包装: | 66 |

| 特点: | * |

| 通道数: | 8 |

| FIFO's: | 32 字节 |

| 规程: | RS485 |

| 电源电压: | 1.62 V ~ 3.63 V |

| 带自动流量控制功能: | 是 |

| 带IrDA 编码器/解码器: | 是 |

| 带故障启动位检测功能: | 是 |

| 带调制解调器控制功能: | 是 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-BQFP |

| 供应商设备封装: | 100-QFP(14x20) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页

XR16M698

36

1.62V TO 3.63V HIGH PERFORMANCE OCTAL UART WITH 32-BYTE FIFO

REV. 1.0.0

]

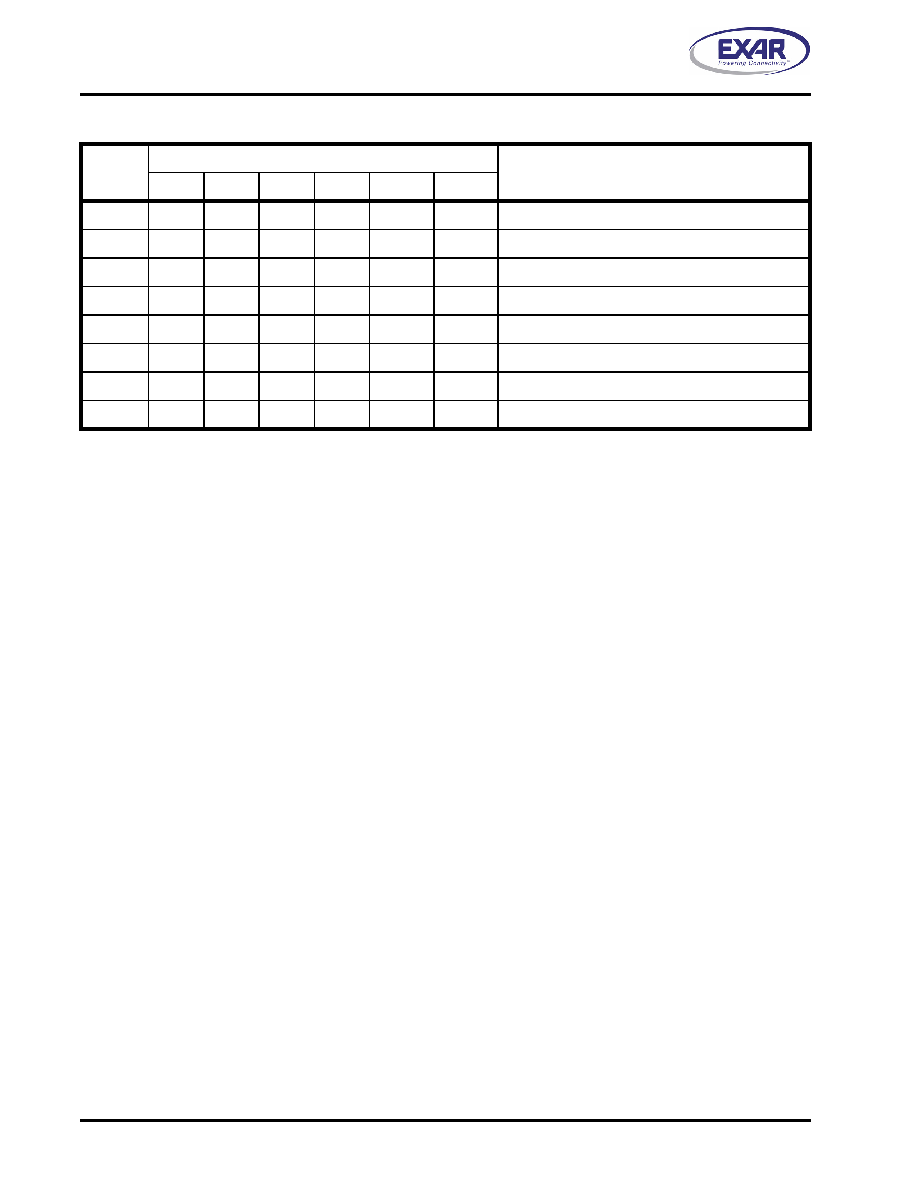

TABLE 14: INTERRUPT SOURCE AND PRIORITY LEVEL

PRIORITY

ISR REGISTER STATUS BITS

SOURCE OF THE INTERRUPT

LEVEL

BIT-5

BIT-4

BIT-3

BIT-2

BIT-1

BIT-0

1

0

1

0

LSR (Receiver Line Status Register)

2

0

1

0

RXRDY (Received Data Ready)

3

0

1

0

RXRDY (Receive Data Time-out)

4

0

1

0

TXRDY (Transmitter Holding Register Empty)

5

0

MSR (Modem Status Register)

6

0

1

0

RXRDY (Received Xon/Xoff or Special character)

7

1

0

CTS#/DSR#, RTS#/DTR# change of state

X

0

1

None (default) or wake-up indicator

ISR[7:6]: FIFO Enable Status

These bits are set to a logic 0 when the FIFOs are disabled. They are set to a logic 1 when the FIFOs are

enabled.

ISR[5]: RTS#/CTS# Interrupt Status

This bit is enabled when EFR bit-4 is set to a logic 1. ISR bit-5 indicates that the CTS# or RTS# has changed

state from LOW to HIGH.

ISR[4]: Xoff/Xon or Special Character Interrupt Status

This bit is enabled when EFR bit-4 is set to a logic 1. ISR bit-4 indicates that the receiver detected a data match

of the Xoff character(s). If this is an Xoff/Xon interrupt, it can be cleared by a read to the ISR. Reading the

XCHAR register will indicate which character (Xoff or Xon) was received last. If it is a special character

interrupt, it can be cleared by reading ISR or it will automatically clear after the next character is received.

ISR[5:1]: Interrupt Status

These bits indicate the source for a pending interrupt at interrupt priority levels (See Table 14). See “Section

and “Section 4.4.2, Interrupt Clearing:” on page 35 for details.

ISR[0]: Interrupt Status

Logic 0 = An interrupt is pending and the ISR contents may be used as a pointer to the appropriate interrupt

service routine.

Logic 1 = No interrupt pending. (default condition)

4.5

FIFO Control Register (FCR) - Write Only

This register is used to enable the FIFOs, clear the FIFOs, set the transmit/receive FIFO trigger levels, and

select the DMA mode. The DMA, and FIFO modes are defined as follows:

FCR[7:6]: Receive FIFO Trigger Select

(logic 0 = default, RX trigger level =1)

These 2 bits are used to set the trigger level for the receive FIFO. The UART will issue a receive interrupt when

the number of the characters in the FIFO crosses the trigger level. Table 15 shows the complete selections.

Note that the receiver and the transmitter cannot use different trigger tables. Whichever selection is made last

applies to both the RX and TX side.

相关PDF资料 |

PDF描述 |

|---|---|

| XR16M770IL32-F | IC UART FIFO 64B 32QFN |

| XR16M780IM48-F | IC UART FIFO 64B 48TQFP |

| XR16M781IL32-F | IC UART FIFO 64B 32QFN |

| XR16M890IM48TR-F | IC UART TXRX 128 BYTE 48TQFP |

| XR16V2550IL-F | IC UART FIFO 16B DUAL 32QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XR16M698IQ100TR-F | 制造商:Exar Corporation 功能描述:UART 8-CH 32Byte FIFO 1.8V/2.5V/3.3V 100-Pin PQFP T/R 制造商:Exar Corporation 功能描述:XR16M698IQ100TR-F |

| XR16M752 | 制造商:EXAR 制造商全称:EXAR 功能描述:HIGH PERFORMANCE DUART WITH 64-BYTE FIFO |

| XR16M752_09 | 制造商:EXAR 制造商全称:EXAR 功能描述:HIGH PERFORMANCE DUART WITH 64-BYTE FIFO |

| XR16M752IL-0B-EB | 功能描述:UART 接口集成电路 Supports 16M752 32L QFN, PCI Interface RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| XR16M752IL32 | 制造商:EXAR 制造商全称:EXAR 功能描述:HIGH PERFORMANCE DUART WITH 64-BYTE FIFO |

发布紧急采购,3分钟左右您将得到回复。