参数资料

| 型号: | XR16M698IQ100-F |

| 厂商: | Exar Corporation |

| 文件页数: | 32/58页 |

| 文件大小: | 0K |

| 描述: | IC UART FIFO 32B OCTAL 100QFP |

| 标准包装: | 66 |

| 特点: | * |

| 通道数: | 8 |

| FIFO's: | 32 字节 |

| 规程: | RS485 |

| 电源电压: | 1.62 V ~ 3.63 V |

| 带自动流量控制功能: | 是 |

| 带IrDA 编码器/解码器: | 是 |

| 带故障启动位检测功能: | 是 |

| 带调制解调器控制功能: | 是 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-BQFP |

| 供应商设备封装: | 100-QFP(14x20) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页

XR16M698

38

1.62V TO 3.63V HIGH PERFORMANCE OCTAL UART WITH 32-BYTE FIFO

REV. 1.0.0

LCR[7]: Baud Rate Divisors Enable

Baud rate generator divisor (DLL, DLM, DLD) enable.

Logic 0 = Data registers are selected (default).

Logic 1 = Divisor latch registers (DLL, DLM and DLD) are selected.

LCR[6]: Transmit Break Enable

When enabled the Break control bit causes a break condition to be transmitted (the TX output is forced to a

“space’, logic 0, state). This condition remains until disabled by setting LCR bit-6 to a logic 0.

Logic 0 = No TX break condition. (default)

Logic 1 = Forces the transmitter output (TX) to a “space”, logic 0, for alerting the remote receiver of a line

break condition.

LCR[5]: TX and RX Parity Select

If the parity bit is enabled, LCR BIT-5 selects the forced parity format.

LCR BIT-5 = logic 0, parity is not forced (default).

LCR BIT-5 = logic 1 and LCR BIT-4 = logic 0, parity bit is forced to a logical 1 for the transmit and receive

data.

LCR BIT-5 = logic 1 and LCR BIT-4 = logic 1, parity bit is forced to a logical 0 for the transmit and receive

data.

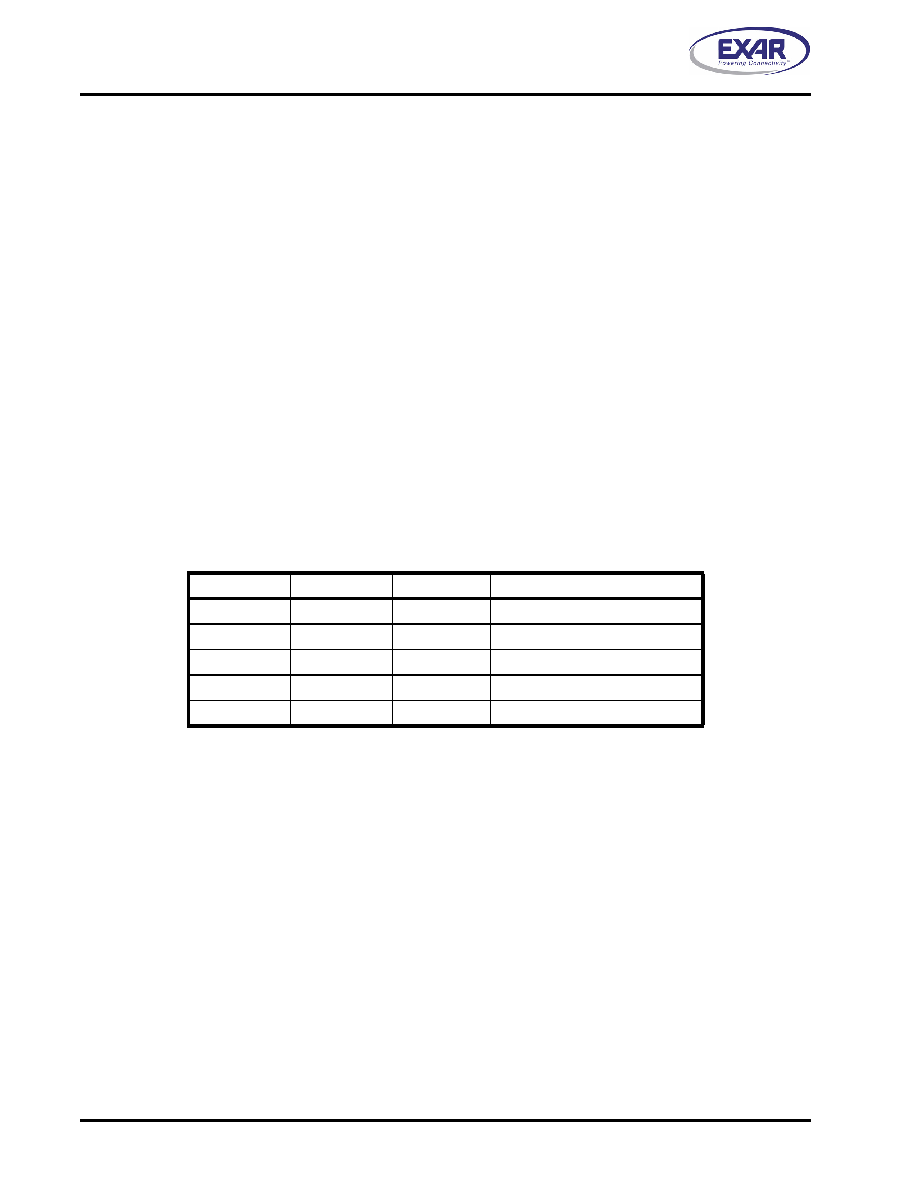

TABLE 16: PARITY PROGRAMMING

LCR BIT-5

LCR BIT-4

LCR BIT-3

PARITY SELECTION

X

0

No parity

0

1

Odd parity

0

1

Even parity

1

0

1

Force parity to mark, “1”

1

Force parity to space, “0”

LCR[4]: TX and RX Parity Select

If the parity bit is enabled with LCR bit-3 set to a logic 1, LCR BIT-4 selects the even or odd parity format.

Logic 0 = ODD Parity is generated by forcing an odd number of logic 1’s in the transmitted character. The

receiver must be programmed to check the same format (default).

Logic 1 = EVEN Parity is generated by forcing an even the number of logic 1’s in the transmitted character.

The receiver must be programmed to check the same format.

LCR[3]: TX and RX Parity Select

Parity or no parity can be selected via this bit. The parity bit is a simple way used in communications for data

integrity check. See Table 16 above for parity selection summary.

Logic 0 = No parity.

Logic 1 = A parity bit is generated during the transmission while the receiver checks for parity error of the

data character received.

相关PDF资料 |

PDF描述 |

|---|---|

| XR16M770IL32-F | IC UART FIFO 64B 32QFN |

| XR16M780IM48-F | IC UART FIFO 64B 48TQFP |

| XR16M781IL32-F | IC UART FIFO 64B 32QFN |

| XR16M890IM48TR-F | IC UART TXRX 128 BYTE 48TQFP |

| XR16V2550IL-F | IC UART FIFO 16B DUAL 32QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XR16M698IQ100TR-F | 制造商:Exar Corporation 功能描述:UART 8-CH 32Byte FIFO 1.8V/2.5V/3.3V 100-Pin PQFP T/R 制造商:Exar Corporation 功能描述:XR16M698IQ100TR-F |

| XR16M752 | 制造商:EXAR 制造商全称:EXAR 功能描述:HIGH PERFORMANCE DUART WITH 64-BYTE FIFO |

| XR16M752_09 | 制造商:EXAR 制造商全称:EXAR 功能描述:HIGH PERFORMANCE DUART WITH 64-BYTE FIFO |

| XR16M752IL-0B-EB | 功能描述:UART 接口集成电路 Supports 16M752 32L QFN, PCI Interface RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| XR16M752IL32 | 制造商:EXAR 制造商全称:EXAR 功能描述:HIGH PERFORMANCE DUART WITH 64-BYTE FIFO |

发布紧急采购,3分钟左右您将得到回复。