- 您现在的位置:买卖IC网 > PDF目录300164 > ZL50112GAG2 (ZARLINK SEMICONDUCTOR INC) SPECIALTY TELECOM CIRCUIT, PBGA552 PDF资料下载

参数资料

| 型号: | ZL50112GAG2 |

| 厂商: | ZARLINK SEMICONDUCTOR INC |

| 元件分类: | 通信及网络 |

| 英文描述: | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| 封装: | 35 X 35 MM, 1.27 MM, LEAD FREE, PLASTIC, BGA-552 |

| 文件页数: | 41/113页 |

| 文件大小: | 1923K |

| 代理商: | ZL50112GAG2 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页当前第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页

ZL50110/11/12/14

Data Sheet

33

Zarlink Semiconductor Inc.

3.3

Packet Interfaces

For the ZL50111 and ZL50112 variants the packet interface is capable of either 3 MII interfaces, 2 redundant GMII

interfaces or 2 redundant TBI (1000 Mbps) interfaces. The TBI interface is a PCS interface supported by an

integrated 1000BASE-X PCS module. The ZL50110 and ZL50114 variants have either 2 MII interfaces, 2 redundant

GMII interfaces or 2 redundant TBI (1000 Mbps) interfaces. When the packet interface is programmed for PCS/TBI

mode, by default the hardware will not enable auto-negotiation. The TBI auto-negotiation must be done by

application software. Ports 2 and 3 are not available on the ZL50110 and ZL50114 devices.

NOTE: In GMII/TBI mode only 1 GMAC port may be used to receive data. The second GMAC port is for

redundancy purposes only.

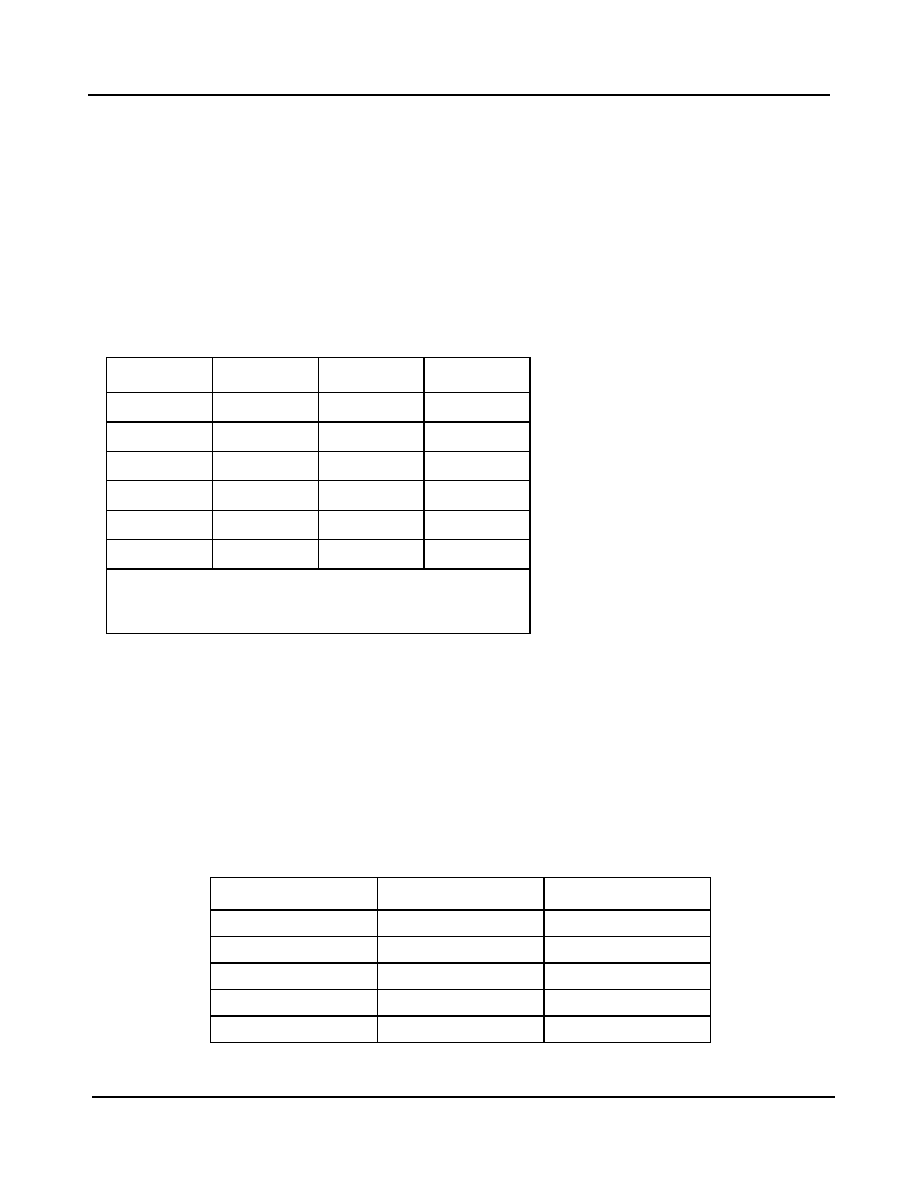

Data for all three types of packet switching is based on Specification IEEE Std. 802.3 - 2000. The table below

highlights the valid Ethernet interface combinations:

Note: Port 2 and Port 3 can not be used to receive data simultaneously, they are mutually exclusive for packet

reception. They may both be used for packet transmission if required.

The ZL50110/11/12/14 will not take action when receiving a PAUSE frame. It will not pause the transmission of

traffic. It is normally not required to stop CESoP traffic because it is generally constant bit rate and time sensitive. If

necessary, the limiting of egress non-CESoP traffic may be done external to the ZL50110/11/12/14 (e.g. in an

Ethernet switch).

Table 8 maps the signal pins used in the MII interface to those used in the GMII and TBI interface. Table 9 shows

MII Management Interface Package Ball Definition. Table 10, Table 11, Table 12, and Table 13 show respectively

the MII Port 0, Port 1, Port 2 and Port 3 Interface Package Ball Definition.

All Packet Interface signals are 5 V tolerant, and all outputs are high impedance while System Reset is LOW.

MII Port 0

MII Port 1

MII Port 2*

MII Port 3**

GE

GE***

--

GE

--

FE

--

GE

--

FE

--

FE

--

FE

--

FE

Note 1:

*ZL50111/112 only

Note 2:

**ZL50111 only

Note 3:

***Standby only

MII

GMII

TBI (PCS)

Mn_LINKUP_LED

Mn_ACTIVE_LED

-Mn_GIGABIT_LED

Mn_GIGABIT_LED

-Mn_REFCLK

Mn_REFCLK

Mn_RXCLK

Mn_RBC0

Table 8 - Packet Interface Signal Mapping - MII to GMII/TBI

相关PDF资料 |

PDF描述 |

|---|---|

| ZL50112GAG | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50114GAG2 | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50114GAG | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50232GD | DATACOM, ISDN ECHO CANCELLER, PBGA208 |

| ZL50233/GDG | DATACOM, ISDN ECHO CANCELLER, PBGA208 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ZL50114 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:128, 256, 512 and 1024 Channel CESoP Processors |

| ZL50114GAG | 制造商:Microsemi Corporation 功能描述:CESOP PROCESSOR 552BGA - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC CESOP PROCESSOR 128CH 552PBGA 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 128CH 552PBGA |

| ZL50114GAG2 | 制造商:Microsemi Corporation 功能描述:CESOP PROCESSOR 552BGA - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC CESOP PROCESSOR 128CH 552PBGA 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 128CH 552PBGA |

| ZL50115 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:32, 64 and 128 Channel CESoP Processors |

| ZL50115GAG | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 1K X 1K 1.8V/3.3V 324BGA - Trays 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 32CH 324PBGA |

发布紧急采购,3分钟左右您将得到回复。