- 您现在的位置:买卖IC网 > PDF目录300164 > ZL50112GAG2 (ZARLINK SEMICONDUCTOR INC) SPECIALTY TELECOM CIRCUIT, PBGA552 PDF资料下载

参数资料

| 型号: | ZL50112GAG2 |

| 厂商: | ZARLINK SEMICONDUCTOR INC |

| 元件分类: | 通信及网络 |

| 英文描述: | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| 封装: | 35 X 35 MM, 1.27 MM, LEAD FREE, PLASTIC, BGA-552 |

| 文件页数: | 74/113页 |

| 文件大小: | 1923K |

| 代理商: | ZL50112GAG2 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页当前第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页

ZL50110/11/12/14

Data Sheet

63

Zarlink Semiconductor Inc.

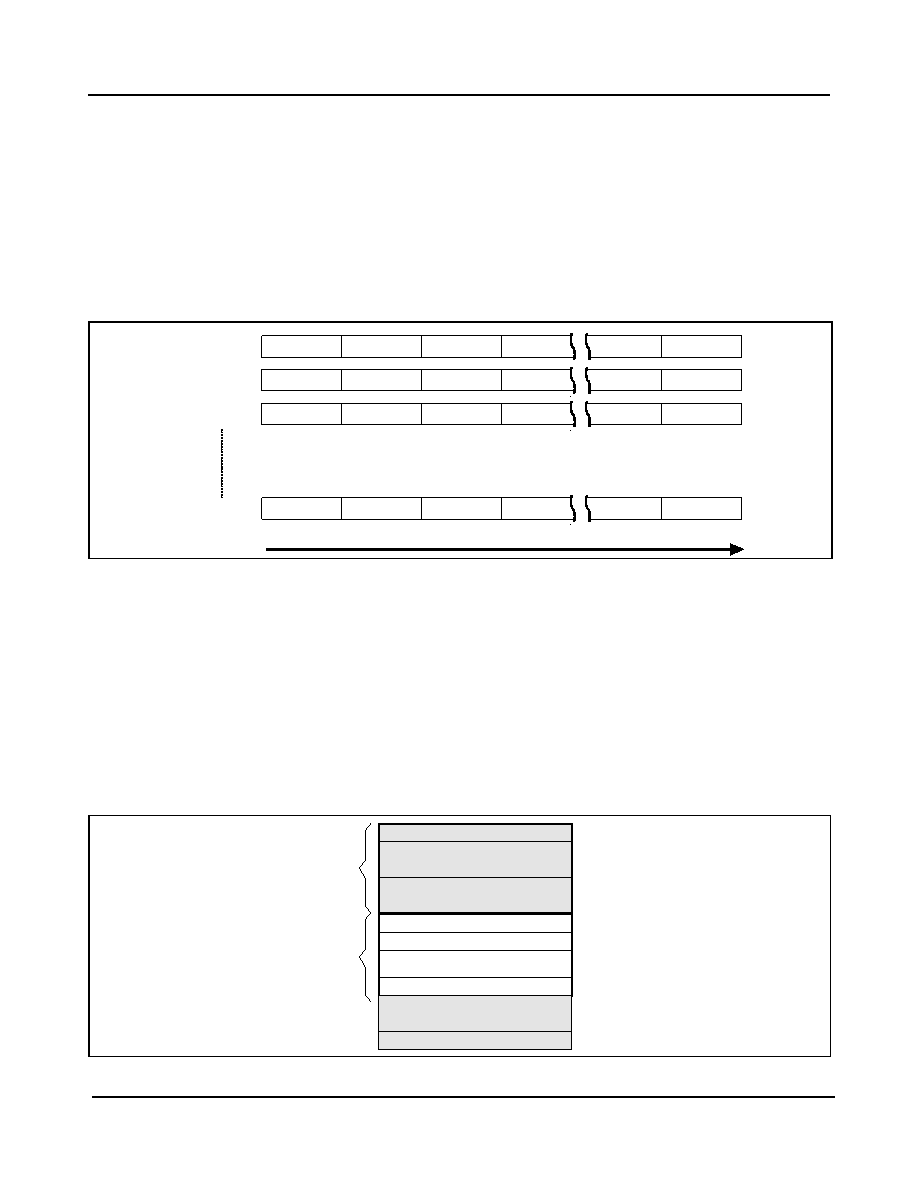

shows the packet format for structured TDM data, where the payload is split into frames, and each frame

concatenated to form the packet.

5.4.1.1

Structured Payload Order

Packets are assembled sequentially, with each channel placed into the packet as it arrives at the TDM Access

Interface. A fixed order of channels is maintained (see Figure 16), with channel 0 placed before channel 1,

which is placed before channel 2. It is this order that allows the packet to be correctly disassembled at the far

end. A context must contain only unique channel numbers. As such a context that contains the same channel

from different streams, for example channel 1 from stream 2 and channel 1 from stream 5, would not be

permitted.

Figure 16 - Channel Order for Packet Formation

Each packet contains one or more frames of TDM data, in sequential order. This groups the selected channels

for the first frame, followed by the same set of channels for the subsequent frame, and so on.

5.4.2

Unstructured Payload Operation

In unstructured mode, the payload is not split by defined frames or timeslots, so the packet consists of a continuous

stream of data. Each packet contains a programmable number of octets, as shown in Figure 17. The number of

octets in a packet need not be an integer number of frames. A typical value for N may be 192, as defined in the

IETF PWE3 RFC. For example, consider mapping the unstructured data of a 25 timeslot DS0 stream. The data for

each T1 frame would normally consist of 193 bits, 192 data bits and 1 framing bit. If the payload consists of 24

octets it will be 1 bit short of a complete frames worth of data, if the payload consists of 25 octets it will be 7 bits over

a complete frames worth of data. NOTE: No alignment of the octets with the T1 framing structure can be assumed.

Figure 17 - ZL50110/11/12/14 Packet Format - Unstructured Mode

C h an nel 0

C h an nel 1

C han ne l 2

C h a n nel 31

Stre a m 0

C h an nel 0

C h an nel 1

C han ne l 2

C h a n nel 31

Stre am 3 1

C h an nel 0

C h an nel 1

C han ne l 2

C h a n nel 31

Stre a m 1

C h an nel 0

C h an nel 1

C han ne l 2

C h a n nel 31

Stre a m 2

C han ne l A s s e m b ly O rder

Header

N octets of data from unstructured stream

NOTE: No frame or channel alignment

may include VLAN tagging

e.g. IPv4, IPv6, MPLS

e.g. UDP, L2TP, RTP,

CESoPSN, SAToP

TDM Payload

(constructed by Payload Assembler)

46 to 1500 bytes

may also be placed in the

packet header

Octet 1

Octet 2

Octet N

Ethernet Header

Network Layers

(added by Packet Transmit)

Upper layers

(added by Protocol Engine)

Ethernet FCS

Static Padding

(if required to meet minimum payload size)

相关PDF资料 |

PDF描述 |

|---|---|

| ZL50112GAG | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50114GAG2 | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50114GAG | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50232GD | DATACOM, ISDN ECHO CANCELLER, PBGA208 |

| ZL50233/GDG | DATACOM, ISDN ECHO CANCELLER, PBGA208 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ZL50114 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:128, 256, 512 and 1024 Channel CESoP Processors |

| ZL50114GAG | 制造商:Microsemi Corporation 功能描述:CESOP PROCESSOR 552BGA - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC CESOP PROCESSOR 128CH 552PBGA 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 128CH 552PBGA |

| ZL50114GAG2 | 制造商:Microsemi Corporation 功能描述:CESOP PROCESSOR 552BGA - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC CESOP PROCESSOR 128CH 552PBGA 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 128CH 552PBGA |

| ZL50115 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:32, 64 and 128 Channel CESoP Processors |

| ZL50115GAG | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 1K X 1K 1.8V/3.3V 324BGA - Trays 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 32CH 324PBGA |

发布紧急采购,3分钟左右您将得到回复。