- 您现在的位置:买卖IC网 > PDF目录33761 > 42S16400A (Integrated Silicon Solution, Inc.) 1 Meg Bits x 16 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM PDF资料下载

参数资料

| 型号: | 42S16400A |

| 厂商: | Integrated Silicon Solution, Inc. |

| 英文描述: | 1 Meg Bits x 16 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

| 中文描述: | 1梅格位× 16位× 4银行(64兆位)同步动态RAM |

| 文件页数: | 11/55页 |

| 文件大小: | 472K |

| 代理商: | 42S16400A |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页

IS42S16400A

ISSI

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

19

Rev.C

04/16/03

CLK

CKE

HIGH - Z

ROW ADDRESS

BANK ADDRESS

CS

RAS

CAS

WE

A0-A11

BA0,BA1

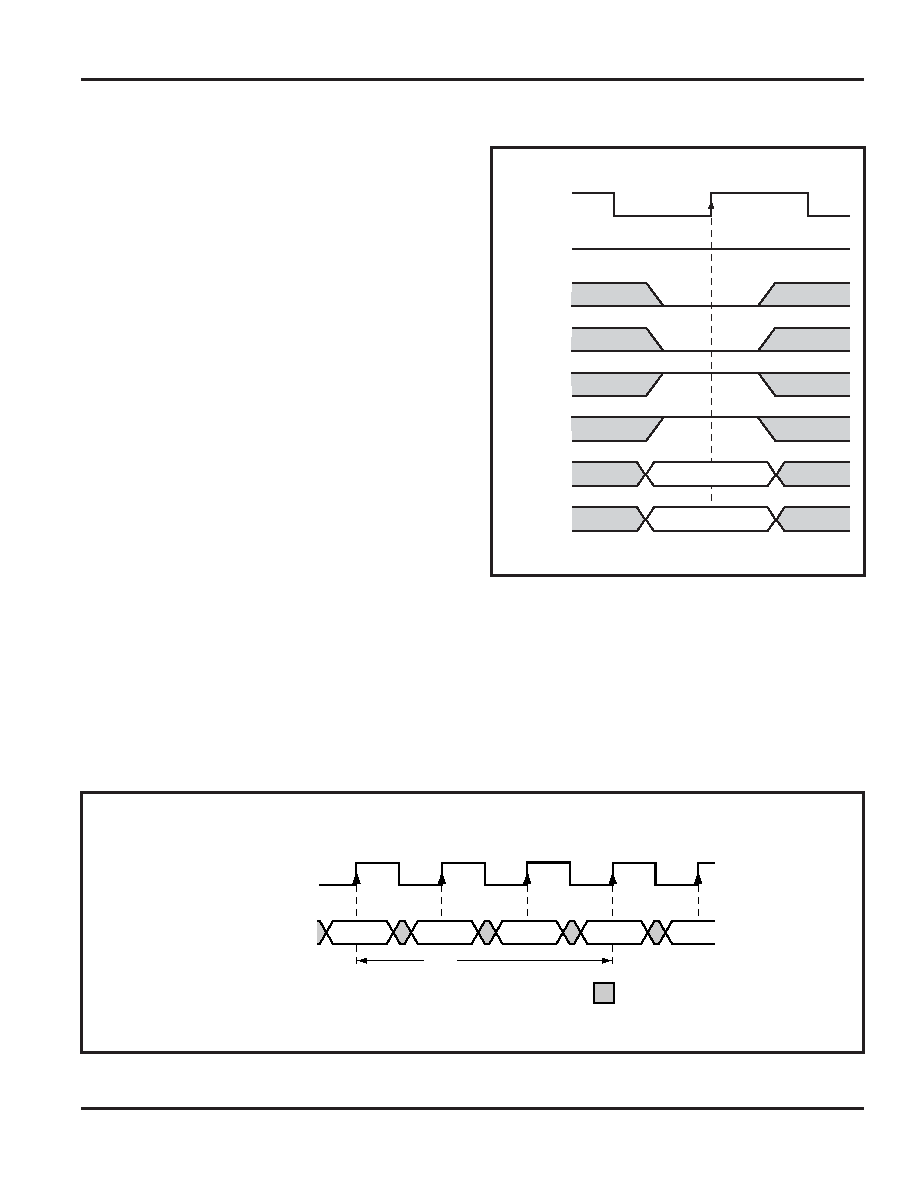

Activating Specific Row Within Specific Bank

DON'T CARE

CLK

COMMAND

ACTIVE

NOP

tRCD

T0

T1

T2

T3

T4

READ or

WRITE

OPERATION

BANK/ROW ACTIVATION

Before any READ or WRITE commands can be issued to

a bank within the SDRAM, a row in that bank must be

“opened.” This is accomplished via the ACTIVE command,

which selects both the bank and the row to be activated

(see Activating Specific Row Within Specific Bank).

After opening a row (issuing an ACTIVE command), a READ

or WRITE command may be issued to that row, subject to

the tRCD specification. Minimum tRCD should be divided by

the clock period and rounded up to the next whole number

to determine the earliest clock edge after the ACTIVE

command on which a READ or WRITE command can be

entered. For example, a tRCD specification of 20ns with a

125 MHz clock (8ns period) results in 2.5 clocks, rounded

to 3. This is reflected in the following example, which

covers any case where 2 < [tRCD (MIN)/tCK]

≤ 3. (The

same procedure is used to convert other specification

limits from time units to clock cycles).

A subsequent ACTIVE command to a different row in the

same bank can only be issued after the previous active

row has been “closed” (precharged). The minimum time

interval between successive ACTIVE commands to the

same bank is defined by tRC.

A subsequent ACTIVE command to another bank can be

issued while the first bank is being accessed, which

results in a reduction of total row-access overhead. The

minimum time interval between successive ACTIVE com-

mands to different banks is defined by tRRD.

Example: Meeting tRCD (MIN) when 2

<<<<< [tRCD (min)/tCK] ≤≤≤≤≤ 3

相关PDF资料 |

PDF描述 |

|---|---|

| 42S16800A | 16Meg x 8, 8Meg x16 & 4Meg x 32 128-MBIT SYNCHRONOUS DRAM |

| 42S32200 | 512K Bits x 32 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

| 4300-000 | EMI/RFI FILTER Hermetically Sealed |

| 4300-000LF | |

| 4300-001 | EMI/RFI FILTER Hermetically Sealed |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 42S16400B-6TLTR | 制造商:Integrated Silicon Solution Inc 功能描述: |

| 42S16800A | 制造商:ISSI 制造商全称:Integrated Silicon Solution, Inc 功能描述:16Meg x 8, 8Meg x16 & 4Meg x 32 128-MBIT SYNCHRONOUS DRAM |

| 42S16800L | 制造商:NEC 制造商全称:NEC 功能描述:3.3 V OPERATION 16 M-BIT DYNAMIC RAM 2 M-WORD BY 8-BIT, FAST PAGE MODE |

| 42S16800L-A60 | 制造商:NEC 制造商全称:NEC 功能描述:3.3 V OPERATION 16 M-BIT DYNAMIC RAM 2 M-WORD BY 8-BIT, FAST PAGE MODE |

| 42S16800L-A70 | 制造商:NEC 制造商全称:NEC 功能描述:3.3 V OPERATION 16 M-BIT DYNAMIC RAM 2 M-WORD BY 8-BIT, FAST PAGE MODE |

发布紧急采购,3分钟左右您将得到回复。