- 您现在的位置:买卖IC网 > PDF目录68811 > 71M6542G-IGT/F (MAXIM INTEGRATED PRODUCTS INC) SPECIALTY ANALOG CIRCUIT, PQFP100 PDF资料下载

参数资料

| 型号: | 71M6542G-IGT/F |

| 厂商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分类: | 模拟信号调理 |

| 英文描述: | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 封装: | LEAD FREE, LQFP-100 |

| 文件页数: | 15/165页 |

| 文件大小: | 2208K |

| 代理商: | 71M6542G-IGT/F |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页

v1.1

2008–2011 Teridian Semiconductor Corporation

111

5.2

I/O RAM Map – Alphabetical Order

Table 76 lists I/O RAM bits and registers in alphabetical order.

Bits with a write direction (W in column Dir) are written by the MPU into configuration RAM. Typically, they are initially stored in flash memory and

copied to the configuration RAM by the MPU. Some of the more frequently programmed bits are mapped to the MPU SFR memory space. The

remaining bits are mapped to the address space 0x2XXX. Bits with R (read) direction can be read by the MPU. Columns labeled Rst and Wk

describe the bit values upon reset and wake, respectively. No entry in one of these columns means the bit is either read-only or is powered by the

NV supply and is not initialized. Write-only bits return zero when they are read.

Locations that are shaded in grey are non-volatile (i.e., battery-backed).

Table 76: I/O RAM Map – Functional Order

Name

Location

Rst Wk

Dir

Description

ADC_E

2704[4]

0

R/W Enables ADC and VREF. When disabled, reduces bias current.

ADC_DIV

2200[5]

0

R/W

ADC_DIV controls the rate of the ADC and FIR clocks.

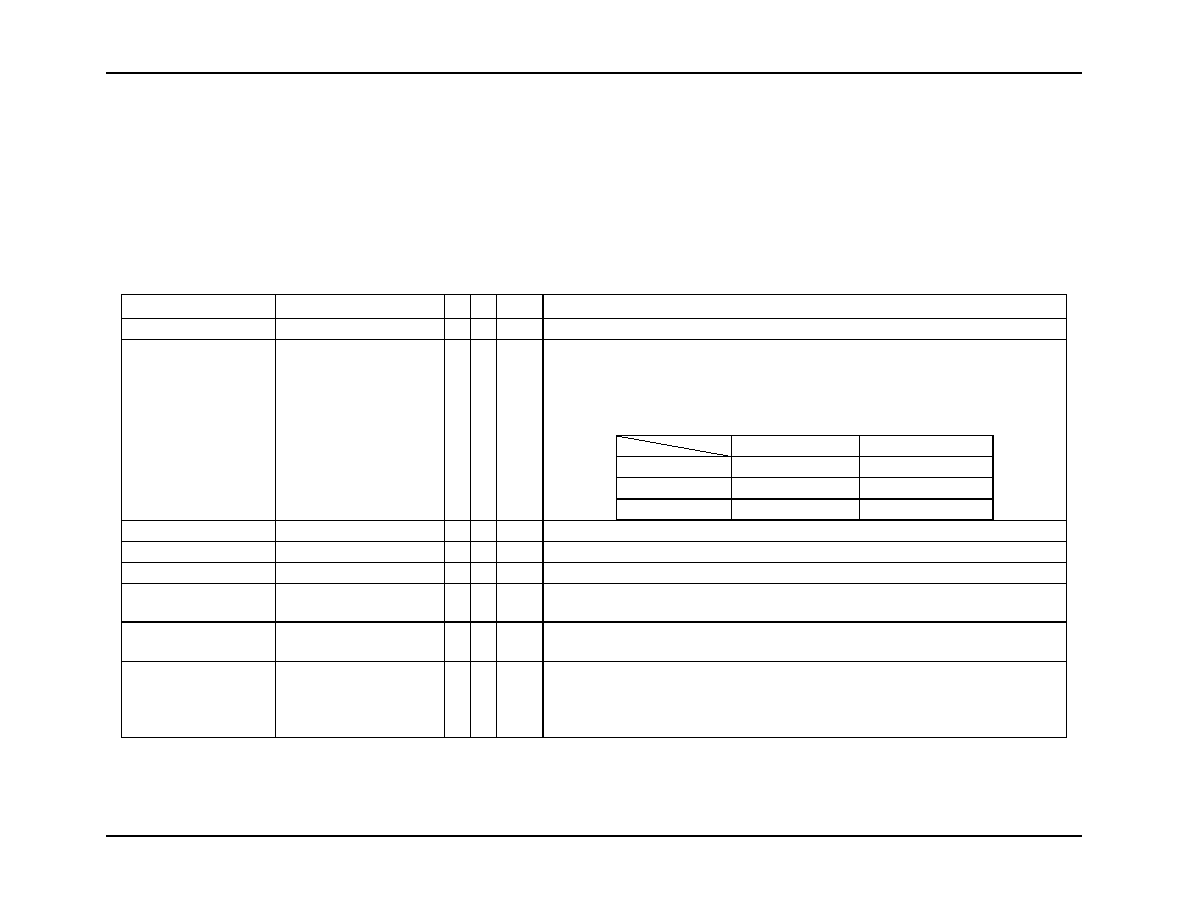

The ADC_DIV setting determines whether MCK is divided by 4 or 8:

0 = MCK/4

1 = MCK/8

The resulting ADC and FIR clock is as shown below.

PLL_FAST = 0

PLL_FAST = 1

MCK

6.291456 MHz

19.660800 MHz

ADC_DIV = 0

1.572864 MHz

4.9152 MHz

ADC_DIV = 1

0.786432 MHz

2.4576 MHz

BCURR

2704[3]

0

R/W Connects a 100 A load to the battery selected by TEMP_BSEL.

BSENSE[7:0]

2885[7:0]

–

R

The result of the battery measurement. See 2.5.6 71M654x Battery Monitor.

CE_E

2106[0]

0

R/W CE enable.

CE_LCTN[5:0]

2109[5:0]

31 31 R/W

CE program location. The starting address for the CE program is

1024*CE_LCTN.

CHIP_ID[15:8]

CHIP_ID[7:0]

2300[7:0]

2301[7:0]

0

R

These bytes contain the chip identification.

CHOP_E[1:0]

2106[3:2]

0

R/W

Chop enable for the reference bandgap circuit. The value of CHOP changes

on the rising edge of MUXSYNC according to the value in CHOP_E:

00 = toggle

1

01 = positive

10 = reversed

11 = toggle

1except at the mux sync edge at the end of an accumulation interval.

相关PDF资料 |

PDF描述 |

|---|---|

| 71M6541G-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP64 |

| 71M6541F-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP64 |

| 71M6543F-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 71M6543H-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 71M6543F-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 71M6542G-IGTR/F | 制造商:Maxim Integrated Products 功能描述:- Tape and Reel |

| 71M6542GT-IGT/F | 制造商:Maxim Integrated Products 功能描述:1-PHASE, 128KB, PRES TEMP SENSOR - Bulk |

| 71M6542GT-IGTR/F | 制造商:Maxim Integrated Products 功能描述:1-PHASE, 128KB, PRES TEMP SENSOR - Tape and Reel |

| 71M6543F | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Selectable Gain of 1 or 8 for One Current Energy Meter ICs Metrology Compensation |

| 71M6543F-DB | 功能描述:开发板和工具包 - 8051 71M6543 Eval Kit RoHS:否 制造商:Silicon Labs 产品:Development Kits 工具用于评估:C8051F960, Si7005 核心: 接口类型:USB 工作电源电压: |

发布紧急采购,3分钟左右您将得到回复。