- 您现在的位置:买卖IC网 > PDF目录10031 > AD6654CBCZ (Analog Devices Inc)IC ADC 14BIT W/4CH RSP 256CSPBGA PDF资料下载

参数资料

| 型号: | AD6654CBCZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 68/88页 |

| 文件大小: | 0K |

| 描述: | IC ADC 14BIT W/4CH RSP 256CSPBGA |

| 标准包装: | 1 |

| 位数: | 14 |

| 采样率(每秒): | 92.16M |

| 数据接口: | 串行,并联 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 2.5W |

| 电压电源: | 模拟和数字 |

| 工作温度: | -25°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 256-BGA,CSPBGA |

| 供应商设备封装: | 256-CSPBGA(17x17) |

| 包装: | 托盘 |

| 输入数目和类型: | 1 个差分,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页当前第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页

AD6654

Rev. 0 | Page 70 of 88

MICROPORT

The microport on the AD6654 can be used for programming

the part, reading register values, and reading output data (I, Q,

and RSSI words).

Note that, at any given point in time, either the microport or the

serial port can be active, but not both. Some of the balls on the

package are shared between the microport and the serial port

and have dual functionality based on the SMODE pin. The

microport is selected by pulling the SMODE pin low (ground).

Both read and write operations can be performed using the

microport. The direct addressing scheme is used and any

internal register can be accessed using an 8-bit address. The

data bus can be either 8-bit or 16-bit as set by the chip I/O

access control register. Microport operation is synchronous to

CPUCLK, which must be supplied external to the AD6654 part.

CPUCLK should be less than CLK and 100 MHz.

The microport can operate in Intel mode (separate read and

write strobes) or in Motorola mode (single read/write strobe).

The MODE pin is used to select between Intel (INM, MODE =

0) and Motorola (MNM, MODE = 1) modes. Some AD6654

pins have dual functionality based on the MODE pin. Table 27

lists the pin functions for both modes.

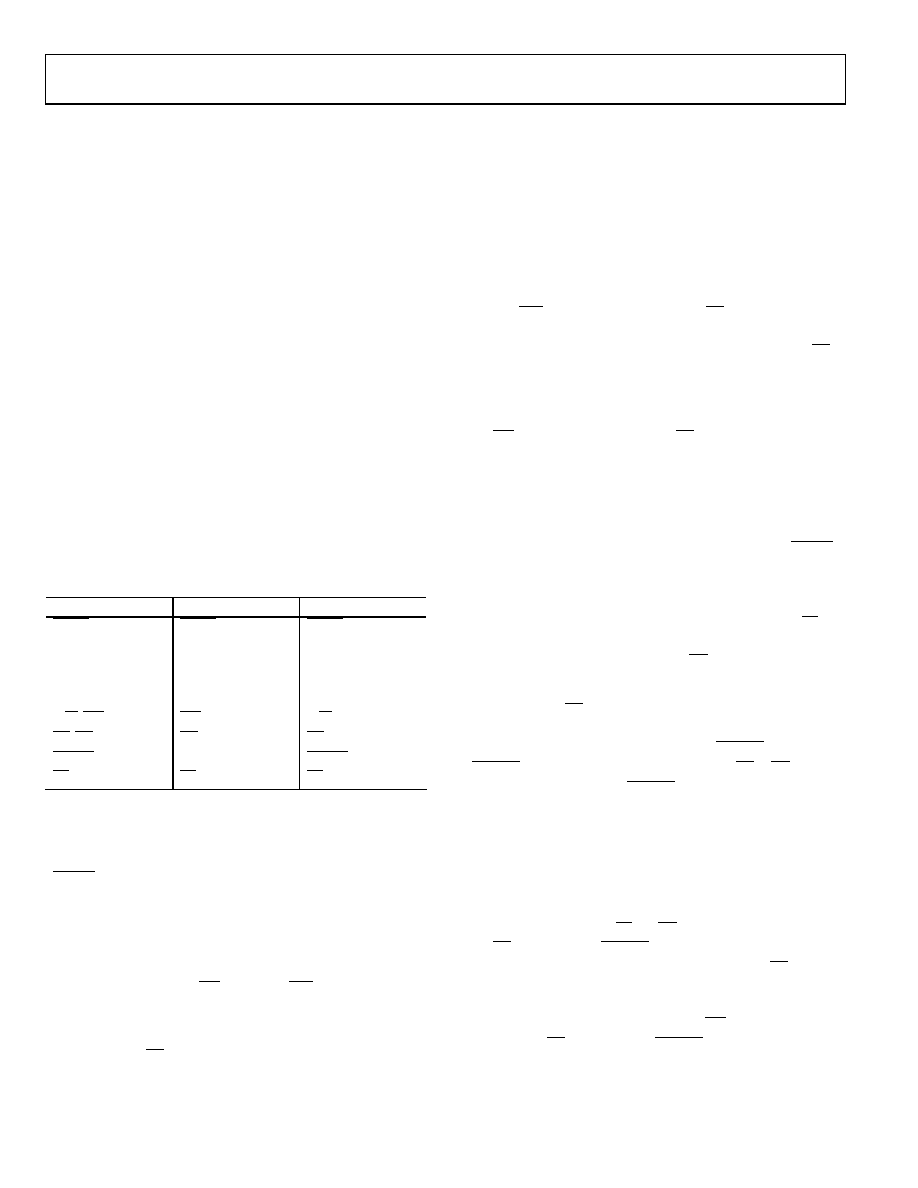

Table 27. Microport Programming Pins

Pin Name

Intel Mode

Motorola Mode

RESET

SMODE

Logic 0

MODE

Logic 0

Logic 1

A[7:0]

D[15:0]

R/W (WR)

WR

R/W

DS (RD)

RD

DS

DTACK (RDY)

RDY

DTACK

CS

INTEL (INM) MODE

The programming port performs synchronous Intel-style reads

and writes on the positive edge of the CPUCLK input when

RESET is inactive (active low signal). The CPUCLK pin is

driven by the programming device (CPUCLK of DSP or

FPGA). During a write access, the A[7:0] address bus provides

the address for access, and the D[15:0] bus (D[7:0] if the 8-bit

data bus is used) is driven by the programming device. The data

bus is driven by the AD6654 during a read operation. Intel

mode uses separate read (RD) and write (WR) active low data

strobes to indicate both the type of access and the valid data for

that access.

The chip select (CS) is an active-low input that signals when an

access is active on its programming port pins. During an access,

the AD6654 drives RDY low to indicate that it is performing the

access. When the internal read or write access is complete, the

RDY pin is pulled high. Because the RDY pin is an open-drain

output with a weak internal pull-up resistor (70 k), an

external pull-up resistor is recommended (see the DDC Design

for read and write cycles using the microport in INM mode.

For an asynchronous write operation in Intel (INM) mode, the

CPUCLK should be running. Set up the data and address buses.

Pull the WR signal low and then pull the CS signal low. The

RDY goes low to indicate that the access is taking place inter-

nally. When RDY goes high, the write cycle is complete and CS

can be pulled high to disable the microport.

For an asynchronous read operation on the Intel mode micro-

port, set up the address bus and three-state the data bus. Pull

the RD signal low and then pull the CS signal low. The RDY

goes low to indicate an internal access. When RDY goes low,

valid data is available on the data bus for read.

MOTOROLA (MNM) MODE

The programming port performs synchronous Motorola-style

reads and writes on the positive edge of CPUCLK when RESET

is inactive (active low signal). The A[7:0] bus provides the

address to access and the D[15:0] bus (D[7:0], if the 8-bit data

bus is used) is externally driven with data during a write (driven

by the AD6654 during a read). Motorola mode uses the R/W

line to indicate the type of access (Logic 1 = read, Logic 0 =

write), and the active low data strobe (DS) signal is used to

indicate valid data.

The chip select (CS) is an active-low input that signals when an

access is active on its programming port pins. When the read/

write cycle is complete, the AD6654 drives DTACK low. The

DTACK signal goes high again after either the CS or DS signal

is driven high. Because the DTACK pin is an open-drain output

with a weak internal pull-up resistor (70 k), an external pull-

up resistor is recommended (see the DDC Design Notes

section). Figure 12 and Figure 13 are the timing diagrams for

read and write cycles using the microport in MNM mode.

For an asynchronous write operation on the Motorola mode

microport, the CPUCLK should be running. Set up the data and

address buses. Pull the R/W and DS signals low and then pull

the CS signal low. The DTACK goes low after a few clock cycles

to indicate that the write access is complete and that CS can be

pulled high to disable the microport. For an asynchronous read

operation on the Motorola mode microport, set up the address

bus and three-state the data bus. Pull the RD signal low and

then pull the CS signal low. The DTACK goes low after a few

clock cycles to indicate that valid data is on the data bus.

相关PDF资料 |

PDF描述 |

|---|---|

| MS27467T21A16PA | CONN PLUG 16POS STRAIGHT W/PINS |

| VE-21J-IU-F1 | CONVERTER MOD DC/DC 36V 200W |

| MS3100R28-21S | CONN RCPT 37POS WALL MNT W/SCKT |

| VI-26H-MX-F4 | CONVERTER MOD DC/DC 52V 75W |

| VE-21H-IU-F3 | CONVERTER MOD DC/DC 52V 200W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6654XBCZ | 制造商:Analog Devices 功能描述:14-BIT, 92.16 MSPS, 4 & 6-CHANNEL WIDEBAND IF TO BASE BAND R - Bulk |

| AD6655 | 制造商:AD 制造商全称:Analog Devices 功能描述:IF Diversity Receiver |

| AD6655-125EBZ | 功能描述:BOARD EVAL W/AD6655 & SOFTWARE RoHS:是 类别:RF/IF 和 RFID >> RF 评估和开发套件,板 系列:- 标准包装:1 系列:- 类型:GPS 接收器 频率:1575MHz 适用于相关产品:- 已供物品:模块 其它名称:SER3796 |

| AD6655-125EBZ1 | 制造商:AD 制造商全称:Analog Devices 功能描述:IF Diversity Receiver |

| AD6655-150EBZ | 功能描述:BOARD EVAL FOR 150MSPS AD6655 RoHS:是 类别:RF/IF 和 RFID >> RF 评估和开发套件,板 系列:- 标准包装:1 系列:- 类型:GPS 接收器 频率:1575MHz 适用于相关产品:- 已供物品:模块 其它名称:SER3796 |

发布紧急采购,3分钟左右您将得到回复。