参数资料

| 型号: | AD73322LYRZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 29/48页 |

| 文件大小: | 0K |

| 描述: | IC ANALOG FRONT END DUAL 28-SOIC |

| 标准包装: | 27 |

| 位数: | 16 |

| 通道数: | 4 |

| 功率(瓦特): | 73mW |

| 电压 - 电源,模拟: | 2.7 V ~ 5.5 V |

| 电压 - 电源,数字: | 2.7 V ~ 5.5 V |

| 封装/外壳: | 28-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 28-SOIC W |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

AD73322L

Rev. A | Page 35 of 48

DIFFERENTIAL-TO-SINGLE-ENDED OUTPUT

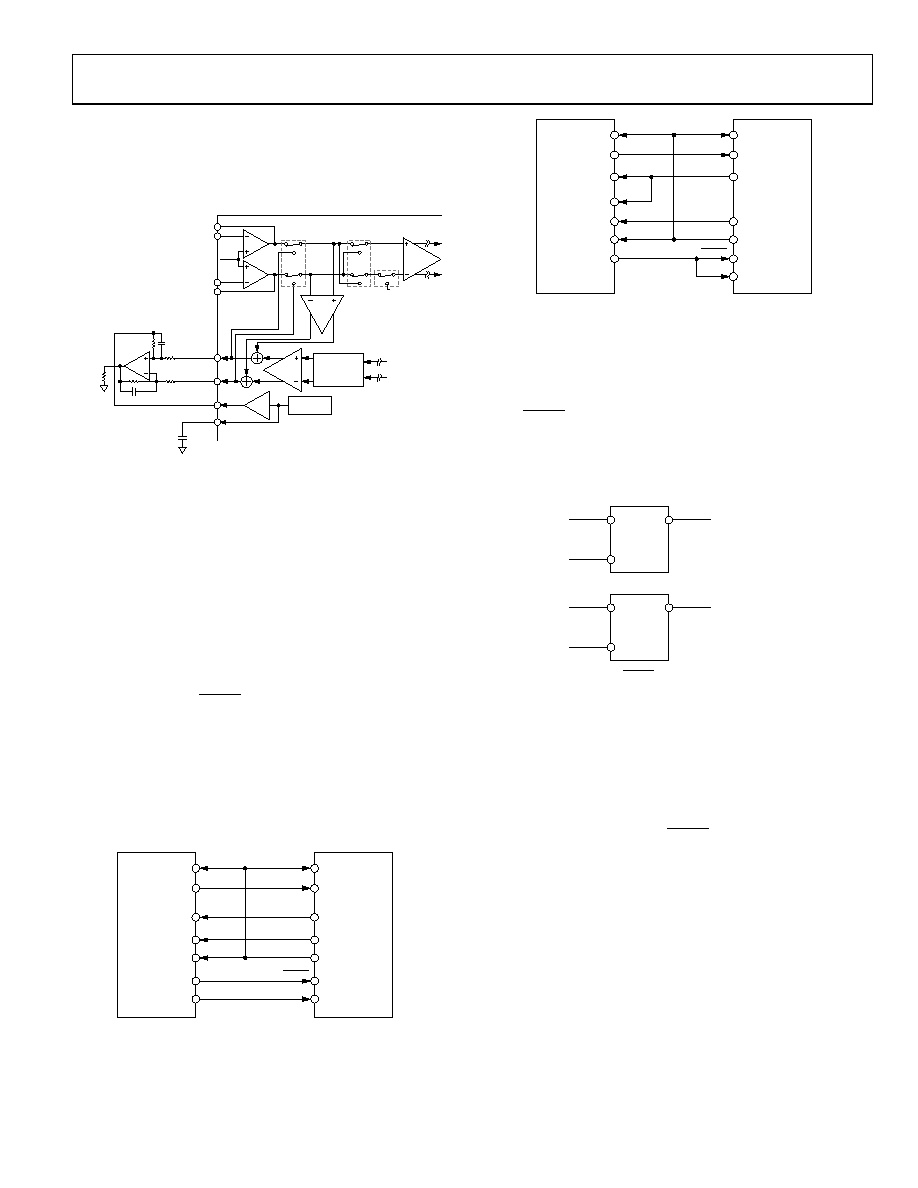

In some applications it may be desirable to convert the full

differential output of the decoder channel to a single-ended

signal. The circuit of Figure 42 shows a scheme for doing this.

CONTINUOUS

TIME

LOW-PASS

FILTER

VREF

VINP1

VFBP1

VOUTP1

VOUTN1

AD73322L

+6/–15dB

PGA

0/38dB

PGA

GAIN

±1

REFOUT

REFCAP

REFERENCE

VREF

0.1

F

00691-

042

RF

R1

RF

RLOAD

Figure 42. Example Circuit for Differential to Single-Ended

Output Conversion

DIGITAL INTERFACING

The AD73322L is designed to interface easily to most common

DSPs. The SCLK, SDO, SDOFS, SDI, and SDIFS must be con-

nected to the DSP’s serial clock, receive data, receive data

frame sync, transmit data, and transmit data frame sync pins,

respectively. The SE pin may be controlled from a parallel

output pin or flag pin such as FL0-2 on the ADSP-21xx (or XF

on the TMS320C5x) or, where SPORT power-down is not

required, it can be permanently strapped high using a suitable

pull-up resistor. The RESET pin may be connected to the

system hardware reset structure or it may also be controlled

using a dedicated control line. In the event of tying it to the

global system reset, it is advisable to operate the device in mixed

mode, which allows a software reset, otherwise there is no

convenient way of resetting the device. Figure 43 and Figure 44

show typical connections to an ADSP-218x and TMS320C5x,

respectively.

TFS

DT

SCLK

DR

RFS

ADSP-218x

DSP

AD73322L

CODEC

SDIFS

SDI

SCLK

SDO

SDOFS

FL0

FL1

RESET

SE

00691-

043

Figure 43. AD73322L Connected to ADSP-218x

FSX

DT

CLKX

DR

FSR

TMS320C5x

DSP

AD73322L

CODEC

SDIFS

SDI

SCLK

SDO

SDOFS

XF

RESET

SE

CLKR

00691-

044

Figure 44. AD73322L Connected to TMS320C5x

CASCADE OPERATION

Where it is required to configure a cascade of up to eight codecs

(four AD73322L dual codecs), ensure that the timing of the SE

and RESET signals is synchronized at each device in the

cascade. A simple D-type flip-flop is sufficient to sync each

signal to the master clock MCLK, as in Figure 45.

1/2

74HC74

CLK

DQ

DSP CONTROL

TO SE

MCLK

SE SIGNAL SYNCHRONIZED

TO MCLK

1/2

74HC74

CLK

DQ

DSP CONTROL

TO RESET

MCLK

RESET SIGNAL SYNCHRONIZED

TO MCLK

00691-

045

Figure 45. SE and RESET Sync Circuit or Cascaded Operation

Connection of a cascade of devices to a DSP, as shown in

Figure 46, is no more complicated than connecting a single

device. Instead of connecting the SDO and SDOFS to the DSP’s

Rx port, these are now daisy-chained to the SDI and SDIFS of

the next device in the cascade. The SDO and SDOFS of the final

device in the cascade are connected to the DSP’s Rx port to

complete the cascade. SE and RESET on all devices are fed from

the signals that were synchronized with the MCLK using the

circuit, as described previously. The SCLK from only one device

need be connected to the DSP’s SCLK input(s) as all devices run

at the same SCLK frequency and phase.

相关PDF资料 |

PDF描述 |

|---|---|

| AD73360ARZ | IC PROCESSOR FRONTEND 6CH 28SOIC |

| AD7352YRUZ-500RL7 | IC ADC DUAL 12BIT 3MSPS 16TSSOP |

| AD7356YRUZ-500RL7 | IC ADC DUAL 12BIT 5MSPS 16TSSOP |

| AD7357YRUZ | IC ADC DUAL14BIT 4.2MSPS 16TSSOP |

| AD7367BRUZ-500RL7 | IC ADC 14BIT SAR 1MSPS 24TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD73322LYST | 制造商:Analog Devices 功能描述: |

| AD73322LYSTZ | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| AD73360 | 制造商:AD 制造商全称:Analog Devices 功能描述:Six-Input Channel Analog Front End |

| AD73360AR | 制造商:Analog Devices 功能描述:AFE General Purpose 6ADC 16-Bit 5V 28-Pin SOIC W 制造商:Analog Devices 功能描述:IC 16-BIT ADC |

| AD73360AR-REEL | 制造商:Analog Devices 功能描述:AFE General Purpose 6ADC 16-Bit 5V 28-Pin SOIC W T/R 制造商:Analog Devices 功能描述:AFE GEN PURPOSE 6ADC 16BIT 5V/5V/5V 28SOIC W - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。