- 您现在的位置:买卖IC网 > PDF目录10149 > AD7712ARZ-REEL (Analog Devices Inc)IC ADC 24BIT SGNL CONDTNR 24SOIC PDF资料下载

参数资料

| 型号: | AD7712ARZ-REEL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 13/28页 |

| 文件大小: | 0K |

| 描述: | IC ADC 24BIT SGNL CONDTNR 24SOIC |

| 标准包装: | 1,000 |

| 位数: | 24 |

| 采样率(每秒): | 1.03k |

| 数据接口: | 串行 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 45mW |

| 电压电源: | 模拟和数字,双 ± |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 24-SOIC W |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 1 个单端,单极;1 个差分,单极;1 个差分,双极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

REV. F

–20–

AD7712

DIGITAL INTERFACE

The AD7712’s serial communications port provides a flexible

arrangement to allow easy interfacing to industry-standard

microprocessors, microcontrollers, and digital signal processors.

A serial read to the AD7712 can access data from the output

register, the control register, or the calibration registers. A serial

write to the AD7712 can write data to the control register or the

calibration registers.

Two different modes of operation are available, optimized for

different types of interfaces where the AD7712 can act either as

master in the system (it provides the serial clock) or as slave (an

external serial clock can be provided to the AD7712). These

two modes, labeled self-clocking mode and external clocking

mode, are discussed in detail in the following sections.

Self-Clocking Mode

The AD7712 is configured for its self-clocking mode by tying

the MODE pin high. In this mode, the AD7712 provides the

serial clock signal used for the transfer of data to and from the

AD7712. This self-clocking mode can be used with processors

that allow an external device to clock their serial port, including

most digital signal processors and microcontrollers such as the

68HC11 and 68HC05. It also allows easy interfacing to serial

parallel conversion circuits in systems with parallel data com-

munication, allowing interfacing to 74XX299 universal shift

registers without any additional decoding. In the case of shift

registers, the serial clock line should have a pull-down resistor

instead of the pull-up resistor shown in Figures 11 and 12.

Read Operation

Data can be read from the output register, the control register, or

the calibration registers. A0 determines whether the data read

accesses data from the control register or from the output/calibra-

tion registers. This A0 signal must remain valid for the duration

of the serial read operation. With A0 high, data is accessed from

either the output register or from the calibration registers. With

A0 low, data is accessed from the control register.

The function of the

DRDY line is dependent on only the output

update rate of the device and the reading of the output data

register.

DRDY goes low when a new data-word is available in

the output data register. It is reset high when the last bit of data

(either 16th bit or 24th bit) is read from the output register. If

data is not read from the output register, the

DRDY line will

remain low. The output register will continue to be updated at

the output update rate, but

DRDY will not indicate this. A read

from the device in this circumstance will access the most recent

word in the output register. If a new data-word becomes avail-

able to the output register while data is being read from the

output register,

DRDY will not indicate this and the new data-

word will be lost to the user.

DRDY is not affected by reading

from the control register or the calibration registers.

Data can be accessed from the output data register only when

DRDY is low. If RFS goes low with DRDY high, no data trans-

fer will take place.

DRDY does not have any effect on reading

data from the control register or from the calibration registers.

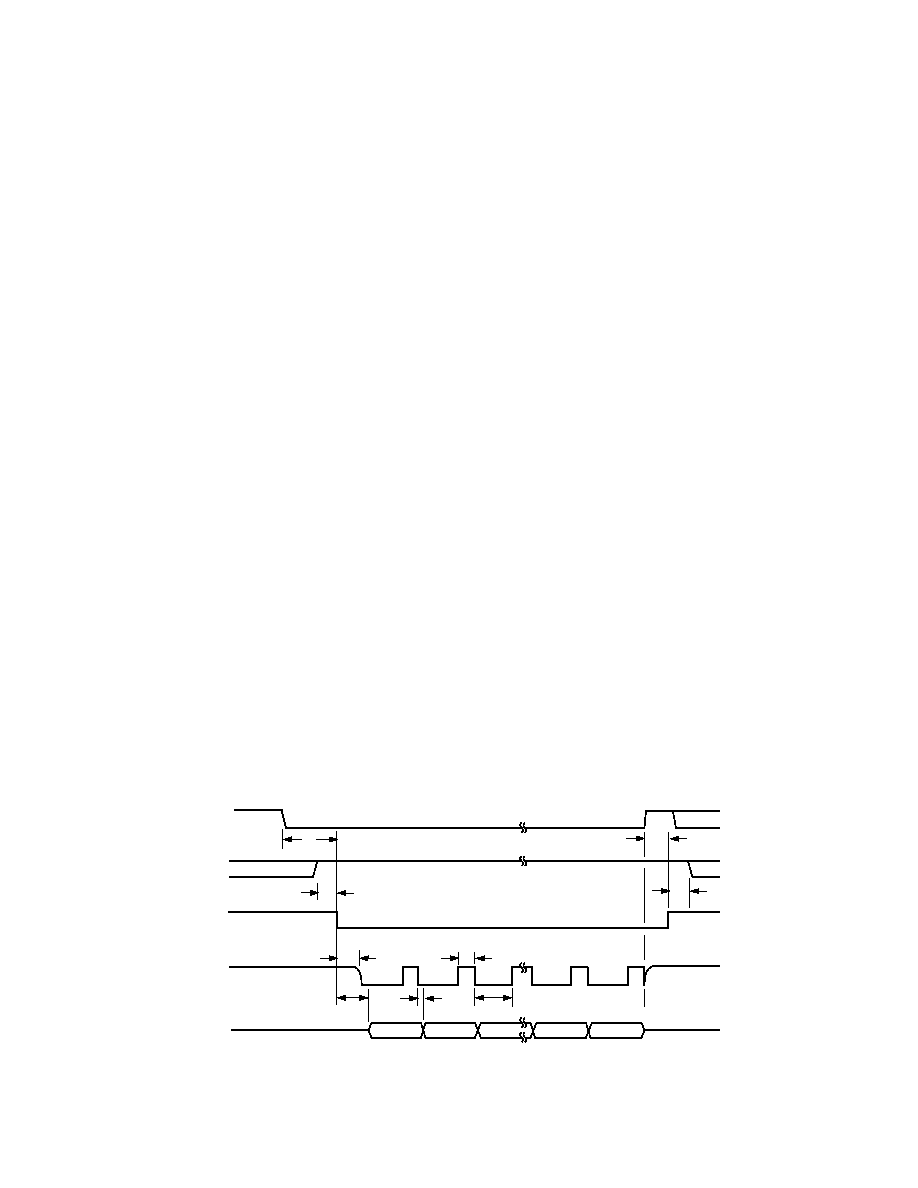

Figure 11 shows a timing diagram for reading from the AD7712

in the self-clocking mode. This read operation shows a read

from the AD7712’s output data register. A read from the con-

trol register or calibration registers is similar, but, in these cases,

the

DRDY line is not related to the read function. Depending

on the output update rate, it can go low at any stage in the

control/calibration register read cycle without affecting the read

and its status should be ignored. A read operation from either

the control or calibration registers must always read 24 bits of

data from the respective register.

Figure 11 shows a read operation from the AD7712. For the

timing diagram shown, it is assumed that there is a pull-up

resistor on the SCLK output. With

DRDY low, the RFS input

is brought low.

RFS going low enables the serial clock of the

AD7712 and also places the MSB of the word on the serial data

line. All subsequent data bits are clocked out on a high to low

transition of the serial clock and are valid prior to the following

rising edge of this clock. The final active falling edge of SCLK

clocks out the LSB, and this LSB is valid prior to the final active

rising edge of SCLK. Coincident with the next falling edge of

SCLK,

DRDY is reset high. DRDY going high turns off the

SCLK and the SDATA outputs, which means that the data

hold time for the LSB is slightly shorter than for all other bits.

SDATA (O)

SCLK (O)

THREE-STATE

RFS (I)

A0 (I)

DRDY (O)

MSB

LSB

t2

t3

t4

t5

t6

t7

t8

t9

t10

Figure 11. Self-Clocking Mode, Output Data Read Operation

相关PDF资料 |

PDF描述 |

|---|---|

| VE-2NN-MX-F4 | CONVERTER MOD DC/DC 18.5V 75W |

| D38999/20WB98SA | CONN RCPT 6POS WALL MNT W/SCKT |

| PXA911/04/P | CONN PLUG 4POS W/PINS LG CABLE |

| VE-2NN-MX-F3 | CONVERTER MOD DC/DC 18.5V 75W |

| VE-B30-IV-F2 | CONVERTER MOD DC/DC 5V 150W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7712ARZ-REEL7 | 功能描述:IC ADC 24BIT SGNL CONDTNR 24SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| AD7712EB | 制造商:AD 制造商全称:Analog Devices 功能描述:LC 2 MOS Signal Conditioning ADC(229.08 k) |

| AD7712SQ | 制造商:Analog Devices 功能描述: 制造商:Rochester Electronics LLC 功能描述:24 BIT SIGMA DELTA ADC IC - Bulk |

| AD7713 | 制造商:AD 制造商全称:Analog Devices 功能描述:LC2MOS Loop-Powered Signal Conditioning ADC |

发布紧急采购,3分钟左右您将得到回复。