- 您现在的位置:买卖IC网 > PDF目录16854 > AD9522-0/PCBZ (Analog Devices Inc)BOARD EVAL FOR AD9522-0 CLK GEN PDF资料下载

参数资料

| 型号: | AD9522-0/PCBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 33/84页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD9522-0 CLK GEN |

| 设计资源: | AD9522 Eval Board Schematic AD9522 BOM |

| 标准包装: | 1 |

| 主要目的: | 计时,时钟发生器 |

| 嵌入式: | 否 |

| 已用 IC / 零件: | AD9522-0 |

| 主要属性: | 12 LVDS/24 CMOS 输出,2.8 GHz VCO |

| 次要属性: | I²C & SPI 接口 |

| 已供物品: | 板 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页当前第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页

AD9522-0

Rev. 0 | Page 39 of 84

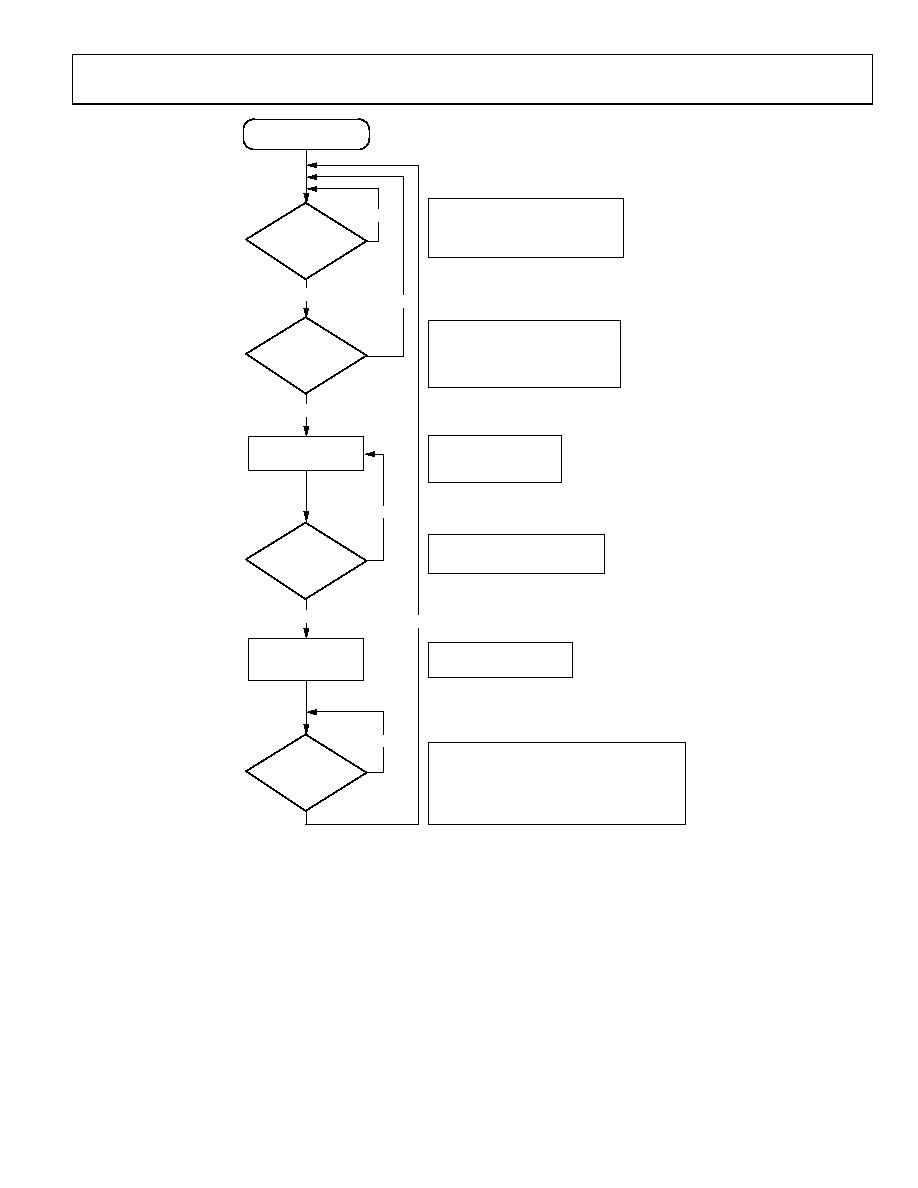

NO

YES

PLL ENABLED

DLD == LOW

WAS

LD PIN == HIGH

WHEN DLD WENT

LOW?

HIGH IMPEDANCE

CHARGE PUMP

REFERENCE

EDGE AT PFD?

RELEASE

CHARGE PUMP

HIGH IMPEDANCE

DLD == HIGH

LOOP OUT OF LOCK. DIGITAL LOCK

DETECT SIGNAL GOES LOW WHEN THE

LOOP LEAVES LOCK AS DETERMINED

BY THE PHASE DIFFERENCE AT THE

INPUT OF THE PFD.

ANALOG LOCK DETECT PIN INDICATES

LOCK WAS PREVIOUSLY ACHIEVED.

(0x01D[3] = 1; USE LD PIN VOLTAGE

WITH HOLDOVER.

0x01D[3] = 0; IGNORE LD PIN VOLTAGE,

TREAT LD PIN AS ALWAYS HIGH.)

CHARGE PUMP IS MADE

HIGH IMPEDANCE.

PLL COUNTERS CONTINUE

OPERATING NORMALLY.

CHARGE PUMP REMAINS HIGH

IMPEDANCE UNTIL THE REFERENCE

RETURNS.

TAKE CHARGE PUMP OUT OF

HIGH IMPEDANCE. PLL CAN

NOW RESETTLE.

WAIT FOR DLD TO GO HIGH. THIS TAKES

5 TO 255 CYCLES (PROGRAMMING OF THE DLD

DELAY COUNTER) WITH THE REFERENCE AND

FEEDBACK CLOCKS INSIDE THE LOCK WINDOW AT

THE PFD. THIS ENSURES THAT THE HOLDOVER

FUNCTION WAITS FOR THE PLL TO SETTLE AND LOCK

BEFORE THE HOLDOVER FUNCTION CAN BE

RETRIGGERED.

0

72

19

-06

9

Figure 47. Flowchart of Automatic/Internal Holdover Mode

The holdover function senses the logic level of the LD pin as a

condition to enter holdover. The signal at LD can be from the

DLD, ALD, or current source LD (CSDLD) mode. It is possible

to disable the LD comparator (0x01D[3]), which causes the

holdover function to always sense LD as being high. If DLD is

used, it is possible for the DLD signal to chatter while the PLL is

reacquiring lock. The holdover function may retrigger, thereby

preventing the holdover mode from terminating. Use of the

current source lock detect mode is recommended to avoid this

situation (see the Current Source Digital Lock Detect (CSDLD)

section).

When in holdover mode, the charge pump stays in a high

impedance state as long as there is no reference clock present.

As in the external holdover mode, the B counter (in the N divider)

is reset synchronously with the charge pump leaving the high

impedance state on the reference path PFD event. This helps

align the edges out of the R and N dividers for faster settling of

the PLL and reduces frequency errors during settling. Because

the prescaler is not reset, this feature works best when the B and

R numbers are close because this results in a smaller phase

difference for the loop to settle out.

相关PDF资料 |

PDF描述 |

|---|---|

| EBM22DCMT-S288 | CONN EDGECARD 44POS .156 EXTEND |

| RNF-100-MINI-SPL-3/64-BK | HEATSHRINK RNF-100 3/64"X100'BLK |

| V110B36E150B3 | CONVERTER MOD DC/DC 36V 150W |

| RNF-100-MINI-SPL-1/16-BK | HEATSHRINK RNF-100 1/16"X75'BLK |

| H4PXS-2036G | DIP CABLE - HDP20S/AE20G/X |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9522-1 | 制造商:AD 制造商全称:Analog Devices 功能描述:12 LVDS/24 CMOS Output Clock Generator with Integrated 2.4 GHz VCO |

| AD9522-1/PCBZ | 功能描述:BOARD EVAL FOR AD9522-1 CLK GEN RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| AD9522-1BCPZ | 功能描述:IC CLOCK GEN 2.5GHZ VCO 64LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

| AD9522-1BCPZ-REEL7 | 功能描述:IC CLOCK GEN 2.5GHZ VCO 64LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

| AD9522-2 | 制造商:AD 制造商全称:Analog Devices 功能描述:12 LVDS/24 CMOS Output Clock Generator with Integrated 2.2 GHz VCO |

发布紧急采购,3分钟左右您将得到回复。