- 您现在的位置:买卖IC网 > PDF目录19388 > ADSP-2191MBSTZ-140 (Analog Devices Inc)IC DSP CONTROLLER 16BIT 144LQFP PDF资料下载

参数资料

| 型号: | ADSP-2191MBSTZ-140 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 47/48页 |

| 文件大小: | 0K |

| 描述: | IC DSP CONTROLLER 16BIT 144LQFP |

| 标准包装: | 1 |

| 系列: | ADSP-21xx |

| 类型: | 定点 |

| 接口: | 主机接口,SPI,SSP,UART |

| 时钟速率: | 140MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 160kB |

| 电压 - 输入/输出: | 3.00V,3.30V |

| 电压 - 核心: | 2.50V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-LQFP |

| 供应商设备封装: | 144-LQFP(20x20) |

| 包装: | 托盘 |

| 其它名称: | ADSP-2191MBSTZ140 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页当前第47页第48页

ADSP-2191M

–8–

REV. A

Host can directly access the DSP’s entire memory space map,

boot memory space, and internal I/O space. To access the DSP’s

internal memory space, a Host steals one cycle per access from

the DSP. A Host access to the DSP’s external memory uses the

external port interface and does not stall (or steal cycles from)

the DSP’s core. Because a Host can access internal I/O memory

space, a Host can control any of the DSP’s I/O mapped

peripherals.

The Host port is most efficient when using the DSP as a slave

and uses DMA to automate the incrementing of addresses for

these accesses. In this case, an address does not have to be trans-

ferred from the Host for every data transfer.

Host Port Acknowledge (HACK) Modes

The Host port supports a number of modes (or protocols) for

generating a HACK output for the host. The host selects ACK

or Ready modes using the HACK_P and HACK pins. The Host

port also supports two modes for address control: Address Latch

Enable (ALE) and Address Cycle Control (ACC) modes. The

DSP auto-detects ALE versus ACC mode from the HALE and

HWR inputs.

The Host port HACK signal polarity is selected (only at reset) as

active high or active low, depending on the value driven on the

HACK_P pin.The HACK polarity is stored into the Host port

configuration register as a read only bit.

The DSP uses HACK to indicate to the Host when to complete

an access. For a read transaction, a Host can proceed and

complete an access when valid data is present in the read buffer

and the Host port is not busy doing a write. For a write transac-

tions, a Host can complete an access when the write buffer is not

full and the Host port is not busy doing a write.

Two mode bits in the Host Port configuration register HPCR

[7:6] define the functionality of the HACK line. HPCR6 is ini-

tialized at reset based on the values driven on HACK and

HACK_P pins (shown in Table 5); HPCR7 is always cleared (0)

at reset. HPCR [7:6] can be modified after reset by a write access

to the Host port configuration register.

The functional modes selected by HPCR [7:6] are as follows

(assuming active high signal):

ACK Mode—Acknowledge is active on strobes; HACK

goes high from the leading edge of the strobe to indicate

when the access can complete. After the Host samples the

HACK active, it can complete the access by removing the

strobe.The Host port then removes the HACK.

Ready Mode—Ready active on strobes, goes low to insert

waitstate during the access.If the Host port cannot

complete the access, it deasserts the HACK/READY line.

In this case, the Host has to extend the access by keeping

the strobe asserted. When the Host samples the HACK

asserted, it can then proceed and complete the access by

deasserting the strobe.

While in Address Cycle Control (ACC) mode and the ACK or

Ready acknowledge modes, the HACK is returned active for any

address cycle.

Host Port Chip Selects

There are two chip-select signals associated with the Host port:

HCMS and HCIOMS. The Host Chip Memory Select (HCMS)

lets the Host select the DSP and directly access the DSP’s inter-

nal/external memory space or boot memory space. The Host

Chip I/O Memory Select (

HCIOMS) lets the Host select the

DSP and directly access the DSP’s internal I/O memory space.

Before starting a direct access, the Host configures Host port

interface registers, specifying the width of external data bus

(8- or 16-bit) and the target address page (in the IJPG register).

The DSP generates the needed memory select signals during the

access, based on the target address. The Host port interface

combines the data from one, two, or three consecutive Host

accesses (up to one 24-bit value) into a single DMA bus access

to prefetch Host direct reads or to post direct writes. During

assembly of larger words, the Host port interface asserts ACK for

each byte access that does not start a read or complete a write.

Otherwise, the Host port interface asserts ACK when it has

completed the memory access successfully.

DSP Serial Ports (SPORTs)

The ADSP-2191M incorporates three complete synchronous

serial ports (SPORT0, SPORT1, and SPORT2) for serial and

multiprocessor communications. The SPORTs support the

following features:

Bidirectional operation—each SPORT has independent

transmit and receive pins.

Double-buffered transmit and receive ports—each port

has a data register for transferring data words to and from

memory and shift registers for shifting data in and out of

the data registers.

Clocking—each transmit and receive port can either use

an external serial clock (

40 MHz) or generate its own, in

frequencies ranging from 19 Hz to 40 MHz.

Word length—each SPORT supports serial data words

from 3 to 16 bits in length transferred in Big Endian

(MSB) or Little Endian (LSB) format.

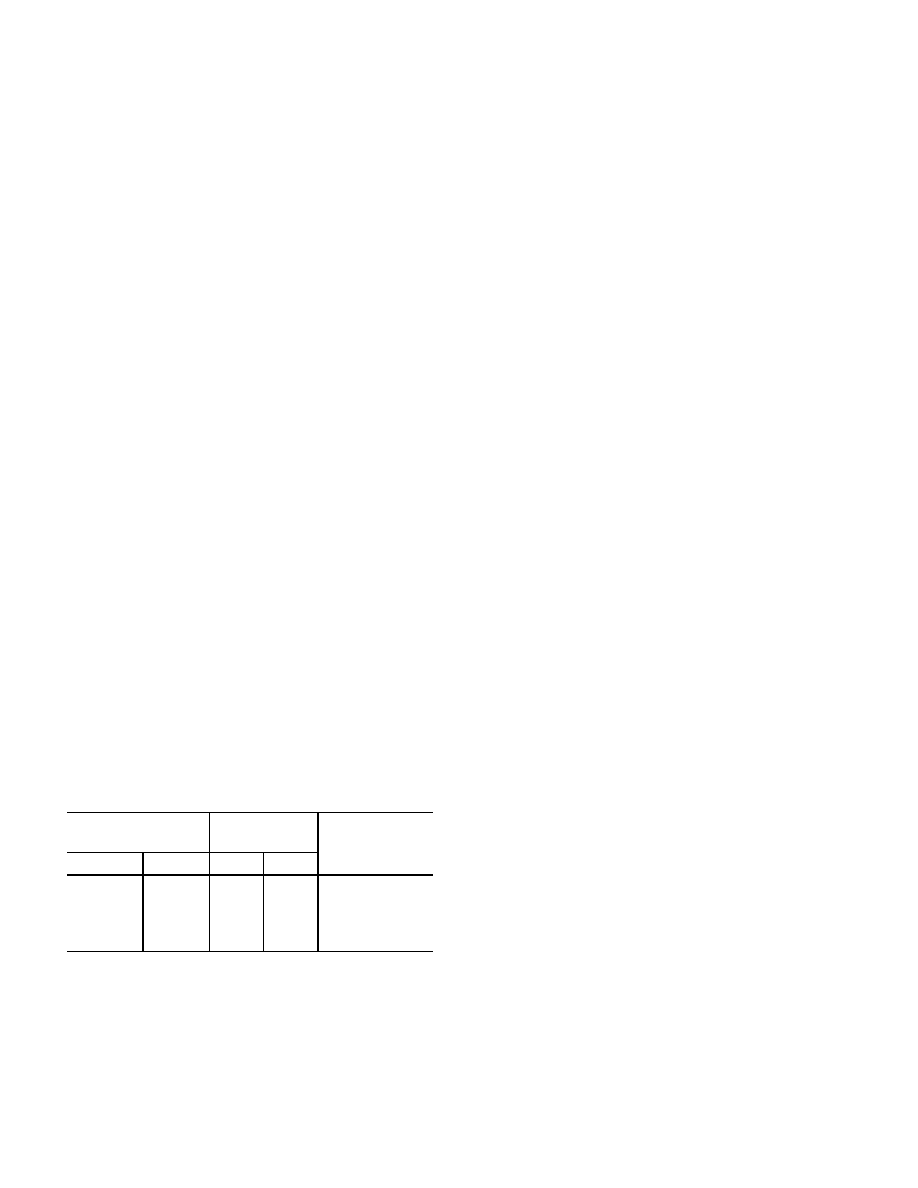

Table 5. Host Port Acknowledge Mode Selection

Values Driven At

Reset

HPCR [7:6]

Initial Values

Acknowledge

Mode

HACK_P

HACK

Bit 7

Bit 6

0

1

Ready Mode

01

0

ACK Mode

10

0

ACK Mode

1

0

1

Ready Mode

相关PDF资料 |

PDF描述 |

|---|---|

| TLJA686M006R0500 | CAP TANT 68UF 6.3V 20% 1206 |

| MC7808CD2T | IC REG LDO 8V 1A D2PAK-3 |

| SWS600L-3 | POWER SUPPLY 3.3V 120A SGL OTPT |

| MC7808BT | IC REG LDO 8V 1A TO220AB |

| TLJA476M010R0600 | CAP TANT 47UF 10V 20% 1206 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-2191MKCA-160 | 功能描述:IC DSP CONTROLLER 16BIT 144MBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:ADSP-21xx 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-2191MKCAZ-160 | 功能描述:IC DSP CONTROLLER 16BIT 144MBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:ADSP-21xx 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-2191MKST-160 | 制造商:Analog Devices 功能描述:DSP 16-Bit 160MHz 160MIPS 144-Pin LQFP 制造商:Analog Devices 功能描述:Digital Signal Processor IC Supply Volta |

| ADSP-2191MKSTZ-160 | 功能描述:IC DSP CONTROLLER 16BIT 144LQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:ADSP-21xx 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-2195MBCA-140 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 24-Bit 140MHz 140MIPS 144-Pin CSP-BGA 制造商:Rochester Electronics LLC 功能描述:16-BIT,140 MIPS, 2.5V, 80KBYTES RAM - Bulk |

发布紧急采购,3分钟左右您将得到回复。