- 您现在的位置:买卖IC网 > PDF目录19388 > ADSP-BF537BBC-5A (Analog Devices Inc)IC DSP CTLR 16BIT 182CSPBGA PDF资料下载

参数资料

| 型号: | ADSP-BF537BBC-5A |

| 厂商: | Analog Devices Inc |

| 文件页数: | 6/68页 |

| 文件大小: | 0K |

| 描述: | IC DSP CTLR 16BIT 182CSPBGA |

| 产品培训模块: | Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services |

| 标准包装: | 1 |

| 系列: | Blackfin® |

| 类型: | 定点 |

| 接口: | CAN,SPI,SSP,TWI,UART |

| 时钟速率: | 500MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 132kB |

| 电压 - 输入/输出: | 2.50V,3.30V |

| 电压 - 核心: | 1.26V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 182-LFBGA,CSPBGA |

| 供应商设备封装: | 182-CSPBGA(12x12) |

| 包装: | 托盘 |

| 配用: | ADZS-BF537-ASKIT-ND - BOARD EVAL SKIT ADSP-BF537 ADZS-BFAUDIO-EZEXT-ND - BOARD EVAL AUDIO BLACKFIN ADZS-BF537-EZLITE-ND - BOARD EVAL ADSP-BF537 ADZS-BFAV-EZEXT-ND - BOARD DAUGHT ADSP-BF533,37,61KIT ADZS-BF537-STAMP-ND - SYSTEM DEV FOR ADSP-BF537 |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

Rev. J

|

Page 14 of 68

|

February 2014

Hibernate State—Maximum Static Power Savings

The hibernate state maximizes static power savings by disabling

the voltage and clocks to the processor core (CCLK) and to all of

the synchronous peripherals (SCLK). The internal voltage regu-

lator for the processor can be shut off by writing b#00 to the

FREQ bits of the VR_CTL register. This disables both CCLK

and SCLK. Furthermore, it sets the internal power supply volt-

age (VDDINT) to 0 V to provide the greatest power savings. To

preserve the processor state, prior to removing power, any criti-

cal information stored internally (memory contents, register

contents, etc.) must be written to a nonvolatile storage device.

Since VDDEXT is still supplied in this state, all of the external pins

three-state, unless otherwise specified. This allows other devices

that are connected to the processor to still have power applied

without drawing unwanted current.

The Ethernet or CAN modules can wake up the internal supply

regulator. If the PH6 pin does not connect as the PHYINT sig-

nal to an external PHY device, it can be pulled low by any other

device to wake the processor up. The regulator can also be

woken up by a real-time clock wake-up event or by asserting the

RESET pin. All hibernate wake-up events initiate the hardware

reset sequence. Individual sources are enabled by the VR_CTL

register.

With the exception of the VR_CTL and the RTC registers, all

internal registers and memories lose their content in the hiber-

nate state. State variables can be held in external SRAM or

SDRAM. The SCKELOW bit in the VR_CTL register provides a

means of waking from hibernate state without disrupting a self-

refreshing SDRAM, provided that there is also an external pull-

down on the SCKE pin.

Power Savings

As shown in Table 5, the processors support three different

power domains which maximizes flexibility, while maintaining

compliance with industry standards and conventions. By isolat-

ing the internal logic of the processor into its own power

domain, separate from the RTC and other I/O, the processor

can take advantage of dynamic power management, without

affecting the RTC or other I/O devices. There are no sequencing

requirements for the various power domains.

The dynamic power management feature allows both the pro-

cessor’s input voltage (VDDINT) and clock frequency (fCCLK) to be

dynamically controlled.

The power dissipated by a processor is largely a function of its

clock frequency and the square of the operating voltage. For

example, reducing the clock frequency by 25% results in a 25%

reduction in power dissipation, while reducing the voltage by

25% reduces power dissipation by more than 40%. Further,

these power savings are additive, in that if the clock frequency

and supply voltage are both reduced, the power savings can be

dramatic, as shown in the following equations.

The power savings factor (PSF) is calculated as:

where:

fCCLKNOM is the nominal core clock frequency

fCCLKRED is the reduced core clock frequency

VDDINTNOM is the nominal internal supply voltage

VDDINTRED is the reduced internal supply voltage

tNOM is the duration running at fCCLKNOM

tRED is the duration running at fCCLKRED

The percent power savings is calculated as

VOLTAGE REGULATION

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors pro-

vide an on-chip voltage regulator that can generate appropriate

Conditions on Page 23 for regulator tolerances and acceptable

VDDEXT ranges for specific models.

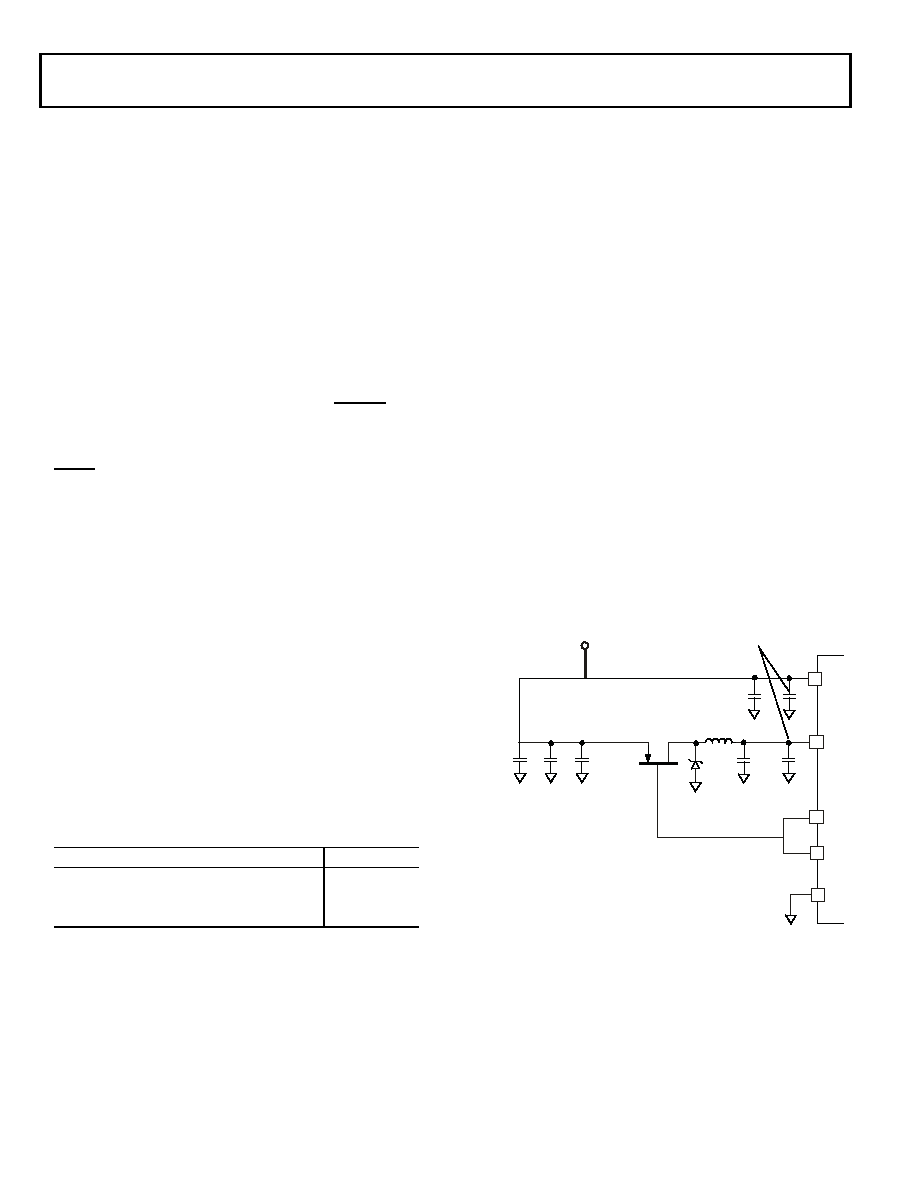

Figure 5 shows the typical external components required to

complete the power management system. The regulator con-

trols the internal logic voltage levels and is programmable with

the voltage regulator control register (VR_CTL) in increments

of 50 mV. To reduce standby power consumption, the internal

voltage regulator can be programmed to remove power to the

processor core while keeping I/O power supplied. While in

Table 5. Power Domains

Power Domain

VDD Range

All internal logic, except RTC

VDDINT

RTC internal logic and crystal I/O

VDDRTC

All other I/O

VDDEXT

Figure 5. Voltage Regulator Circuit

PSF

fCCLKRED

fCCLKNOM

---------------------

VDDINTRED

VDDINTNOM

--------------------------

2

tRED

tNOM

-----------

=

% power savings

1

PSF

–

100%

=

VDDEXT

(LOW-INDUCTANCE)

VDDINT

VROUT

100μF

VROUT

GND

SHORT AND LOW-

INDUCTANCE WIRE

VDDEXT

+

100μF

10μF

LOW ESR

100nF

SET OF DECOUPLING

CAPACITORS

FDS9431A

ZHCS1000

NOTE: DESIGNER SHOULD MINIMIZE

TRACE LENGTH TO FDS9431A.

10μH

相关PDF资料 |

PDF描述 |

|---|---|

| MC78L18ACP | IC REG LDO 18V .1A TO92 |

| TPSC107M010R0150 | CAP TANT 100UF 10V 20% 2312 |

| MC78L15ACP | IC REG LDO 15V .1A TO92 |

| MC78L12ACP | IC REG LDO 12V .1A TO92 |

| MC78L12ABP | IC REG LDO 12V .1A TO92 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-BF537BBC-5AV | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| ADSP-BF537BBCZ-5A | 功能描述:数字信号处理器和控制器 - DSP, DSC Blackfin processor 500MHz 132KB SRAM RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| ADSP-BF537BBCZ-5A | 制造商:Analog Devices 功能描述:Digital Signal Processor IC |

| ADSP-BF537BBCZ-5AV | 功能描述:IC DSP CTLR 16BIT 182CSPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-BF537BBCZ-5AV | 制造商:Analog Devices 功能描述:Digital Signal Processor IC |

发布紧急采购,3分钟左右您将得到回复。