- 您现在的位置:买卖IC网 > PDF目录19388 > ADSP-BF537BBC-5A (Analog Devices Inc)IC DSP CTLR 16BIT 182CSPBGA PDF资料下载

参数资料

| 型号: | ADSP-BF537BBC-5A |

| 厂商: | Analog Devices Inc |

| 文件页数: | 68/68页 |

| 文件大小: | 0K |

| 描述: | IC DSP CTLR 16BIT 182CSPBGA |

| 产品培训模块: | Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services |

| 标准包装: | 1 |

| 系列: | Blackfin® |

| 类型: | 定点 |

| 接口: | CAN,SPI,SSP,TWI,UART |

| 时钟速率: | 500MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 132kB |

| 电压 - 输入/输出: | 2.50V,3.30V |

| 电压 - 核心: | 1.26V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 182-LFBGA,CSPBGA |

| 供应商设备封装: | 182-CSPBGA(12x12) |

| 包装: | 托盘 |

| 配用: | ADZS-BF537-ASKIT-ND - BOARD EVAL SKIT ADSP-BF537 ADZS-BFAUDIO-EZEXT-ND - BOARD EVAL AUDIO BLACKFIN ADZS-BF537-EZLITE-ND - BOARD EVAL ADSP-BF537 ADZS-BFAV-EZEXT-ND - BOARD DAUGHT ADSP-BF533,37,61KIT ADZS-BF537-STAMP-ND - SYSTEM DEV FOR ADSP-BF537 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页当前第68页

Rev. J

|

Page 9 of 68

|

February 2014

In addition to the dedicated peripheral DMA channels, there are

two memory DMA channels provided for transfers between the

various memories of the processor system. This enables trans-

fers of blocks of data between any of the memories—including

external SDRAM, ROM, SRAM, and flash memory—with mini-

mal processor intervention. Memory DMA transfers can be

controlled by a very flexible descriptor-based methodology or

by a standard register-based autobuffer mechanism.

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors also

have an external DMA controller capability via dual external

DMA request pins when used in conjunction with the external

bus interface unit (EBIU). This functionality can be used when a

high speed interface is required for external FIFOs and high

bandwidth communications peripherals such as USB 2.0. It

allows control of the number of data transfers for memDMA.

The number of transfers per edge is programmable. This feature

can be programmed to allow memDMA to have an increased

priority on the external bus relative to the core.

REAL-TIME CLOCK

The real-time clock (RTC) provides a robust set of digital watch

features, including current time, stopwatch, and alarm. The

RTC is clocked by a 32.768 kHz crystal external to the

processor. The RTC peripheral has dedicated power supply pins

so that it can remain powered up and clocked even when the

rest of the processor is in a low power state. The RTC provides

several programmable interrupt options, including interrupt

per second, minute, hour, or day clock ticks, interrupt on pro-

grammable stopwatch countdown, or interrupt at a

programmed alarm time.

The 32.768 kHz input clock frequency is divided down to a 1 Hz

signal by a prescaler. The counter function of the timer consists

of four counters: a 60-second counter, a 60-minute counter, a

24-hour counter, and an 32,768-day counter.

When enabled, the alarm function generates an interrupt when

the output of the timer matches the programmed value in the

alarm control register. There are two alarms: The first alarm is

for a time of day, while the second alarm is for a day and time of

that day.

The stopwatch function counts down from a programmed

value, with one-second resolution. When the stopwatch is

enabled and the counter underflows, an interrupt is generated.

Like the other peripherals, the RTC can wake up the processor

from sleep mode upon generation of any RTC wake-up event.

Additionally, an RTC wake-up event can wake up the processor

from deep sleep mode, and wake up the on-chip internal voltage

regulator from the hibernate operating mode.

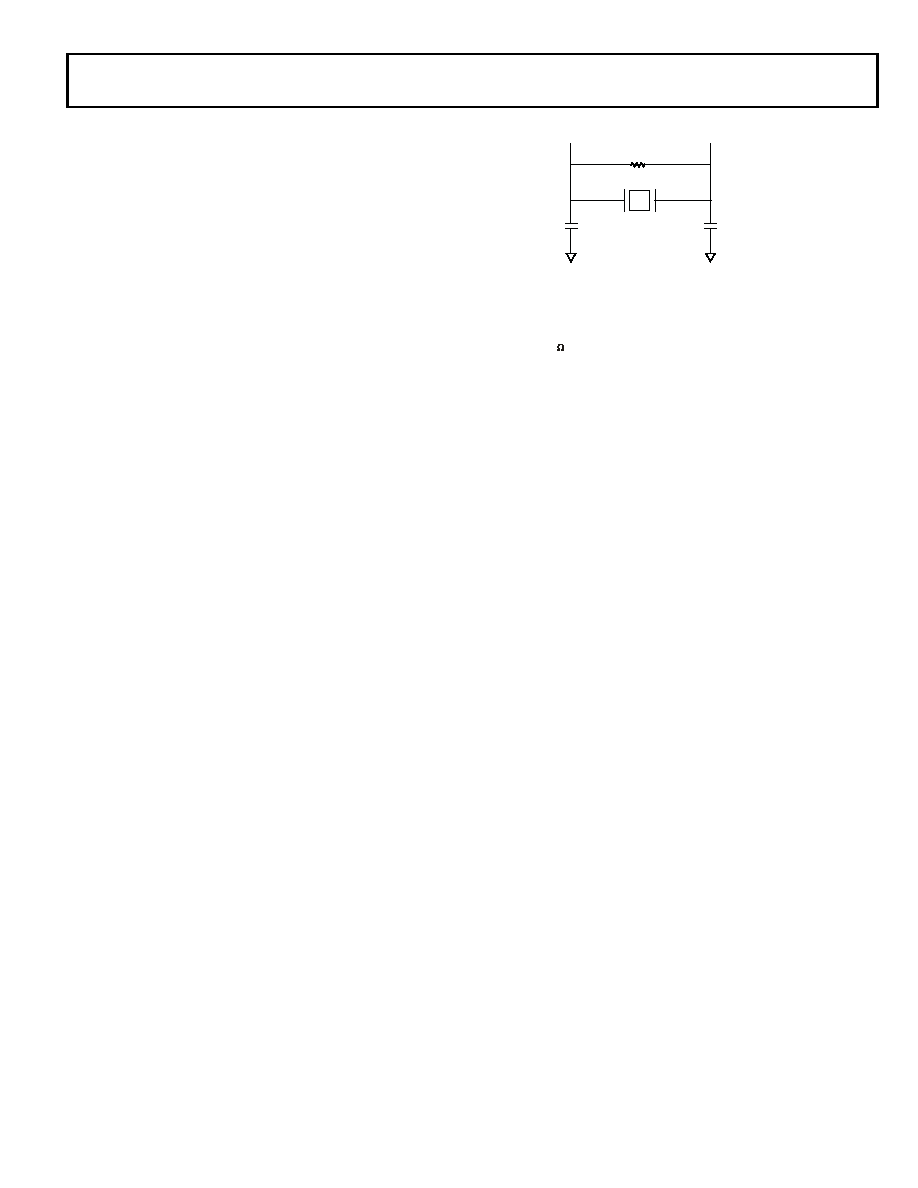

Connect RTC pins RTXI and RTXO with external components

as shown in Figure 4.

WATCHDOG TIMER

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors

include a 32-bit timer that can be used to implement a software

watchdog function. A software watchdog can improve system

availability by forcing the processor to a known state through

generation of a system reset, nonmaskable interrupt (NMI), or

general-purpose interrupt, if the timer expires before being reset

by software. The programmer initializes the count value of the

timer, enables the appropriate interrupt, then enables the timer.

Thereafter, the software must reload the counter before it

counts to zero from the programmed value. This protects the

system from remaining in an unknown state where software,

which would normally reset the timer, has stopped running due

to an external noise condition or software error.

If configured to generate a hardware reset, the watchdog timer

resets both the core and the processor peripherals. After a reset,

software can determine if the watchdog was the source of the

hardware reset by interrogating a status bit in the watchdog

timer control register.

The timer is clocked by the system clock (SCLK), at a maximum

frequency of fSCLK.

TIMERS

There are nine general-purpose programmable timer units in

the processor. Eight timers have an external pin that can be con-

figured either as a pulse-width modulator (PWM) or timer

output, as an input to clock the timer, or as a mechanism for

measuring pulse widths and periods of external events. These

timers can be synchronized to an external clock input to the sev-

eral other associated PF pins, to an external clock input to the

PPI_CLK input pin, or to the internal SCLK.

The timer units can be used in conjunction with the two UARTs

and the CAN controller to measure the width of the pulses in

the data stream to provide a software auto-baud detect function

for the respective serial channels.

The timers can generate interrupts to the processor core provid-

ing periodic events for synchronization, either to the system

clock or to a count of external signals.

In addition to the eight general-purpose programmable timers,

a ninth timer is also provided. This extra timer is clocked by the

internal processor clock and is typically used as a system tick

clock for generating periodic interrupts in an operating system.

Figure 4. External Components for RTC

RTXO

C1

C2

X1

SUGGESTED COMPONENTS:

X1 = ECLIPTEK EC38J (THROUGH-HOLE PACKAGE) OR

EPSON MC405 12 pF LOAD (SURFACE-MOUNT PACKAGE)

C1 = 22 pF

C2 = 22 pF

R1 = 10 M

NOTE: C1 AND C2 ARE SPECIFIC TO CRYSTAL SPECIFIED FOR X1.

CONTACT CRYSTAL MANUFACTURER FOR DETAILS. C1 AND C2

SPECIFICATIONS ASSUME BOARD TRACE CAPACITANCE OF 3 pF.

RTXI

R1

相关PDF资料 |

PDF描述 |

|---|---|

| MC78L18ACP | IC REG LDO 18V .1A TO92 |

| TPSC107M010R0150 | CAP TANT 100UF 10V 20% 2312 |

| MC78L15ACP | IC REG LDO 15V .1A TO92 |

| MC78L12ACP | IC REG LDO 12V .1A TO92 |

| MC78L12ABP | IC REG LDO 12V .1A TO92 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-BF537BBC-5AV | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| ADSP-BF537BBCZ-5A | 功能描述:数字信号处理器和控制器 - DSP, DSC Blackfin processor 500MHz 132KB SRAM RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| ADSP-BF537BBCZ-5A | 制造商:Analog Devices 功能描述:Digital Signal Processor IC |

| ADSP-BF537BBCZ-5AV | 功能描述:IC DSP CTLR 16BIT 182CSPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-BF537BBCZ-5AV | 制造商:Analog Devices 功能描述:Digital Signal Processor IC |

发布紧急采购,3分钟左右您将得到回复。