- 您现在的位置:买卖IC网 > PDF目录19388 > ADSP-BF542KBCZ-6A (Analog Devices Inc)IC DSP 16BIT 600MHZ 400CSBGA PDF资料下载

参数资料

| 型号: | ADSP-BF542KBCZ-6A |

| 厂商: | Analog Devices Inc |

| 文件页数: | 38/100页 |

| 文件大小: | 0K |

| 描述: | IC DSP 16BIT 600MHZ 400CSBGA |

| 标准包装: | 1 |

| 系列: | Blackfin® |

| 类型: | 定点 |

| 接口: | CAN,SPI,SSP,TWI,UART,USB |

| 时钟速率: | 600MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 132kB |

| 电压 - 输入/输出: | 2.50V,3.30V |

| 电压 - 核心: | 1.25V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 400-LFBGA,CSPBGA |

| 供应商设备封装: | 400-CSPBGA(17x17) |

| 包装: | 托盘 |

| 配用: | ADZS-BF548-EZLITE-ND - KIT EZLITE ADZS-BF548 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页当前第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页

Rev. C

|

Page 42 of 100

|

February 2010

ADSP-BF542/ADSP-BF544/ADSP-BF547/ADSP-BF548/ADSP-BF549

TIMING SPECIFICATIONS

Timing specifications are detailed in this section.

Clock and Reset Timing

Table 25. Clock Input and Reset Timing

Parameter

Min

Max

Unit

Timing Requirements

tCKIN

CLKIN Period1, 2, 3, 4

20.0

100.0

ns

tCKINL

CLKIN Low Pulse2

8.0

ns

tCKINH

CLKIN High Pulse2

8.0

ns

tBUFDLAY

CLKIN to CLKBUF Delay

10

ns

tWRST

RESET Asserted Pulsewidth Low

5

11 tCKIN

ns

tRHWFT

RESET High to First HWAIT/HWAITA Transition (Boot Host Wait Mode)

6,7,8,9

6100 tCKIN + 7900 tSCLK

ns

tRHWFT

RESET High to First HWAIT/HWAITA Transition (Reset Output Mode)7,10,11

6100 tCKIN

7000 tCKIN

ns

1 Combinations of the CLKIN frequency and the PLL clock multiplier must not exceed the allowed fVCO, fCCLK, and fSCLK settings discussed in Table 16 and Table 13 on Page 35.

2 Applies to PLL bypass mode and PLL non-bypass mode.

3 CLKIN frequency and duty cycle must not change on the fly.

4 If the DF bit in the PLL_CTL register is set, then the maximum tCKIN period is 50 ns.

5 Applies after power-up sequence is complete. See Table 27 and Figure 12 for more information about power-up reset timing.

6 Maximum value not specified due to variation resulting from boot mode selection and OTP memory programming.

7 Values specified assume no invalidation preboot settings in OTP page PBS00L. Invalidating a PBS set will increase the value by 1875 tCKIN (typically).

8 Applies only to boot modes BMODE=1, 2, 4, 6, 7, 10, 11, 14, 15.

9 Use default t

SCLK value unless PLL is reprogrammed during preboot. In case of PLL reprogramming use the new tSCLK value and add PLL_LOCKCNT settle time.

10When enabled by OTP_RESETOUT_HWAIT bit. If regular HWAIT is not required in an application, the OTP_RESETOUT_HWAIT bit in the same page instructs the

HWAIT or HWAITA to simulate reset output functionality. Then an external resistor is expected to pull the signal to the reset level, as the pin itself is in high performance

mode during reset.

11Variances are mainly dominated by PLL programming instructions in PBS00L page and boot code differences between silicon revisions. The earlier is bypassed in boot mode

BMODE = 0. Maximum value assumes PLL programming instructions do not cause the SCLK frequency to decrease.

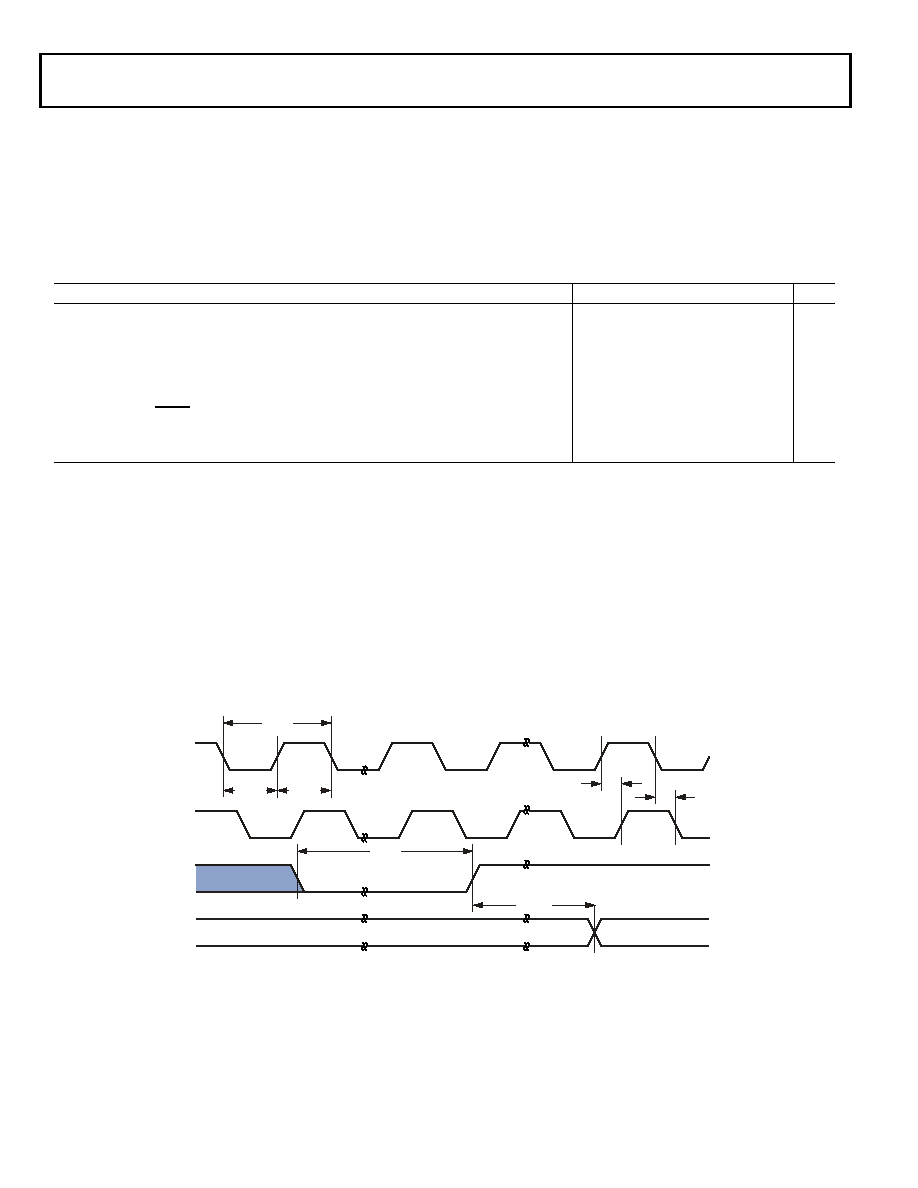

Figure 10. Clock and Reset Timing

CLKIN

tWRST

tCKIN

tCKINL

tCKINH

tBUFDLAY

RESET

CLKBUF

HWAIT (A)

tRHWFT

相关PDF资料 |

PDF描述 |

|---|---|

| TPSC686K016S0125 | CAP TANT 68UF 16V 10% 2312 |

| MC7805ACT | IC REG LDO 5V 1A TO220AB |

| VI-B1X-CV-F2 | CONVERTER MOD DC/DC 5.2V 150W |

| VE-B10-CV-F4 | CONVERTER MOD DC/DC 5V 150W |

| ADSP-BF533SBB500 | IC DSP CTLR 16BIT 500MHZ 169-BGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-BF542MBBCZ-5M | 功能描述:IC DSP 16BIT 533MHZ MDDR 400CBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-BF544BBCZ-4A | 功能描述:IC CCD SIGNAL PROCESSOR 400BGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-BF544BBCZ-5A | 功能描述:IC DSP 16BIT 533MHZ 400CSBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-BF544BBCZ-5X | 制造商:Analog Devices 功能描述:HIGH PERFORMANCE CONVERGENT MULTIMEDIA BLACKFIN PROCESSOR - Trays |

| ADSP-BF544MBBCZ-5M | 功能描述:IC DSP 16BIT 533MHZ MDDR 400CBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

发布紧急采购,3分钟左右您将得到回复。