- 您现在的位置:买卖IC网 > PDF目录19388 > ADSP-BF542KBCZ-6A (Analog Devices Inc)IC DSP 16BIT 600MHZ 400CSBGA PDF资料下载

参数资料

| 型号: | ADSP-BF542KBCZ-6A |

| 厂商: | Analog Devices Inc |

| 文件页数: | 79/100页 |

| 文件大小: | 0K |

| 描述: | IC DSP 16BIT 600MHZ 400CSBGA |

| 标准包装: | 1 |

| 系列: | Blackfin® |

| 类型: | 定点 |

| 接口: | CAN,SPI,SSP,TWI,UART,USB |

| 时钟速率: | 600MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 132kB |

| 电压 - 输入/输出: | 2.50V,3.30V |

| 电压 - 核心: | 1.25V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 400-LFBGA,CSPBGA |

| 供应商设备封装: | 400-CSPBGA(17x17) |

| 包装: | 托盘 |

| 配用: | ADZS-BF548-EZLITE-ND - KIT EZLITE ADZS-BF548 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页当前第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页

Rev. C

|

Page 8 of 100

|

February 2010

ADSP-BF542/ADSP-BF544/ADSP-BF547/ADSP-BF548/ADSP-BF549

higher-priority event takes precedence over servicing of a lower-

priority event. The controller provides support for five different

types of events:

Emulation. An emulation event causes the processor to

enter emulation mode, allowing command and control of

the processor via the JTAG interface.

Reset. This event resets the processor.

Non-maskable interrupt (NMI). The NMI event can be

generated by the software watchdog timer or by the NMI

input signal to the processor. The NMI event is frequently

used as a power-down indicator to initiate an orderly shut-

down of the system.

Exceptions. Events that occur synchronously to program

flow (that is, the exception is taken before the instruction is

allowed to complete). Conditions such as data alignment

violations and undefined instructions cause exceptions.

Interrupts. Events that occur asynchronously to program

flow. They are caused by input pins, timers, and other

peripherals, as well as by an explicit software instruction.

Each event type has an associated register to hold the return

address and an associated return-from-event instruction. When

an event is triggered, the state of the processor is saved on the

supervisor stack.

The ADSP-BF54x Blackfin processor event controller consists

of two stages, the core event controller (CEC) and the system

interrupt controller (SIC). The core event controller works with

the system interrupt controller to prioritize and control all sys-

tem events. Conceptually, interrupts from the peripherals enter

into the SIC and are then routed directly into the general-pur-

pose interrupts of the CEC.

Core Event Controller (CEC)

The CEC supports nine general-purpose interrupts (IVG15–7),

in addition to the dedicated interrupt and exception events. Of

these general-purpose interrupts, the two lowest-priority inter-

rupts (IVG15–14) are recommended to be reserved for software

interrupt handlers, leaving seven prioritized interrupt inputs to

support the peripherals of the ADSP-BF54x Blackfin processors.

Table 3 describes the inputs to the CEC, identifies their names

in the event vector table (EVT), and lists their priorities.

System Interrupt Controller (SIC)

The system interrupt controller provides the mapping and rout-

ing of events from the many peripheral interrupt sources to the

prioritized general-purpose interrupt inputs of the CEC.

Although the ADSP-BF54x Blackfin processors provide a

default mapping, the user can alter the mappings and priorities

of interrupt events by writing the appropriate values into the

interrupt assignment registers (SIC_IARx). Table 4 describes

the inputs into the SIC and the default mappings into the CEC.

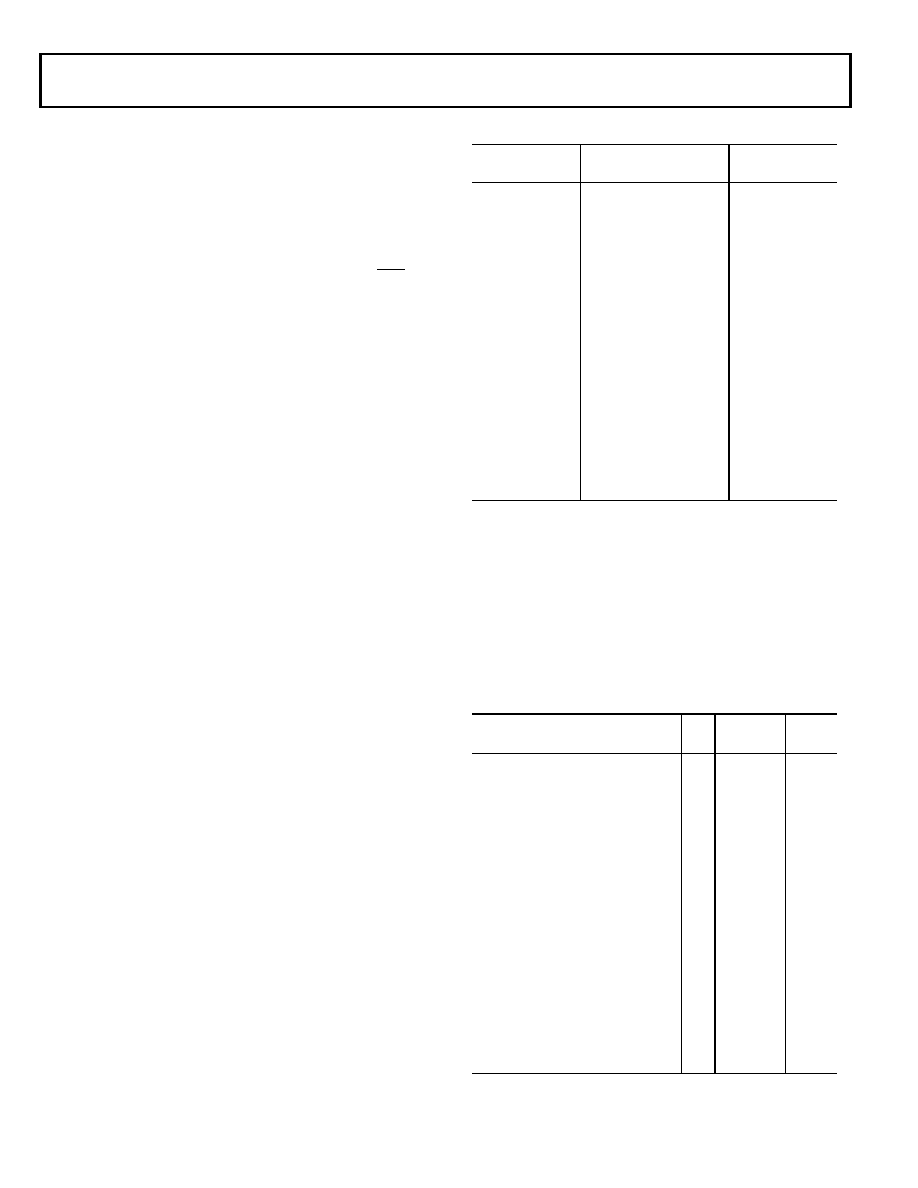

Table 3. Core Event Controller (CEC)

Priority

(0 is Highest)

Event Class

EVT Entry

0Emulation/Test Control

EMU

1

Reset

RST

2

Nonmaskable Interrupt

NMI

3Exception

EVX

4

Reserved

—

5

Hardware Error

IVHW

6

Core Timer

IVTMR

7

General Interrupt 7

IVG7

8

General Interrupt 8

IVG8

9

General Interrupt 9

IVG9

10

General Interrupt 10

IVG10

11

General Interrupt 11

IVG11

12

General Interrupt 12

IVG12

13

General Interrupt 13

IVG13

14

General Interrupt 14

IVG14

15

General Interrupt 15

IVG15

Table 4. System Interrupt Controller (SIC)

Peripheral IRQ

Source

IRQ

ID

GP IRQ

(at Reset)

Core

IRQ ID

PLL Wakeup IRQ

0

IVG7

0

DMAC0 Status (Generic)

1

IVG7

0

EPPI0 Error IRQ

2

IVG7

0

SPORT0 Error IRQ

3

IVG7

0

SPORT1 Error IRQ

4

IVG7

0

SPI0 Status IRQ

5

IVG7

0

UART0 Status IRQ

6

IVG7

0

Real-Time Clock IRQ

7

IVG8

1

DMA12 IRQ (EPPI0)

8

IVG8

1

DMA0 IRQ (SPORT0 RX)

9

IVG9

2

DMA1 IRQ (SPORT0 TX)

10

IVG9

2

DMA2 IRQ (SPORT1 RX)

11

IVG9

2

DMA3 IRQ (SPORT1 TX)

12

IVG9

2

DMA4 IRQ (SPI0)

13

IVG10

3

相关PDF资料 |

PDF描述 |

|---|---|

| TPSC686K016S0125 | CAP TANT 68UF 16V 10% 2312 |

| MC7805ACT | IC REG LDO 5V 1A TO220AB |

| VI-B1X-CV-F2 | CONVERTER MOD DC/DC 5.2V 150W |

| VE-B10-CV-F4 | CONVERTER MOD DC/DC 5V 150W |

| ADSP-BF533SBB500 | IC DSP CTLR 16BIT 500MHZ 169-BGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-BF542MBBCZ-5M | 功能描述:IC DSP 16BIT 533MHZ MDDR 400CBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-BF544BBCZ-4A | 功能描述:IC CCD SIGNAL PROCESSOR 400BGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-BF544BBCZ-5A | 功能描述:IC DSP 16BIT 533MHZ 400CSBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-BF544BBCZ-5X | 制造商:Analog Devices 功能描述:HIGH PERFORMANCE CONVERGENT MULTIMEDIA BLACKFIN PROCESSOR - Trays |

| ADSP-BF544MBBCZ-5M | 功能描述:IC DSP 16BIT 533MHZ MDDR 400CBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

发布紧急采购,3分钟左右您将得到回复。