- 您现在的位置:买卖IC网 > PDF目录223311 > ADSP-TS101SAB1-000 (ANALOG DEVICES INC) 300 MHz TigerSHARC Processor with 6 Mbit on-chip SRAM; Package: 625 ball BGA; No of Pins: 625; Temperature Range: Ind PDF资料下载

参数资料

| 型号: | ADSP-TS101SAB1-000 |

| 厂商: | ANALOG DEVICES INC |

| 元件分类: | 数字信号处理 |

| 英文描述: | 300 MHz TigerSHARC Processor with 6 Mbit on-chip SRAM; Package: 625 ball BGA; No of Pins: 625; Temperature Range: Ind |

| 中文描述: | 64-BIT, 125 MHz, OTHER DSP, PBGA625 |

| 封装: | 27 X 27 MM, PLASTIC, MS-034, BGA-625 |

| 文件页数: | 24/48页 |

| 文件大小: | 679K |

| 代理商: | ADSP-TS101SAB1-000 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

Rev. C

|

Page 30 of 48

|

May 2009

ADSP-TS101S

Table 30. Link Ports—Receive

Parameter

Min

Max

Unit

Timing Requirements

tLXCLK_RX

1, 2

Receive Link Clock Period

0.9 LR tCCLK

1.1 LR tCCLK

ns

tLXCLKH_RX

3

Receive Link Clock Width High

0.33 tLXCLK_RX

0.66 tLXCLK_RX

ns

tLXCLKH_RX

4

Receive Link Clock Width High

0.4 tLXCLK_RX

0.6 tLXCLK_RX

ns

tLXCLKL_RX

Receive Link Clock Width Low

0.33 tLXCLK_RX

0.66 tLXCLK_RX

ns

tLXCLKL_RX

Receive Link Clock Width Low

0.4 tLXCLK_RX

0.6 tLXCLK_RX

ns

tDIS

LxDAT7–0 Input Setup

0.6

ns

tDIH

LxDAT7–0 Input Hold

0.6

ns

Switching Characteristics

tCONNV

Connectivity Pulse Valid

0

2.5 tLXCLK_RX

ns

tCONNOW

Connectivity Pulse Output Width

1.5 tLXCLK_RX

ns

1 The link clock ratio (LR) is 2, 3, 4, or 8 as set by the SPD bits in the LCTLx register.

2 The maximum LxCLK is 125 MHz. LR = 2 may not be used when CCLK 250 MHz.

3 The formula for this parameter applies when LR is 2.

4 The formula for this parameter applies when LR is 3, 4, or 8.

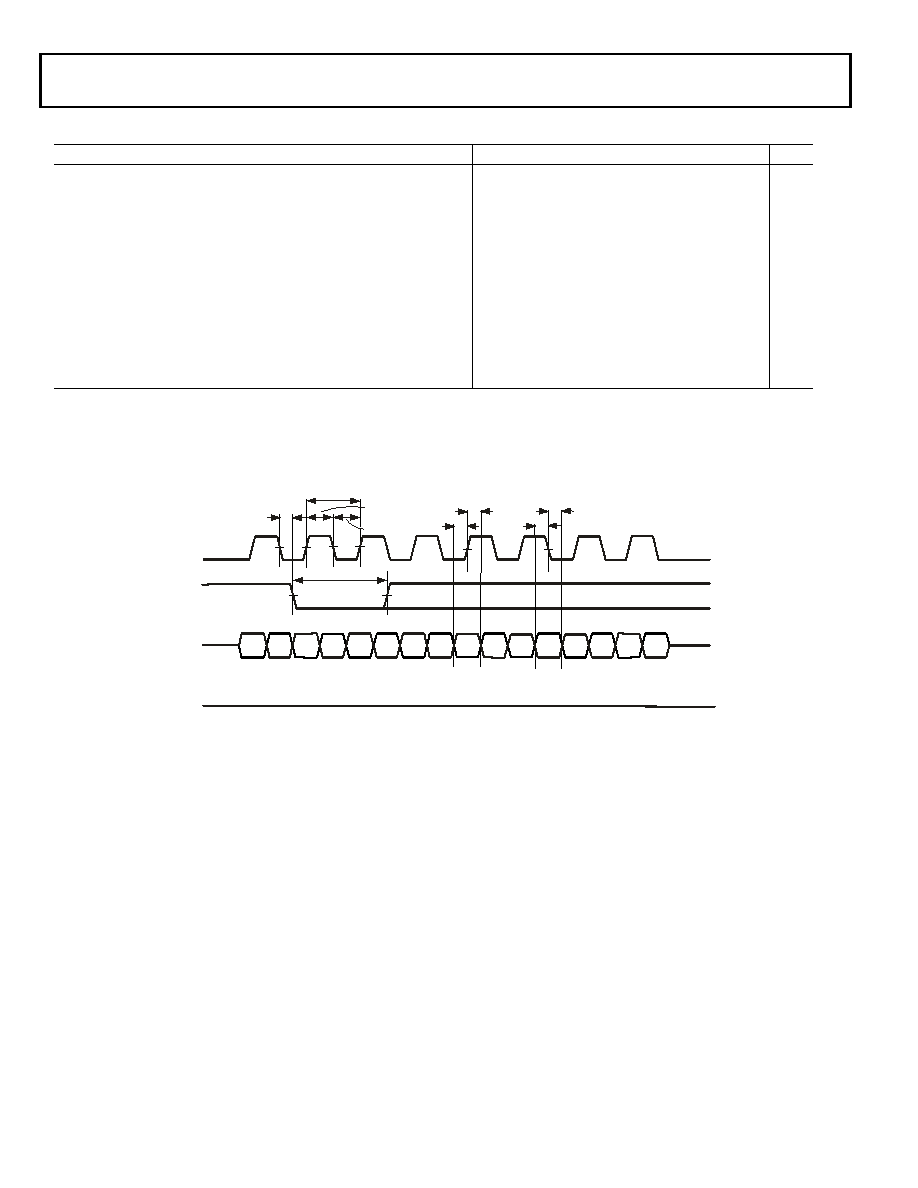

Figure 18. Link Ports—Receive

LxCLKIN

LxCLKOUT

LxDAT7–0

LxDIR

1

2

3

4

5

6

7

8

0

9

10

11

12

13

14

15

tLxCLK_Rx

tCONNV

tLxCLKH_Rx

tLxCLKL_Rx

tCONNOW

tDIS

tDIH

tDIS

tDIH

相关PDF资料 |

PDF描述 |

|---|---|

| ADSP-TS101SAB2-000 | 300 MHz TigerSHARC Processor with 6 Mbit on-chip SRAM; Package: 484 ball BGA; No of Pins: 484; Temperature Range: Ind |

| ADSP-TS203SABP-050 | 500 MHz TigerSHARC Processor with 4 Mbit on-chip embedded DRAM; Package: 576 ball SBGA; No of Pins: 576; Temperature Range: Ind |

| ADSP-TS203SABPZ050 | 500 MHz TigerSHARC Processor with 4 Mbit on-chip embedded DRAM; Package: 576 ball SBGA; No of Pins: 576; Temperature Range: Ind |

| ADSQ-1410-EX-C | 4-CH 14-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, DMA66 |

| ADT-2734-MM-35M-02 | MALE-MALE, RF STRAIGHT ADAPTER, PLUG |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-TS101SAB1-100 | 功能描述:IC DSP CTRLR 128BIT BUS 625BGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:TigerSHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-TS101SAB1Z000 | 功能描述:IC DSP CONTROLLER 6MBIT 625-BGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:TigerSHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-TS101SAB1Z100 | 功能描述:IC DSP CTRLR 128BIT BUS 625-BGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:TigerSHARC® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-TS101SAB2-000 | 功能描述:IC DSP CONTROLLER 6MBIT 484 BGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:TigerSHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-TS101SAB2-050 | 制造商:Analog Devices 功能描述:TIGERSHARC - Trays |

发布紧急采购,3分钟左右您将得到回复。