- 您现在的位置:买卖IC网 > PDF目录19369 > ADSP-TS201SABP-060 (Analog Devices Inc)IC PROCESSOR 600MHZ 576BGA PDF资料下载

参数资料

| 型号: | ADSP-TS201SABP-060 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 23/48页 |

| 文件大小: | 0K |

| 描述: | IC PROCESSOR 600MHZ 576BGA |

| 标准包装: | 1 |

| 系列: | TigerSHARC® |

| 类型: | 定点/浮点 |

| 接口: | 主机接口,连接端口,多处理器 |

| 时钟速率: | 600MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 3MB |

| 电压 - 输入/输出: | 2.50V |

| 电压 - 核心: | 1.20V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 576-BBGA 裸露焊盘 |

| 供应商设备封装: | 576-BGA-ED(25x25) |

| 包装: | 托盘 |

| 配用: | ADZS-TS201S-EZLITE-ND - KIT LITE EVAL FOR ADSP-TS201S |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页当前第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

ADSP-TS201S

Rev. C

|

Page 3 of 48

|

December 2006

GENERAL DESCRIPTION

The ADSP-TS201S TigerSHARC processor is an ultrahigh per-

formance, static superscalar processor optimized for large signal

processing tasks and communications infrastructure. The DSP

combines very wide memory widths with dual computation

blocks—supporting floating-point (IEEE 32-bit and extended

precision 40-bit) and fixed-point (8-, 16-, 32-, and 64-bit) pro-

cessing—to set a new standard of performance for digital signal

processors. The TigerSHARC static superscalar architecture lets

the DSP execute up to four instructions each cycle, performing

24 fixed-point (16-bit) operations or six floating-point

operations.

Four independent 128-bit wide internal data buses, each con-

necting to the six 4M bit memory banks, enable quad-word

data, instruction, and I/O access and provide 33.6G bytes per

second of internal memory bandwidth. Operating at 600 MHz,

the ADSP-TS201S processor’s core has a 1.67 ns instruction

cycle time. Using its single-instruction, multiple-data (SIMD)

features, the ADSP-TS201S processor can perform 4.8 billion,

40-bit MACS or 1.2 billion, 80-bit MACS per second. Table 1

shows the DSP’s performance benchmarks.

The ADSP-TS201S processor is code compatible with the other

TigerSHARC processors.

The Functional Block Diagram on Page 1 shows the

ADSP-TS201S processor’s architectural blocks. These blocks

include:

Dual compute blocks, each consisting of an ALU, multi-

plier, 64-bit shifter, 128-bit CLU, and 32-word register file

and associated data alignment buffers (DABs)

Dual integer ALUs (IALUs), each with its own 31-word

register file for data addressing and a status register

A program sequencer with instruction alignment buffer

(IAB) and branch target buffer (BTB)

An interrupt controller that supports hardware and soft-

ware interrupts, supports level- or edge-triggers, and

supports prioritized, nested interrupts

Four 128-bit internal data buses, each connecting to the six

4M bit memory banks

On-chip DRAM (24M bit)

An external port that provides the interface to host proces-

sors, multiprocessing space (DSPs), off-chip memory-

mapped peripherals, and external SRAM and SDRAM

A 14-channel DMA controller

Four full-duplex LVDS link ports

Two 64-bit interval timers and timer expired pin

An 1149.1 IEEE-compliant JTAG test access port for on-

chip emulation

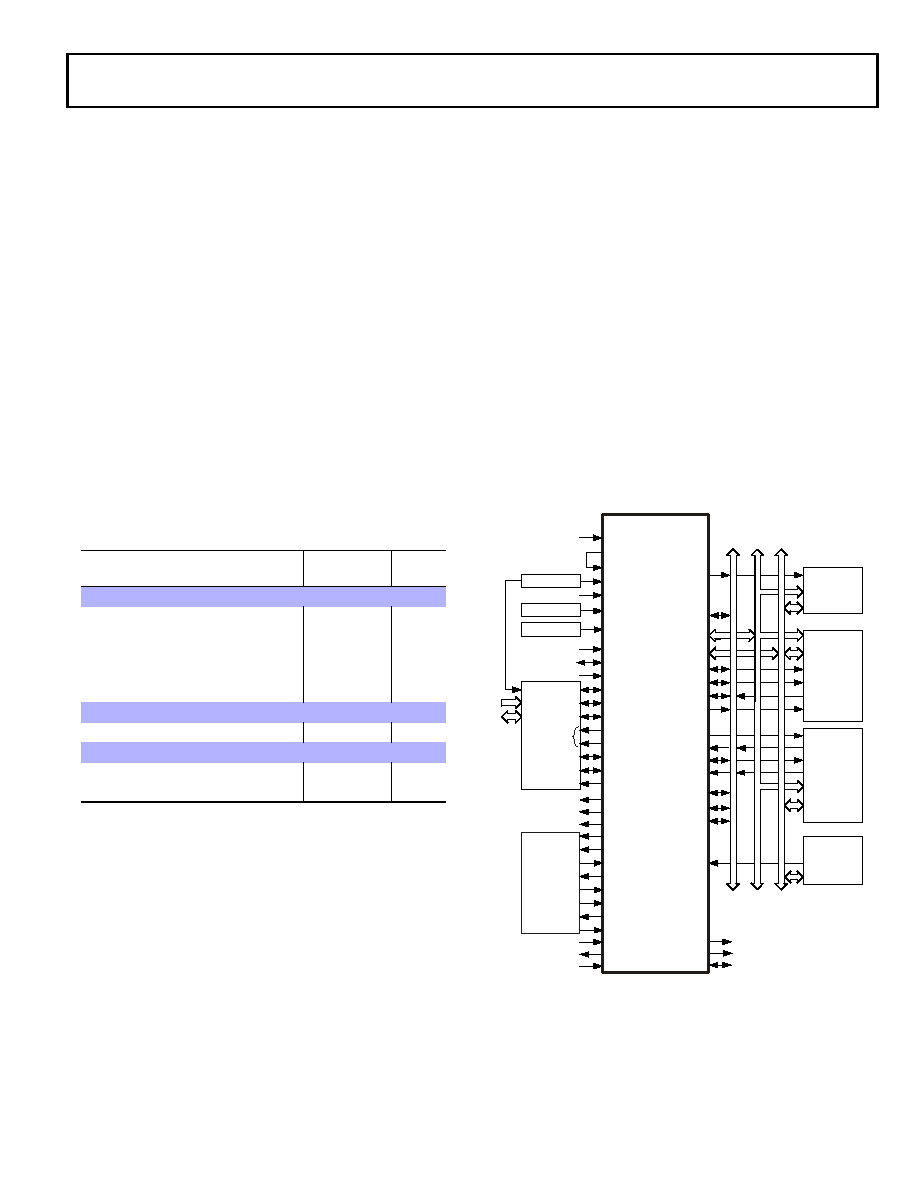

Figure 2 on Page 3 shows a typical single-processor system with

external SRAM and SDRAM. Figure 4 on Page 8 shows a typical

multiprocessor system.

Table 1. General-Purpose Algorithm Benchmarks

at 600 MHz

Benchmark

Speed

Clock

Cycles

32-bit algorithm, 1.2 billion MACS/s peak performance

1K point complex FFT

1 (Radix2)

15.7 μs

9419

64K point complex FFT

1 (Radix2)

2.33 ms

1397544

FIR filter (per real tap)

0.83 ns

0.5

[8 × 8][8 × 8] matrix multiply (complex,

floating-point)

2.3 μs

1399

16-bit algorithm, 4.8 billion MACS/s peak performance

256 point complex FFT1 (Radix 2)

1 Cache preloaded

0.975 μs

585

I/O DMA transfer rate

External port

1G bytes/s

n/a

Link ports (each)

1G bytes/s

n/a

Figure 2. ADSP-TS201S Single-Processor System with External SDRAM

BOFF

CONTROLIMP1–0

DMAR3–0

HBG

HBR

DMA DEVICE

(OPTIONAL)

DATA

MSH

FLAG3–0

ID2–0

IOEN

RAS

CAS

LDQM

HDQM

SDWE

SDCKE

SDA10

IRQ3–0

SCLK

SCLKRAT2–0

SCLK_VREF

VREF

TMR0E

BM

MSSD3–0

BUSLOCK

SDRAM

MEMORY

(OPTIONAL)

CS

RAS

CAS

DQM

WE

CKE

A10

ADDR

DATA

CLK

POR_IN

JTAG

ADSP-TS201S

BMS

CLOCK

LINK

DEVICES

(4 MAX)

(OPTIONAL)

BOOT

EPROM

(OPTIONAL)

ADDR

MEMORY

(OPTIONAL)

OE

DATA

ADDR

DATA

HOST

PROCESSOR

INTERFACE

(OPTIONAL)

ACK

BR7–0

CPA

MS1–0

DATA63–0

DATA

ADDR

CS

ACK

WE

ADDR31–0

D

A

T

A

C

O

N

T

R

O

L

A

D

R

E

S

BRST

REFERENCE

RD

WRH/WRL

DPA

DS2–0

CS

LxCLKINP/N

LxACKO

LxDATI3–0P/N

LxBCMPI

LxBCMPO

LxDATO3–0P/N

LxCLKOUTP/N

LxACKI

IORD

IOWR

RST_OUT

RST_IN

REFERENCE

相关PDF资料 |

PDF描述 |

|---|---|

| VE-B3H-CY-S | CONVERTER MOD DC/DC 52V 50W |

| ADSP-21060KSZ-133 | IC DSP CONTROLLER 32BIT 240-MQFP |

| EBC25DRTS | CONN EDGECARD 50POS DIP .100 SLD |

| VE-B3D-CY-S | CONVERTER MOD DC/DC 85V 50W |

| TPSD686K020R0200 | CAP TANT 68UF 20V 10% 2917 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-TS201SABP-10X | 制造商:Analog Devices 功能描述: |

| ADSP-TS201SABP-15X | 制造商:Analog Devices 功能描述: |

| ADSP-TS201SABP-ENG | 制造商:Analog Devices 功能描述: |

| ADSP-TS201SABP-ENG1 | 制造商:Analog Devices 功能描述: |

| ADSP-TS201SABPZ050 | 功能描述:IC PROCESSOR 500MHZ 576BGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:TigerSHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

发布紧急采购,3分钟左右您将得到回复。