- 您现在的位置:买卖IC网 > PDF目录19369 > ADSP-TS201SABP-060 (Analog Devices Inc)IC PROCESSOR 600MHZ 576BGA PDF资料下载

参数资料

| 型号: | ADSP-TS201SABP-060 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 8/48页 |

| 文件大小: | 0K |

| 描述: | IC PROCESSOR 600MHZ 576BGA |

| 标准包装: | 1 |

| 系列: | TigerSHARC® |

| 类型: | 定点/浮点 |

| 接口: | 主机接口,连接端口,多处理器 |

| 时钟速率: | 600MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 3MB |

| 电压 - 输入/输出: | 2.50V |

| 电压 - 核心: | 1.20V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 576-BBGA 裸露焊盘 |

| 供应商设备封装: | 576-BGA-ED(25x25) |

| 包装: | 托盘 |

| 配用: | ADZS-TS201S-EZLITE-ND - KIT LITE EVAL FOR ADSP-TS201S |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

Rev. C

|

Page 16 of 48

|

December 2006

ADSP-TS201S

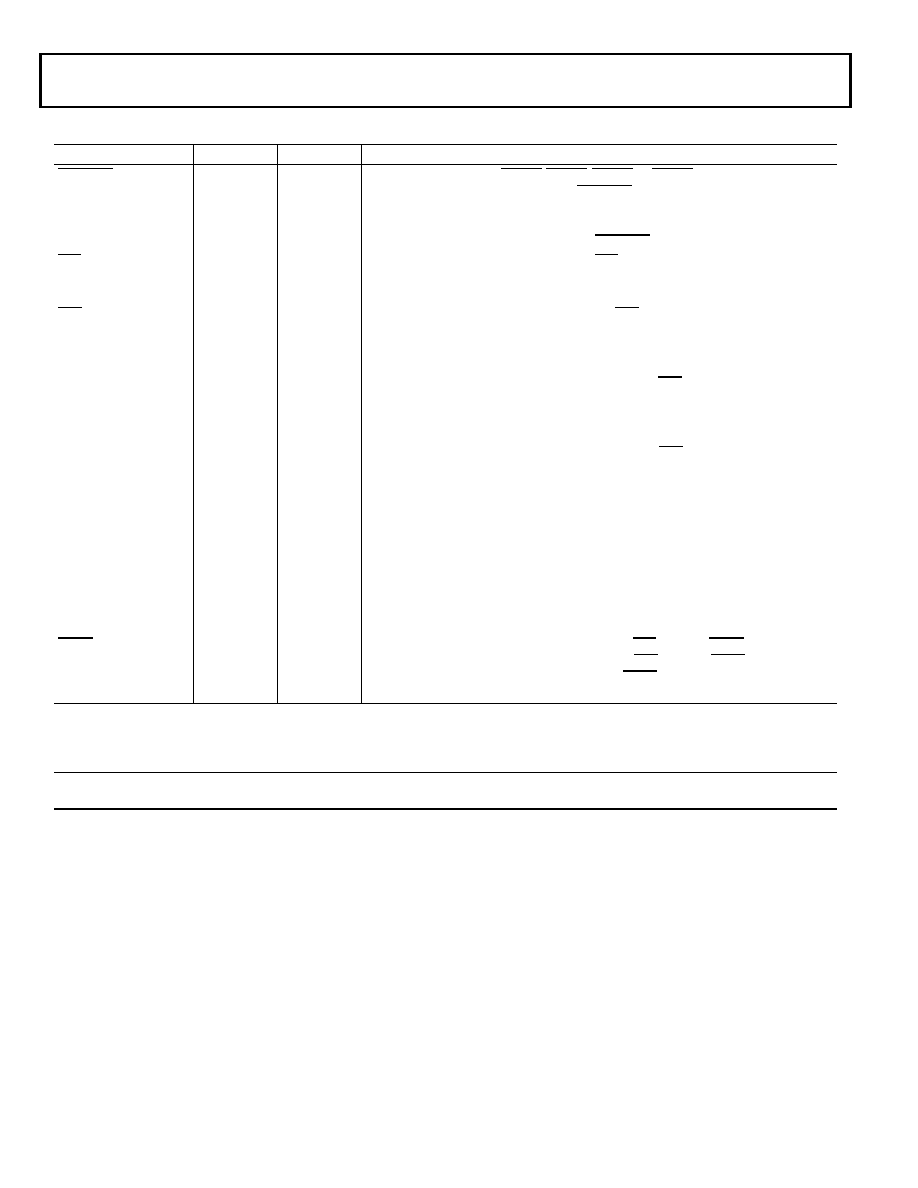

Table 8. Pin Definitions—External Port SDRAM Controller

Signal

Type

Term

Description

MSSD3–0

I/O/T

(pu_0)

nc

Memory Select SDRAM. MSSD0, MSSD1, MSSD2, or MSSD3 is asserted whenever the

DSP accesses SDRAM memory space. MSSD3–0 are decoded memory address pins

that are asserted whenever the DSP issues an SDRAM command cycle (access to

ADDR31:30 = 0b01—except reserved spaces shown in Figure 3 on Page 6). In a multi-

processor system, the master DSP drives MSSD3–0.

RAS

I/O/T

(pu_0)

nc

Row Address Select. When sampled low, RAS indicates that a row address is valid in

a read or write of SDRAM. In other SDRAM accesses, it defines the type of operation

to execute according to SDRAM specification.

CAS

I/O/T

(pu_0)

nc

Column Address Select. When sampled low, CAS indicates that a column address is

valid in a read or write of SDRAM. In other SDRAM accesses, it defines the type of

operation to execute according to the SDRAM specification.

LDQM

O/T

(pu_0)

nc

Low Word SDRAM Data Mask. When sampled high, three-states the SDRAM DQ

buffers. LDQM is valid on SDRAM transactions when CAS is asserted, and inactive on

read transactions. On write transactions, LDQM is active when accessing an odd

address word on a 64-bit memory bus to disable the write of the low word.

HDQM

O/T

(pu_0)

nc

High Word SDRAM Data Mask. When sampled high, three-states the SDRAM DQ

buffers. HDQM is valid on SDRAM transactions when CAS is asserted, and inactive on

read transactions. On write transactions, HDQM is active when accessing an even

address in word accesses or when memory is configured for a 32-bit bus to disable

the write of the high word.

SDA10

O/T

(pu_0)

nc

SDRAM Address Bit 10. Separate A10 signals enable SDRAM refresh operation while

the DSP executes non-SDRAM transactions.

SDCKE

I/O/T

(pu_m/

pd_m)

nc

SDRAM Clock Enable. Activates the SDRAM clock for SDRAM self-refresh or suspend

modes. A slave DSP in a multiprocessor system does not have the pull-up or pull-

down. A master DSP (or ID = 0 in a single processor system) has a pull-up before

granting the bus to the host, except when the SDRAM is put in self refresh mode. In

self refresh mode, the master has a pull-down before granting the bus to the host.

SDWE

I/O/T

(pu_0)

nc

SDRAM Write Enable. When sampled low while CAS is active, SDWE indicates an

SDRAM write access. When sampled high while CAS is active, SDWE indicates an

SDRAM read access. In other SDRAM accesses, SDWE defines the type of operation to

execute according to SDRAM specification.

I = input; A = asynchronous; O = output; OD = open-drain output; T = three-state; P = power supply; G = ground; pd = internal pull-down

5k

Ω; pu = internal pull-up 5 kΩ; pd_0 = internal pull-down 5 kΩ on DSP ID = 0; pu_0 = internal pull-up 5 kΩ on DSP ID = 0; pu_od_0 = internal

pull-up 500

Ω on DSP ID = 0; pd_m = internal pull-down 5 kΩ on DSP bus master; pu_m = internal pull-up 5 kΩ on DSP bus master; pu_ad

= internal pull-up 40 k

Ω. For more pull-down and pull-up information, see Electrical Characteristics on Page 22.

Term (termination of unused pins) column symbols: epd = external pull-down approximately 5 k

Ω to VSS; epu = external pull-up approx-

imately 5 k

Ω to VDD_IO, nc = not connected; na = not applicable (always used); VDD_IO = connect directly to VDD_IO; VSS = connect directly to VSS

相关PDF资料 |

PDF描述 |

|---|---|

| VE-B3H-CY-S | CONVERTER MOD DC/DC 52V 50W |

| ADSP-21060KSZ-133 | IC DSP CONTROLLER 32BIT 240-MQFP |

| EBC25DRTS | CONN EDGECARD 50POS DIP .100 SLD |

| VE-B3D-CY-S | CONVERTER MOD DC/DC 85V 50W |

| TPSD686K020R0200 | CAP TANT 68UF 20V 10% 2917 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-TS201SABP-10X | 制造商:Analog Devices 功能描述: |

| ADSP-TS201SABP-15X | 制造商:Analog Devices 功能描述: |

| ADSP-TS201SABP-ENG | 制造商:Analog Devices 功能描述: |

| ADSP-TS201SABP-ENG1 | 制造商:Analog Devices 功能描述: |

| ADSP-TS201SABPZ050 | 功能描述:IC PROCESSOR 500MHZ 576BGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:TigerSHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

发布紧急采购,3分钟左右您将得到回复。