- 您现在的位置:买卖IC网 > PDF目录19369 > ADSP-TS201SABP-060 (Analog Devices Inc)IC PROCESSOR 600MHZ 576BGA PDF资料下载

参数资料

| 型号: | ADSP-TS201SABP-060 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 45/48页 |

| 文件大小: | 0K |

| 描述: | IC PROCESSOR 600MHZ 576BGA |

| 标准包装: | 1 |

| 系列: | TigerSHARC® |

| 类型: | 定点/浮点 |

| 接口: | 主机接口,连接端口,多处理器 |

| 时钟速率: | 600MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 3MB |

| 电压 - 输入/输出: | 2.50V |

| 电压 - 核心: | 1.20V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 576-BBGA 裸露焊盘 |

| 供应商设备封装: | 576-BGA-ED(25x25) |

| 包装: | 托盘 |

| 配用: | ADZS-TS201S-EZLITE-ND - KIT LITE EVAL FOR ADSP-TS201S |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页当前第45页第46页第47页第48页

Rev. C

|

Page 6 of 48

|

December 2006

ADSP-TS201S

33.6G bytes per second, enabling the core and I/O to access

eight 32-bit data-words and four 32-bit instructions each cycle.

The DSP’s flexible memory structure enables:

DSP core and I/O accesses to different memory blocks in

the same cycle

DSP core access to three memory blocks in parallel—one

instruction and two data accesses

Programmable partitioning of program and data memory

Program access of all memory as 32-, 64-, or 128-bit

words—16-bit words with the DAB

EXTERNAL PORT

(OFF-CHIP MEMORY/PERIPHERALS INTERFACE)

The ADSP-TS201S processor’s external port provides the DSP’s

interface to off-chip memory and peripherals. The 4G word

address space is included in the DSP’s unified address space.

The separate on-chip buses—four 128-bit data buses and four

32-bit address buses—are multiplexed at the SOC interface and

transferred to the external port over the SOC bus to create an

external system bus transaction. The external system bus pro-

vides a single 64-bit data bus and a single 32-bit address bus.

The external port supports data transfer rates of 1G byte per

second over the external bus.

The external bus can be configured for 32-bit or 64-bit, little-

endian operations. When the system bus is configured for 64-bit

operations, the lower 32 bits of the external data bus connect to

even addresses, and the upper 32 bits connect to odd addresses.

The external port supports pipelined, slow, and SDRAM proto-

cols. Addressing of external memory devices and memory-

mapped peripherals is facilitated by on-chip decoding of high

order address lines to generate memory bank select signals.

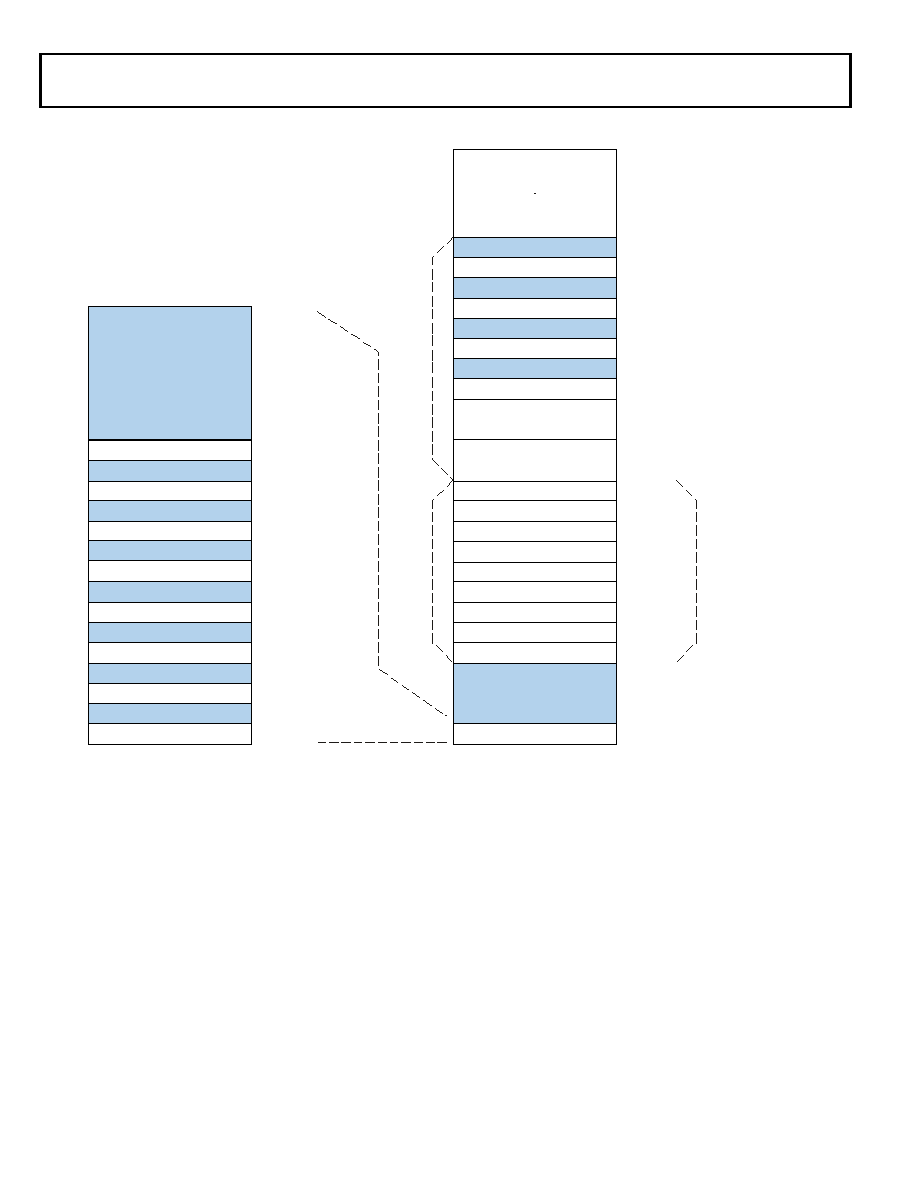

Figure 3. ADSP-TS201S Memory Map

RESERVED

RE SERVED

INTERNAL REG ISTERS (UREG S)

INTERNAL MEMORY BLO CK 4

INTERNAL MEMORY BLOCK 2

INTERNAL MEMORY BLOCK 0

0x03FFFFFF

0x001E0000

0x001E03FF

0x000DFFFF

0x000C0000

0x0009FFFF

0x00080000

0x0005FFFF

0x00040000

0x0001FFFF

0x00000000

INTERNAL SPACE

PROCESSOR ID 7

PROCESSOR ID 6

PROCESSOR ID 5

PROCESSOR ID 4

PROCESSOR ID 3

PROCESSOR ID 2

PROCESSOR ID 1

PROCESSOR ID 0

BROADCAST

HOST (

MSH)

BANK 1 (

MS1)

BANK 0 (

MS0)

MSSD BANK 0 (

MSSD0)

INTERNAL MEMORY

0x50000000

0x40000000

0x38000000

0x30000000

0x2C000000

0x28000000

0x24000000

0x20000000

0x1C000000

0x18000000

0x14000000

0x10000000

0x0C000000

0x03FFFFFF

0x00000000

GLOBAL SPACE

0xFFFFFFFF

M

U

L

T

IP

R

O

C

E

S

O

R

M

E

M

O

R

Y

S

P

A

C

E

X

T

E

R

N

A

L

M

E

M

O

R

Y

S

P

A

C

E

EACH IS A COPY

OF INTERNAL SPACE

RESERVED

INTERNAL MEMORY BLO CK 6

INTERNAL MEMO RY BLOCK 8

0x0011FFFF

0x00100000

INTERNAL MEMO RY BLOCK 10

0x0015FFFF

0x00140000

RESERVED

SO C REGISTE RS (UREGS)

0x001F0000

0x001F03FF

MSSD BANK 1 (

MSSD1)

MSSD BANK 2 (

MSSD2)

MSSD BANK 3 (

MSSD3)

0x60000000

0x70000000

0x80000000

RESERV ED

0x54000000

0x44000000

0x64000000

0x74000000

相关PDF资料 |

PDF描述 |

|---|---|

| VE-B3H-CY-S | CONVERTER MOD DC/DC 52V 50W |

| ADSP-21060KSZ-133 | IC DSP CONTROLLER 32BIT 240-MQFP |

| EBC25DRTS | CONN EDGECARD 50POS DIP .100 SLD |

| VE-B3D-CY-S | CONVERTER MOD DC/DC 85V 50W |

| TPSD686K020R0200 | CAP TANT 68UF 20V 10% 2917 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-TS201SABP-10X | 制造商:Analog Devices 功能描述: |

| ADSP-TS201SABP-15X | 制造商:Analog Devices 功能描述: |

| ADSP-TS201SABP-ENG | 制造商:Analog Devices 功能描述: |

| ADSP-TS201SABP-ENG1 | 制造商:Analog Devices 功能描述: |

| ADSP-TS201SABPZ050 | 功能描述:IC PROCESSOR 500MHZ 576BGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:TigerSHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

发布紧急采购,3分钟左右您将得到回复。