- 您现在的位置:买卖IC网 > PDF目录12014 > ADUC836BSZ (Analog Devices Inc)IC ADC DUAL 16BIT W/MCU 52-MQFP PDF资料下载

参数资料

| 型号: | ADUC836BSZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 40/80页 |

| 文件大小: | 0K |

| 描述: | IC ADC DUAL 16BIT W/MCU 52-MQFP |

| 产品培训模块: | Process Control |

| 标准包装: | 1 |

| 系列: | MicroConverter® ADuC8xx |

| 核心处理器: | 8052 |

| 芯体尺寸: | 8-位 |

| 速度: | 12.58MHz |

| 连通性: | EBI/EMI,I²C,SPI,UART/USART |

| 外围设备: | POR,PSM,PWM,温度传感器,WDT |

| 输入/输出数: | 34 |

| 程序存储器容量: | 62KB(62K x 8) |

| 程序存储器类型: | 闪存 |

| EEPROM 大小: | 4K x 8 |

| RAM 容量: | 2.25K x 8 |

| 电压 - 电源 (Vcc/Vdd): | 2.7 V ~ 5.25 V |

| 数据转换器: | A/D 7x16b; D/A 1x12b |

| 振荡器型: | 内部 |

| 工作温度: | -40°C ~ 125°C |

| 封装/外壳: | 52-QFP |

| 包装: | 托盘 |

| 产品目录页面: | 738 (CN2011-ZH PDF) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页当前第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页

ADuC836

–44–

ADuC836

–45–

SPIDAT

SPI Data Register

Function

The SPIDAT SFR is written by the user to transmit data over the SPI interface or read by user code to read

data just received by the SPI interface.

SFR Address

F7H

Power-On Default Value

00H

Bit Addressable

No

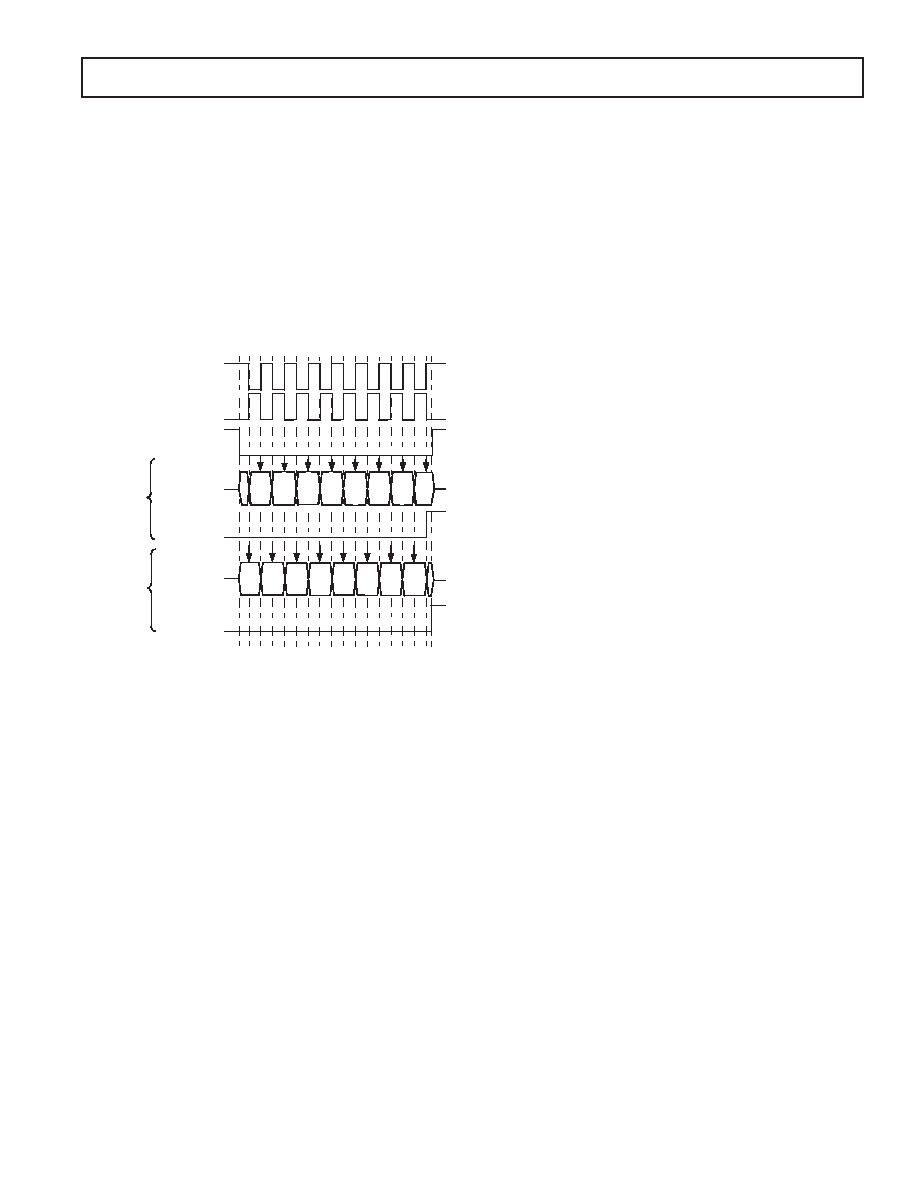

Depending on the configuration of the bits in the SPICON SFR

shown in Table XXI, the ADuC836 SPI interface will transmit

or receive data in a number of possible modes. Figure 34 shows

all possible ADuC836 SPI configurations and the timing rela-

tionships and synchronization between the signals involved. Also

shown in this figure is the SPI Interrupt bit (ISPI) and how it is

triggered at the end of each byte-wide communication.

SCLOCK

(CPOL = 1)

SCLOCK

(CPOL = 0)

(CPHA = 1)

(CPHA = 0)

SAMPLE INPUT

ISPI FLAG

DATA OUTPUT

ISPI FLAG

SAMPLE INPUT

DATA OUTPUT

?

MSB BIT 6 BIT 5

?

BIT 4 BIT 3 BIT 2 BIT 1 LSB

MSB BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 LSB

SS

Figure 34. SPITiming, All Modes

SPI Interface—Master Mode

In Master mode, the SCLOCK pin is always an output and gen-

erates a burst of eight clocks whenever user code writes to the

SPIDAT Register.The SCLOCK bit rate is determined by SPR0

and SPR1 in SPICON. It should also be noted that the SS pin

is not used in Master mode. If the ADuC836 needs to assert

the SS pin on an external slave device, a port digital output pin

should be used.

In Master mode, a byte transmission or reception is initiated

by a write to SPIDAT. Eight clock periods are generated via

the SCLOCK pin and the SPIDAT byte being transmitted via

MOSI.With each SCLOCK period, a data bit is also sampled

via MISO. After eight clocks, the transmitted byte will have been

completely transmitted and the input byte will be waiting in the

input shift register.The ISPI flag will be set automatically and an

interrupt will occur if enabled.The value in the shift register will

be latched into SPIDAT.

SPI Interface—Slave Mode

In Slave mode, the SCLOCK is an input.The SS pin must also

be driven low externally during the byte communication.Trans-

mission is also initiated by a write to SPIDAT. In Slave mode,

a data bit is transmitted via MISO and a data bit is received via

MOSI through each input SCLOCK period. After eight clocks,

the transmitted byte will have been completely transmitted and

the input byte will be waiting in the input shift register.The ISPI

flag will be set automatically and an interrupt will occur if enabled.

The value in the shift register will be latched into SPIDAT only

when the transmission/reception of a byte has been completed.

The end of transmission occurs after the eighth clock has been

received, if CPHA = 1 or when SS returns high if CPHA = 0.

REV. A

相关PDF资料 |

PDF描述 |

|---|---|

| ADUC841BSZ62-5 | IC ADC/DAC 12BIT W/MCU 52-MQFP |

| VJ1825Y103JBGAT4X | CAP CER 10000PF 1KV 5% X7R 1825 |

| SCRU-01 | CONN RCPT IP68 USB A PNL MNT |

| VJ1825Y153JBGAT4X | CAP CER 0.015UF 1KV 5% X7R 1825 |

| VJ1825Y223JBGAT4X | CAP CER 0.022UF 1KV 5% X7R 1825 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADUC841 | 制造商:AD 制造商全称:Analog Devices 功能描述:MicroConverter 12-Bit ADCs and DACs with Embedded High Speed 62-kB Flash MCU |

| ADUC841BCP32-5 | 制造商:Analog Devices 功能描述:MICROCONVERTER 1-CYCLE VERSION ADUC829 - Trays |

| ADUC841BCP62-3 | 制造商:Analog Devices 功能描述:MCU 8-Bit ADuC8xx 8052 CISC 62KB Flash 3V 56-Pin LFCSP EP 制造商:Rochester Electronics LLC 功能描述:8BIT CISC 62KB FLASH 20MHZ 3.3V 56LFCSP - Bulk |

| ADUC841BCP62-5 | 制造商:Analog Devices 功能描述:MCU 8-Bit ADuC8xx 8052 CISC 62KB Flash 5V 56-Pin LFCSP EP |

| ADUC841BCP8-3 | 制造商:Analog Devices 功能描述:MCU 8-bit ADuC8xx 8052 CISC 62KB Flash 3V 56-Pin LFCSP EP 制造商:Rochester Electronics LLC 功能描述:8BIT CISC 62KB FLASH 20MHZ 3.3V 56LFCSP - Bulk |

发布紧急采购,3分钟左右您将得到回复。