参数资料

| 型号: | ADV7180WBCPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 5/116页 |

| 文件大小: | 0K |

| 描述: | IC VIDEO DECODER SDTV 40LFCSP |

| 标准包装: | 1 |

| 类型: | 视频解码器 |

| 应用: | 数码相机,手机,便携式视频 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 40-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 40-LFCSP-VQ(6x6) |

| 包装: | 托盘 |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页

ADV7180

Data Sheet

Rev. I | Page 102 of 116

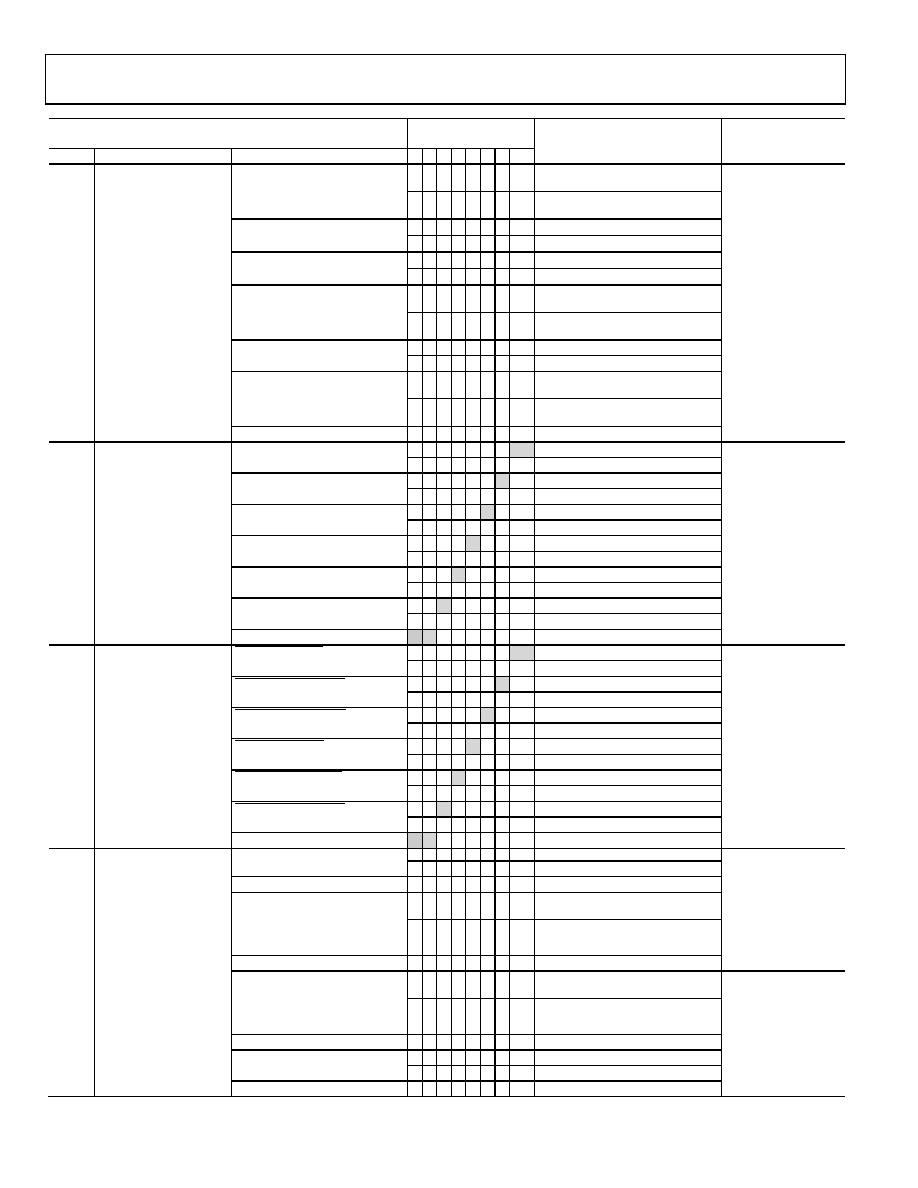

Interrupt and VDP Map

Bit

(Shading Indicates

Default State)

Address Register

Bit Description

7 6 5 4 3 2 1 0

Comments

Notes

0x4A

Interrupt Status 3

(read only)

SD_OP_CHNG_Q; SD 60 Hz/50 Hz

frame rate at output

0

No change in SD signal standard

detected at the output

These bits can be cleared

and masked by

Register 0x4B and

Register 0x4C, respectively

1

A change in SD signal standard is

detected at the output

SD_V_LOCK_CHNG_Q

0

No change in SD

VSYNC lock status

1

SD

VSYNC lock status has changed

SD_H_LOCK_CHNG_Q

0

No change in

HSYNC lock status

1

SD

HSYNC lock status has changed

SD_AD_CHNG_Q; SD autodetect

changed

0

No change in AD_RESULT[2:0] bits in

Status 1 register

1

AD_RESULT[2:0] bits in Status 1 register

have changed

SCM_LOCK_CHNG_Q; SECAM lock

0

No change in SECAM lock status

1

SECAM lock status has changed

PAL_SW_LK_CHNG_Q

0

No change in PAL swinging burst

lock status

1

PAL swinging burst lock status has

changed

Reserved

x x

Not used

0x4B

Interrupt Clear 3

(write only)

SD_OP_CHNG_CLR

0

Do not clear

1

Clears SD_OP_CHNG_Q bit

SD_V_LOCK_CHNG_CLR

0

Do not clear

1

Clears SD_V_LOCK_CHNG_Q bit

SD_H_LOCK_CHNG_CLR

0

Do not clear

1

Clears SD_H_LOCK_CHNG_Q bit

SD_AD_CHNG_CLR

0

Do not clear

1

Clears SD_AD_CHNG_Q bit

SCM_LOCK_CHNG_CLR

0

Do not clear

1

Clears SCM_LOCK_CHNG_Q bit

PAL_SW_LK_CHNG_CLR

0

Do not clear

1

Clears PAL_SW_LK_CHNG_Q bit

Reserved

x x

Not used

0x4C

Interrupt Mask 3

(read/write)

SD_OP_CHNG_MSK

0

Masks SD_OP_CHNG_Q bit

1

Unmasks SD_OP_CHNG_Q bit

SD_V_LOCK_CHNG_MSK

0

Masks SD_V_LOCK_CHNG_Q bit

1

Unmasks SD_V_LOCK_CHNG_Q bit

SD_H_LOCK_CHNG_MSK

0

Masks SD_H_LOCK_CHNG_Q bit

1

Unmasks SD_H_LOCK_CHNG_Q bit

SD_AD_CHNG_MSK

0

Masks SD_AD_CHNG_Q bit

1

Unmasks SD_AD_CHNG_Q bit

SCM_LOCK_CHNG_MSK

0

Masks SCM_LOCK_CHNG_Q bit

1

Unmasks SCM_LOCK_CHNG_Q bit

PAL_SW_LK_CHNG_MSK

0

Masks PAL_SW_LK_CHNG_Q bit

1

Unmasks PAL_SW_LK_CHNG_Q bit

Reserved

x x

Not used

0x4E

Interrupt Status 4 (read only) VDP_CCAPD_Q

0

Closed captioning not detected

These bits can be cleared

and masked by Register

0x4F and Register 0x50,

respectively; note that an

interrupt in Register 0x4E

for the CCAP, Gemstar,

CGMS, WSS, VPS, PDC,

UTC, and VITC data uses

the VDP data slicer

1

Closed captioning detected

Reserved

x

VDP_CGMS_WSS_CHNGD_Q; see

0x9C Bit 4 of user sub map to determine

whether interrupt is issued for a

change in detected data or for when

data is detected regardless of content

0

CGMS/WSS data is not changed/

not available

1

CGMS/WSS data is changed/available

Reserved

x

VDP_GS_VPS_PDC_UTC_CHNG_Q;

see 0x9C Bit 5 of User Sub Map to deter-

mine whether interrupt is issued for a

change in detected data or for when

data is detected regardless of content

0

Gemstar/PDC/VPS/UTC data is not

changed/not available

1

Gemstar/PDC/VPS/UTC data is

changed/available

Reserved

x

VDP_VITC_Q

0

VITC data is not available in the VDP

1

VITC data is available in the VDP

Reserved

x

相关PDF资料 |

PDF描述 |

|---|---|

| ADV7186BBCZ | IC VIDEO DECODER 196CSPBGA |

| ADV7441ABSTZ-5P | IC DECODER DIGITIZER 144LQFP |

| ADV7513BSWZ | IC TX HDMI 165MHZ 64LQFP |

| ADV7520BCPZ-80 | IC XMITTER HDMI/DVI CEC 64LFCSP |

| ADV7520NKBBCZ-80 | IC XMITTER HDMI/DVI LP 76CSPBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADV7180WBCPZ-REEL | 功能描述:IC VIDEO DECODER SDTV 40LFCSP RoHS:是 类别:集成电路 (IC) >> 线性 - 视频处理 系列:- 产品变化通告:Product Discontinuation 07/Mar/2011 标准包装:3,000 系列:OMNITUNE™ 类型:调谐器 应用:移动电话,手机,视频显示器 安装类型:表面贴装 封装/外壳:65-WFBGA 供应商设备封装:PG-WFSGA-65 包装:带卷 (TR) 其它名称:SP000365064 |

| ADV7180WBST48Z | 制造商:Analog Devices 功能描述: |

| ADV7180WBST48Z-RL | 功能描述:视频 IC 10-bit 4x Oversampling SDTV Decoder RoHS:否 制造商:Fairchild Semiconductor 工作电源电压:5 V 电源电流:80 mA 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-28 封装:Reel |

| ADV7180WBSTZ | 功能描述:视频 IC 10-bit 4x Oversampling SDTV Decoder RoHS:否 制造商:Fairchild Semiconductor 工作电源电压:5 V 电源电流:80 mA 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-28 封装:Reel |

| ADV7180WBSTZ-REEL | 功能描述:视频 IC 10-bit 4x Oversampling SDTV Decoder RoHS:否 制造商:Fairchild Semiconductor 工作电源电压:5 V 电源电流:80 mA 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-28 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。