参数资料

| 型号: | ADV7180WBCPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 91/116页 |

| 文件大小: | 0K |

| 描述: | IC VIDEO DECODER SDTV 40LFCSP |

| 标准包装: | 1 |

| 类型: | 视频解码器 |

| 应用: | 数码相机,手机,便携式视频 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 40-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 40-LFCSP-VQ(6x6) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页当前第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页

ADV7180

Data Sheet

Rev. I | Page 76 of 116

PIXEL PORT CONFIGURATION

The ADV7180 has a very flexible pixel port that can be configured

in a variety of formats to accommodate downstream ICs.

Table 100, Table 101, and Table 102 summarize the various

functions that the ADV7180 pins can have in different modes of

operation.

The ordering of components, for example, Cr vs. Cb for

Channel A, Channel B, and Channel C can be changed. See the

indicates the default positions for the Cr/Cb components.

OF_SEL[3:0], Output Format Selection, Address 0x03[5:2]

The modes in which the ADV7180 pixel port can be configured

are under the control of OF_SEL[3:0]. See Table 102 for details.

The default LLC frequency output on the LLC pin is approximately

27 MHz. For modes that operate with a nominal data rate of

13.5 MHz (0001, 0010), the clock frequency on the LLC pin stays

at the higher rate of 27 MHz. For information on outputting the

nominal 13.5 MHz clock on the LLC pin, see the

Address 0x8F[6:4] section.

SWPC, Swap Pixel Cr/Cb, Address 0x27[7]

This bit allows Cr and Cb samples to be swapped.

When SWPC is 0 (default), no swapping is allowed.

When SWPC is 1, the Cr and Cb values can be swapped.

LLC_PAD_SEL[2:0] LLC Output Selection,

Address 0x8F[6:4]

The following I2C write allows the user to select between LLC

(nominally at 27 MHz) and LLC (nominally at 13.5 MHz).

The LLC signal is useful for LLC-compatible wide bus (16-bit)

output modes. See the OF_SEL[3:0], Output Format Selection,

Address 0x03[5:2] section for additional information. The LLC

signal and data on the data bus are synchronized. By default, the

rising edge of LLC/LLC is aligned with the Y data; the falling

edge occurs when the data bus holds C data. The polarity of the

clock, and therefore the Y/C assignments to the clock edges, can

be altered by using the polarity LLC pin.

When LLC_PAD_SEL is 000, the output is nominally 27 MHz

LLC on the LLC pin (default).

When LLC_PAD_SEL is 101, the output is nominally 13.5 MHz

LLC on the LLC pin.

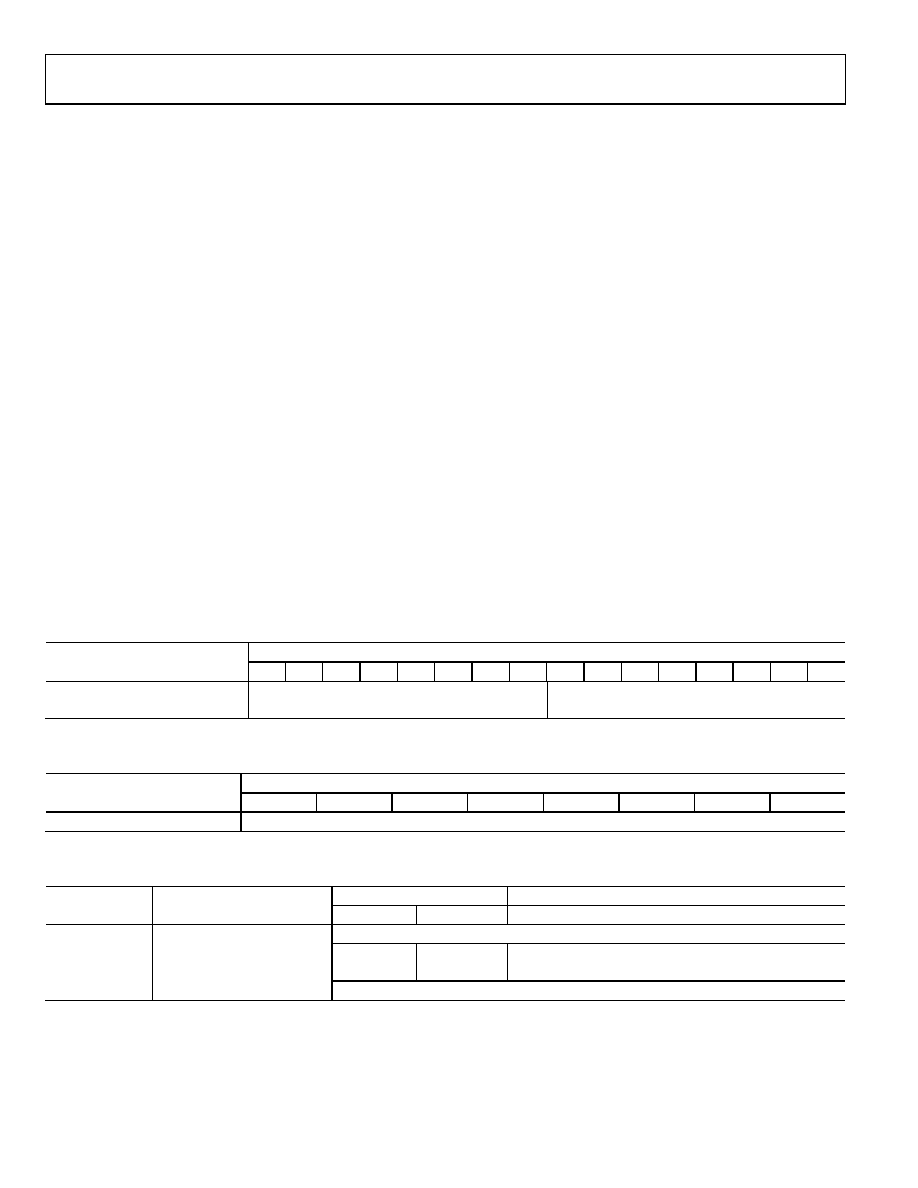

Table 100. 64-Lead LQFP P15 to P0 Output/Input Pin Mapping

Data Port Pins P[15:0]

Format and Mode

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Video Out, 8-Bit, 4:2:2

YCrCb[7:0]OUT

Video Out, 16-Bit, 4:2:2

Y[7:0]OUT

CrCb[7:0]OUT

Table 101. 48-Lead, 40-Lead, and 32-Lead Devices P7 to P0 Output/Input Pin Mapping

Data Port Pins P[7:0]

Format and Mode

7

6

5

4

3

2

1

0

Video Out, 8-Bit, 4:2:2

YCrCb[7:0]OUT

Table 102. ADV7180 Standard Definition Pixel Port Modes

64-Lead LQFP P[15:0]

48-Lead LQFP, 40-Lead LFCSP, or 32-Lead LFCSP

OF_SEL[3:0]

Format

P[15:8]

P[7:0]

0000 to 0001

Reserved

Reserved, do not use

0010

16-bit at LLC 4:2:2

Y[7:0]

CrCb[7:0]

Not valid

0011 (default)

8-bit at LLC 4:2:2 (default)

YCrCb[7:0]

Three-state

YCrCb[7:0]

0100 to 1111

Reserved

Reserved, do not use

相关PDF资料 |

PDF描述 |

|---|---|

| ADV7186BBCZ | IC VIDEO DECODER 196CSPBGA |

| ADV7441ABSTZ-5P | IC DECODER DIGITIZER 144LQFP |

| ADV7513BSWZ | IC TX HDMI 165MHZ 64LQFP |

| ADV7520BCPZ-80 | IC XMITTER HDMI/DVI CEC 64LFCSP |

| ADV7520NKBBCZ-80 | IC XMITTER HDMI/DVI LP 76CSPBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADV7180WBCPZ-REEL | 功能描述:IC VIDEO DECODER SDTV 40LFCSP RoHS:是 类别:集成电路 (IC) >> 线性 - 视频处理 系列:- 产品变化通告:Product Discontinuation 07/Mar/2011 标准包装:3,000 系列:OMNITUNE™ 类型:调谐器 应用:移动电话,手机,视频显示器 安装类型:表面贴装 封装/外壳:65-WFBGA 供应商设备封装:PG-WFSGA-65 包装:带卷 (TR) 其它名称:SP000365064 |

| ADV7180WBST48Z | 制造商:Analog Devices 功能描述: |

| ADV7180WBST48Z-RL | 功能描述:视频 IC 10-bit 4x Oversampling SDTV Decoder RoHS:否 制造商:Fairchild Semiconductor 工作电源电压:5 V 电源电流:80 mA 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-28 封装:Reel |

| ADV7180WBSTZ | 功能描述:视频 IC 10-bit 4x Oversampling SDTV Decoder RoHS:否 制造商:Fairchild Semiconductor 工作电源电压:5 V 电源电流:80 mA 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-28 封装:Reel |

| ADV7180WBSTZ-REEL | 功能描述:视频 IC 10-bit 4x Oversampling SDTV Decoder RoHS:否 制造商:Fairchild Semiconductor 工作电源电压:5 V 电源电流:80 mA 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-28 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。