- 您现在的位置:买卖IC网 > PDF目录294983 > AGLN010V5-UC36 FPGA, 260 CLBS, 10000 GATES, 250 MHz, PBGA36 PDF资料下载

参数资料

| 型号: | AGLN010V5-UC36 |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 260 CLBS, 10000 GATES, 250 MHz, PBGA36 |

| 封装: | 4 X 4 MM, 0.8 MM HEIGHT, 0.4 MM PITCH, UC-36 |

| 文件页数: | 40/140页 |

| 文件大小: | 4325K |

| 代理商: | AGLN010V5-UC36 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页当前第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页

Datasheet Information

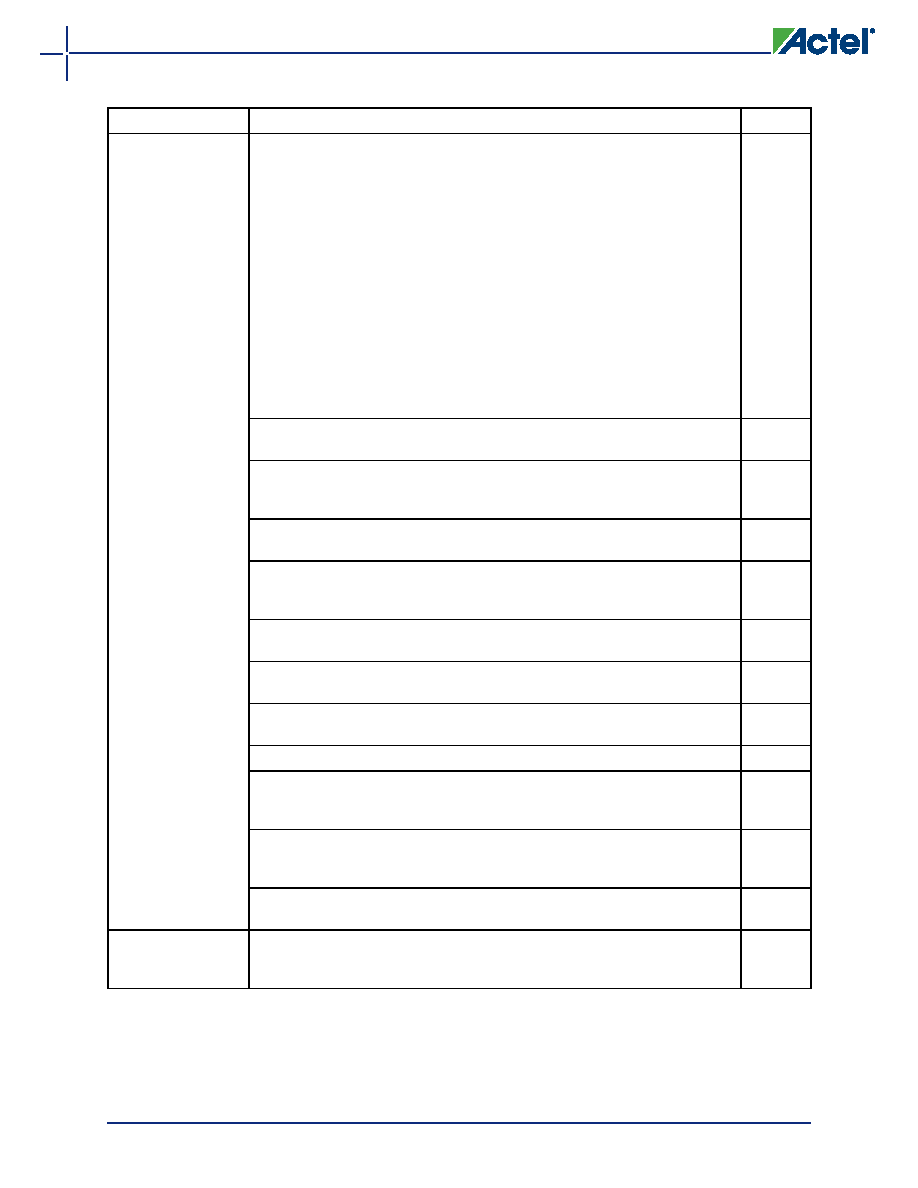

4- 2

R ev isio n 1 0

Revision 10

(continued)

The following tables were updated with current available information. The

equivalent software default drive strength option was added.

Timing tables in the "Single-Ended I/O Characteristics" section, including new

tables for 3.3 V and 1.2 V LVCMOS wide range.

through

The formulas in the notes to Table 2-29 I/O Weak Pull-Up/Pull-Down

Resistances were revised (SAR 21348).

The text introducing Table 2-31 Duration of Short Circuit Event before Failure

was revised to state six months at 100° instead of three months at 110° for

reliability concerns. The row for 110° was removed from the table.

The following sentence was deleted from the "2.5 V LVCMOS" section (SAR

24916): "It uses a 5-V tolerant input buffer and push-pull output buffer."

Specifications" section (SAR 23919). A note was added stating that DDR is not

supported for AGLN010, AGLN015, and AGLN020.

Tables in the "Global Tree Timing Characteristics" section were updated with new

information available.

nano CCC/PLL Specification were revised (SAR 79390).

Tables in the SRAM "Timing Characteristics" section and FIFO "Timing

Characteristics" section were updated with new information available.

A note was added to the "81-Pin CS" pin tables for AGLN060, AGLN060Z,

AGLN125, AGLN125Z, AGLN250, and AGLN250Z indicating that pins F1 and F2

must be grounded (SAR 25007).

through

A note was added to the "81-Pin CS" and "100-Pin VQFP" pin tables for

AGLN060 and AGLN060Z stating that bus hold is not available for pin H7 or pin

45 (SAR 24079).

The AGLN250 function for pin C8 in the "81-Pin CS" table was revised (SAR

22134).

Revision 9

(March 2010)

All product tables and pin tables were updated to show clearly that AGLN030 is

available only in the Z feature grade at this time. The nano-Z feature grade

devices are designated with a Z at the end of the part number.

N/A

Revision

Changes

Page

相关PDF资料 |

PDF描述 |

|---|---|

| AGLP125V2-CS281I | FPGA, 3120 CLBS, 125000 GATES, PBGA281 |

| AGLP125V2-CS281 | FPGA, 3120 CLBS, 125000 GATES, PBGA281 |

| AGLP125V2-CS289I | FPGA, 3120 CLBS, 125000 GATES, PBGA289 |

| AGLP125V2-CS289 | FPGA, 3120 CLBS, 125000 GATES, PBGA289 |

| AGLP125V2-CSG281I | FPGA, 3120 CLBS, 125000 GATES, PBGA281 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AGLN010V5-UCG36 | 功能描述:IC FPGA 10K 1.5V UCG36 RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:IGLOO nano 标准包装:60 系列:XP LAB/CLB数:- 逻辑元件/单元数:10000 RAM 位总计:221184 输入/输出数:244 门数:- 电源电压:1.71 V ~ 3.465 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:388-BBGA 供应商设备封装:388-FPBGA(23x23) 其它名称:220-1241 |

| AGLN010V5-UCG36I | 功能描述:IC FPGA NANO 1KB 10K 36-UCSP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:IGLOO nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| AGLN015V2-QNG68 | 功能描述:IC FPGA NANO 1KB 15K 68-QFN RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:IGLOO nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| AGLN015V2-QNG68I | 功能描述:IC FPGA NANO 1KB 15K 68-QFN RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:IGLOO nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| AGLN015V5-QNG68 | 功能描述:IC FPGA NANO 1KB 15K 68-QFN RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:IGLOO nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

发布紧急采购,3分钟左右您将得到回复。