- 您现在的位置:买卖IC网 > PDF目录256054 > BU-65843F3-200 (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 PDF资料下载

参数资料

| 型号: | BU-65843F3-200 |

| 厂商: | DATA DEVICE CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 |

| 封装: | 0.880 INCH, CERAMIC, QFP-80 |

| 文件页数: | 36/75页 |

| 文件大小: | 532K |

| 代理商: | BU-65843F3-200 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页当前第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页

41

Data Device Corporation

www.ddc-web.com

BU-65743/65843/65863/65864

D-06/04-0

The PCI Mini-ACE Mark3/Micro-ACE TE supports all the inter-

rupt events from ACE/Mini-ACE (Plus) and Enhanced Mini-ACE

including RAM Parity Error, Transmitter Timeout, BC/RT

Command Stack Rollover, MT Command Stack and Data Stack

Rollover, Handshake Error, BC Retry, RT Address Parity Error,

Time Tag Rollover, RT Circular Buffer Rollover, BC Message, RT

Subaddress, BC End-of-Frame, Format Error, BC Status Set, RT

Mode Code, MT Trigger, and End-of-Message.

For the PCI Mini-ACE Mark3/Micro-ACE TE's Enhanced BC

mode, there are four user-defined interrupt bits. The BC

Message Sequence Control Engine includes an instruction

enabling it to issue these interrupts at any time.

For RT and Monitor modes, the PCI Mini-ACE Mark3/Micro-ACE

TE architecture includes an Interrupt Status Queue. This pro-

vides a mechanism for logging messages that result in interrupt

requests. Entries to the Interrupt Status Queue may be filtered

such that only valid and/or invalid messages will result in entries

on the queue.

The PCI Mini-ACE Mark3/Micro-ACE TE incorporates additional

interrupt conditions beyond ACE/Mini-ACE (Plus), based on the

addition of Interrupt Mask Register #2 and Interrupt Status

Register #2. This is accomplished by chaining the two Interrupt

Status Registers using the INTERRUPT CHAIN BIT (bit 0) in

Interrupt Status Register #2 to indicate that an interrupt has

occurred in Interrupt Status Register #1. Additional interrupts

include "Self-Test Completed", masking bits for the Enhanced

BC Control Interrupts, 50% Rollover interrupts for RT Command

Stack, RT Circular Buffers, MT Command Stack, and MT Data

Stack; BC Op Code Parity Error, (RT) Illegal Command, (BC)

General Purpose Queue or (RT/MT) Interrupt Status Queue

Rollover, Call Stack Pointer Register Error, BC Trap Op Code,

and four User-Defined interrupts for the Enhanced BC mode.

RAM PARITY

The BC/RT/MT version of the PCI Mini-ACE Mark3/Micro-ACE

TE is available with options of 4K or 64K words of internal RAM.

For the 64K option, the RAM is 17 bits wide. The 64K X 17 inter-

nal RAM allows for parity generation for RAM write accesses,

and parity checking for RAM read accesses. When the PCI Mini-

ACE Mark3/Micro-ACE TE detects a RAM parity error, it reports

it to the host processor by means of an interrupt and a register

bit. Also, for the RT and Selective Message Monitor modes, the

RAM address(es) where a parity error(s) was detected will be

stored on the Interrupt Status Queue (if enabled).

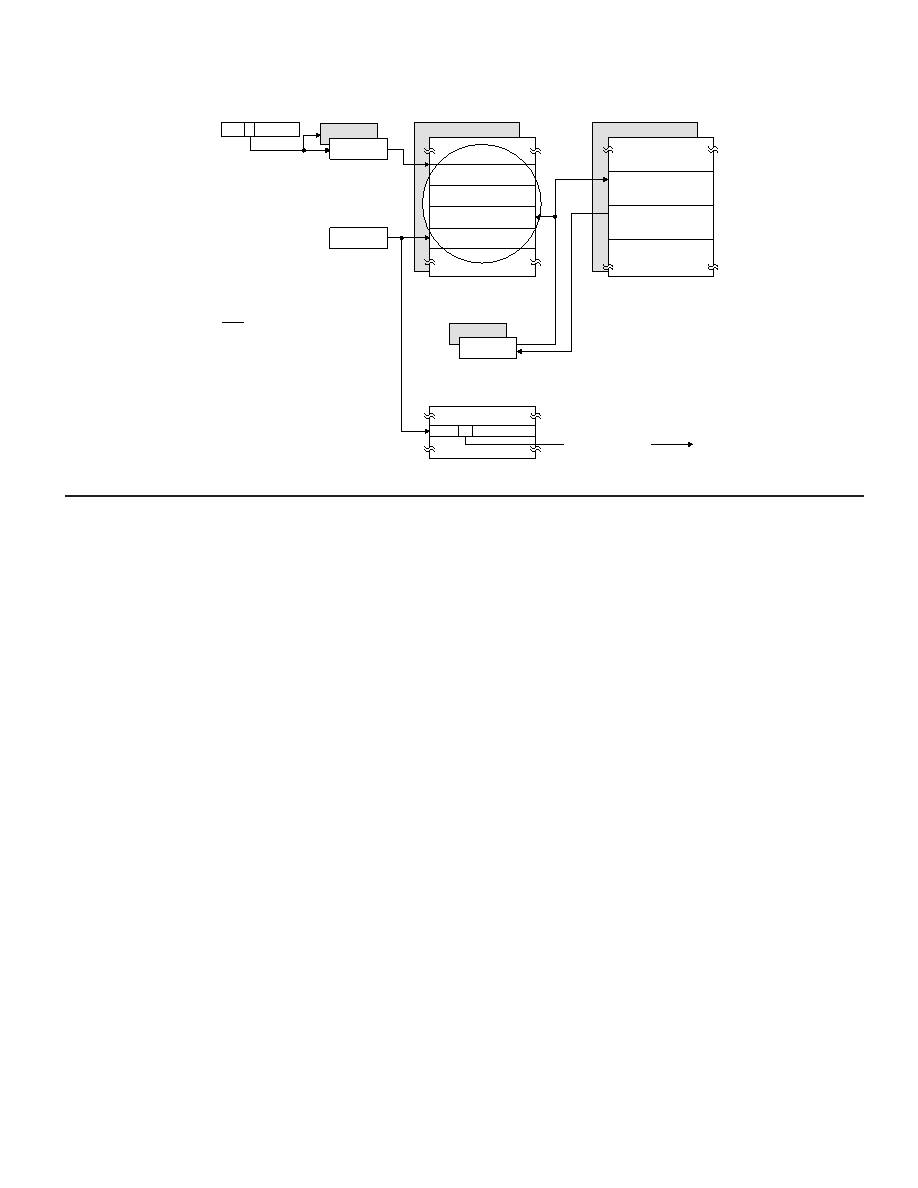

FIGURE 11 illustrates a generic connection diagram between a

PCI "Initiator" and a PCI Mini-ACE Mark3/Micro-ACE TE

"Target."

The following timing diagrams illustrate the PCI commands that

the PCI Mini-ACE Mark3/Micro-ACE TE responds to. Note that

these diagrams are meant to show the basic PCI bus operation

of the PCI Mini-ACE Mark3/Micro-ACE TE itself and do not show

masters inserting wait states, masters burst reading or writing

past address boundaries, masters writing into a full FIFO, etc.

To help understand the following timing diagrams an explanation

of the basic architecture of the PCI Mini-ACE Mark3/Micro-ACE

TE is helpful. The PCI Mini-ACE Mark3/Micro-ACE TE can be

thought of as the very successful mini-ACE terminal family inte-

grated with a 3.3V 33MHz PCI target interface. To simplify

descriptions of the PCI Mini-ACE Mark3/Micro-ACE TE architec-

ture, the term ACE will be used as a substitute for "enhanced

15

13

0

BLOCK STATUS WORD

TIME TAG WORD

DATA BLOCK POINTER

RECEIVED COMMAND

WORD

CONFIGURATION

REGISTER #1

MONITOR COMMAND

STACK POINTERS

MONITOR

COMMAND STACKS

CURRENT

AREA B/A

MONITOR DATA

STACKS

MONITOR DATA

BLOCK #N + 1

MONITOR DATA

BLOCK #N

CURRENT

COMMAND WORD

MONITOR DATA

STACK POINTERS

IF THIS BIT IS "0" (NOT SELECTED)

NO WORDS ARE STORED IN EITHER

THE COMMAND STACK OR DATA STACK.

IN ADDITION, THE COMMAND AND DATA

STACK POINTERS WILL NOT BE UPDATED.

NOTE

SELECTIVE MONITOR

LOOKUP TABLES

SELECTIVE MONITOR

ENABLE

(SEE NOTE)

OFFSET BASED ON

RTA4-RTA0, T/R, SA4

FIGURE 10. SELECTIVE MESSAGE MONITOR MEMORY MANAGEMENT

相关PDF资料 |

PDF描述 |

|---|---|

| BU-65863F8-310 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 |

| BU-61559D1-330L | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| BU-61559D1-380L | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| BU-61559D1-530W | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| BU-61559D1-560 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BU-65-9 | 功能描述:测试电夹 HEAVY DUTY LARGE JAW GATOR CLIP WHITE RoHS:否 制造商:Pomona Electronics 类型:Minigrabber clip 颜色:Black |

| BU6650NUX | 制造商:ROHM 制造商全称:Rohm 功能描述:3ch CMOS LDO Regulators |

| BU6650NUX_11 | 制造商:ROHM 制造商全称:Rohm 功能描述:3ch CMOS LDO Regulators |

| BU6650NUX-TR | 功能描述:低压差稳压器 - LDO LDO REG 0.2A 8PIN 2.8V 2.8V 1.8V RoHS:否 制造商:Texas Instruments 最大输入电压:36 V 输出电压:1.4 V to 20.5 V 回动电压(最大值):307 mV 输出电流:1 A 负载调节:0.3 % 输出端数量: 输出类型:Fixed 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-20 |

| BU6651NUX | 制造商:ROHM 制造商全称:Rohm 功能描述:High-speed Load Response Full CMOS LDP Regulators |

发布紧急采购,3分钟左右您将得到回复。